# MULTI-DOMAIN MODELING THROUGH SPECIFICATION OF A DOMAIN SPECIFIC MODELING LANGUAGE FOR CYBER-PHYSICAL SYSTEMS DEVELOPMENT

By

Alexander L. Mendes

Thesis

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

MASTER OF SCIENCE in

**ELECTRICAL ENGINEERING**

August, 2013

Nashville, Tennessee

Approved:

Theodore A. Bapty, Ph.D

Joseph E. Porter, Ph.D

## **DEDICATION**

To my loving parents, Mary Ellen and Lloyd, for their unfaltering encouragement and all of their imparted wisdom. I would never have been able to achieve all that I have without their continued love and support.

To my beloved Avery, for her years of steadfast patience and comforting support. Your belief in me kept me on my feet even through the toughest times, and saw me through to the finish.

## **ACKNOWLEDGMENTS**

I am truly indebted and grateful to my advisor Dr. Theodore Bapty, who gave me the instruction and support I required throughout my thesis writing. It would have been next to impossible to write this thesis without the help and guidance of Dr. Joseph Porter, who helped me in selecting the right research methodologies. Dr. Porter's expertise and invaluable teachings allowed my ideas to flourish, and will not be forgotten as I embrace the challenges that lay ahead.

# TABLE OF CONTENTS

|    |                |                |                                            | Page |

|----|----------------|----------------|--------------------------------------------|------|

| DE | EDIC           | ATION          |                                            | i    |

| AC | CKNO           | OWLED          | GMENTS                                     | ii   |

| LI | LIST OF TABLES |                |                                            |      |

| LI | ST O           | F FIGU         | RES                                        | vi   |

| Ι  | Int            | roductio       | n                                          | 1    |

|    | I.1            |                | ation and Problem                          |      |

|    |                | I.1.1          | Cyber-Physical Systems                     |      |

|    |                | I.1.2          | Dynamic Simulations                        |      |

|    |                | I.1.3<br>I.1.4 | Software Modeling                          |      |

|    | I.2            |                | Model-Integrated Computing (MIC)           |      |

|    | 1.2            | 1.2.1          | ach                                        |      |

|    |                | I.2.1<br>I.2.2 | Solution Summary                           |      |

|    |                | I.2.3          | Related Works                              |      |

| II | Ba             | ckgroun        | d                                          | 13   |

|    | II.1           | Cyber          | Physical Systems                           | 13   |

|    | 11.1           | II.1.1         | Synchronous Reactive Systems               |      |

|    |                | II.1.2         | Discrete-Event Systems                     |      |

|    |                | II.1.3         | Continuous-Time Systems                    |      |

|    | II.2           | Dynar          | nics Simulations                           |      |

|    |                | II.2.1         | Modelica                                   |      |

|    |                | II.2.2         | Simulink                                   | 22   |

|    |                | II.2.3         | Software Modeling                          |      |

|    |                | II.2.4         | Modeling within Simulink                   | 24   |

|    |                | II.2.5         | Embedded Systems Modeling Language (ESMoL) | 25   |

|    | II.3           | Mode           | -Integrated Computing                      | 29   |

|    |                | II.3.1         | Metamodeling                               | 30   |

|    |                | II.3.2         | GME                                        |      |

|    |                | II.3.3         | The Signal Flow DSML                       | 36   |

| III | Bid   | lirection | al DC/DC Converter                            | . 41  |

|-----|-------|-----------|-----------------------------------------------|-------|

|     | III.1 | Conve     | rter Overview                                 | . 41  |

|     |       | III.1.1   | Converter Purpose                             | . 41  |

|     |       | III.1.2   | How the Converter Works                       | . 44  |

|     |       | III.1.3   | Ideal Bidirectional DC/DC Converter Circuit   | . 51  |

|     | III.2 | Bidirec   | ctional DC/DC Converter Equations             | . 55  |

|     |       | III.2.1   | Volt-Second Balance and Amp-Second balance    | . 56  |

|     |       | III.2.2   | Boost Mode Equations                          |       |

|     |       | III.2.3   | DCM in Boost Operation                        |       |

|     |       | III.2.4   | Buck Mode Equations                           |       |

|     |       | III.2.5   | DCM in Buck Mode                              |       |

|     | III.3 | Model     | Synthesis                                     | . 85  |

|     |       | III.3.1   | Dynamic Circuit Composition                   |       |

|     |       | III.3.2   | Dataflow Composition                          | . 90  |

|     |       | III.3.3   | GME Composition                               |       |

| IV  | Eva   | aluation  |                                               | . 99  |

|     | IV.1  | Testbe    | nch Composition                               | . 99  |

|     | IV.2  |           | ation Evaluation                              |       |

|     |       | IV.2.1    | Float-charge transition to hybrid-drive       |       |

|     |       | IV.2.2    | Hybrid-drive transition to load drop-off      |       |

|     |       | IV.2.3    | Battery charging transition to float charging |       |

|     |       | IV.2.4    | Hybrid drive transition to battery-only drive |       |

|     |       | IV.2.5    | Battery-only drive transition to hybrid-drive |       |

|     |       | IV.2.6    | Hybrid-drive transition to battery charging   |       |

|     | IV.3  | Simula    | ation Results                                 |       |

| V   | Co    | nclusion  | • • • • • • • • • • • • • • • • • • • •       | . 117 |

| ΒI  | BI 14 | CD A DI   | HV                                            | 120   |

# LIST OF TABLES

| Table |                                                                       | Page  |

|-------|-----------------------------------------------------------------------|-------|

| IV.1  | Voltage response of the DC/DC converter during operating mode transi- |       |

|       | tions                                                                 | . 114 |

# LIST OF FIGURES

| Figure |                                                                                                                                                                        | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

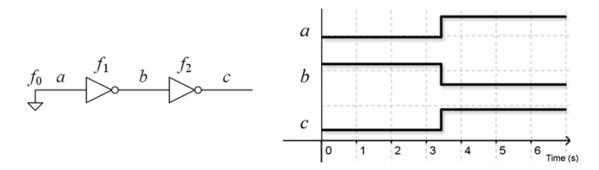

| II.1   | (a) On the left we have an example SR system. (b) The traces of these NOT blocks in response to a change at time = 3.45s                                               | . 14 |

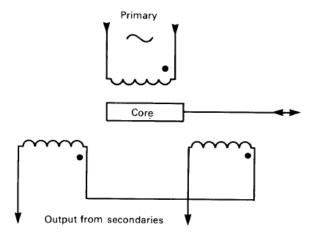

| II.2   | Circuit layout for a Linear Variable Differential Transformer Displacement Transducer                                                                                  | . 19 |

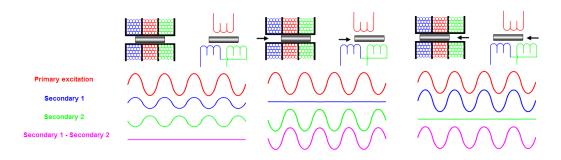

| II.3   | Behavior of an LVDT across 3 different operating conditions                                                                                                            | . 20 |

| II.4   | Example of a mixed domain model in Modelica                                                                                                                            | . 21 |

| II.5   | Example of a Simulink control loop                                                                                                                                     | . 23 |

| II.6   | Example of a Simulink control loop                                                                                                                                     | . 25 |

| II.7   | ESMoL design phases                                                                                                                                                    | . 27 |

| II.8   | Relationship between semantics, synatx, and their respective mappings                                                                                                  | . 30 |

| II.9   | Relationship between semantics, syntax, and their respective mappings                                                                                                  | . 31 |

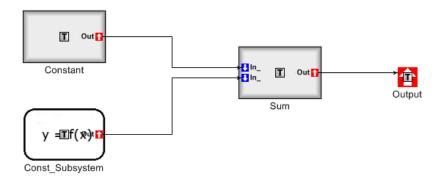

| II.10  | A simple Signal Flow subsystem containing the Sum and Constant primitives along with an additional subsystem                                                           | . 34 |

| II.11  | The DC/DC converter battery as a component assembly within GME                                                                                                         | . 35 |

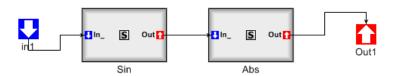

| II.12  | A simple Signal Flow were the input flows into a Sin block, and then into an Absolute value block                                                                      | . 37 |

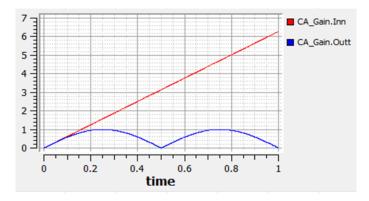

| II.13  | A simulation of the Sin-Abs Signal Flow system. The red input $x$ is pictured as a line, while the blue output $y$ is appears as the positive magnitude of a sinewave. |      |

| II.14  | Cheetah templates corresponding to the Rounding Signal Flow block on the left, and to the Sin Signal Flow block on the right.                                          | . 38 |

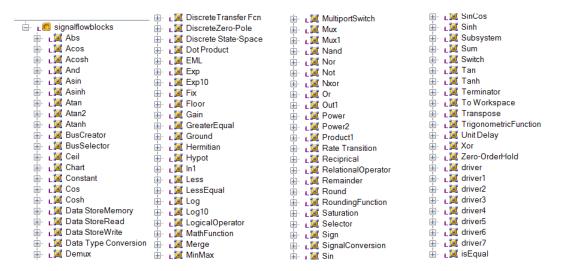

| II.15  | The library of currently supported Signal Flow blocks                                                                                                                  | . 39 |

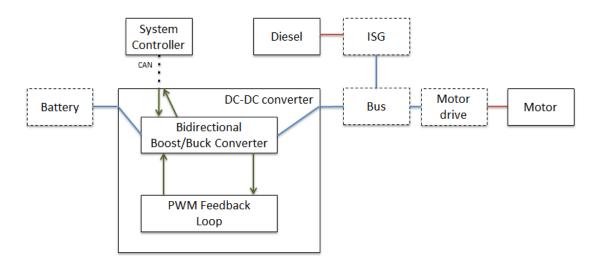

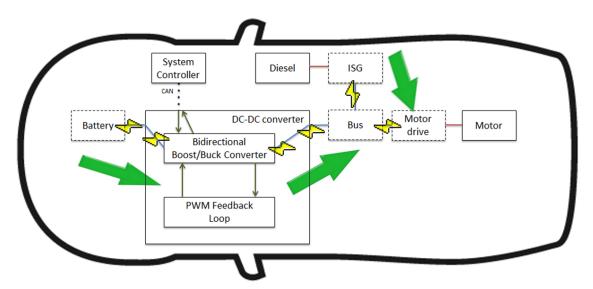

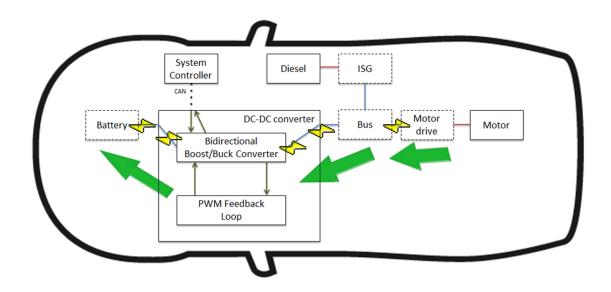

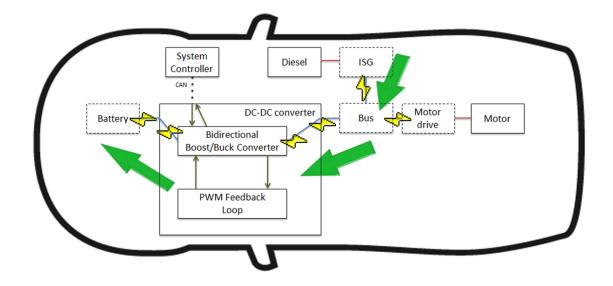

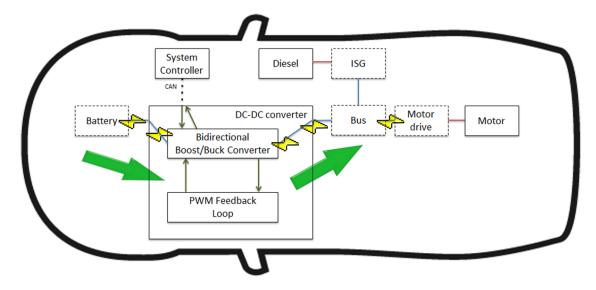

| III.1  | Series Hybrid-Electric Vehicle Architecture                                                                                                                            | . 41 |

| III.2  | The 5 Use Cases of Bidirectional DC/DC Converter Operation                                                                                                                                                                      | 44  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| III.3  | Power Flow during Hybrid operation and Load drop-off                                                                                                                                                                            | 45  |

| III.4  | Regenerative Braking Power Flow during Battery Charging and Charge Floating                                                                                                                                                     | 46  |

| III.5  | Diesel Generation Power Flow during Battery Charging                                                                                                                                                                            | 48  |

| III.6  | Power flow for Battery-Only Drive                                                                                                                                                                                               | 50  |

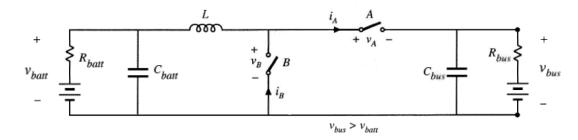

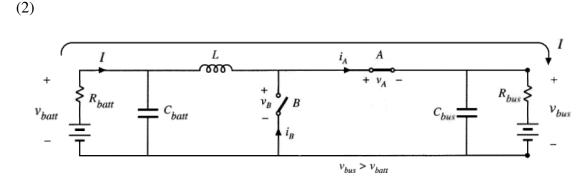

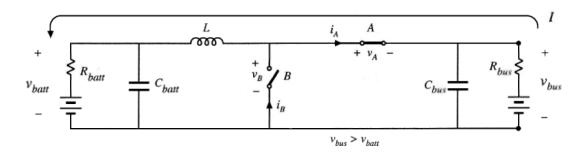

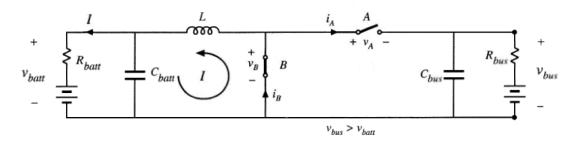

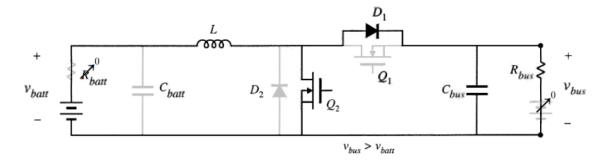

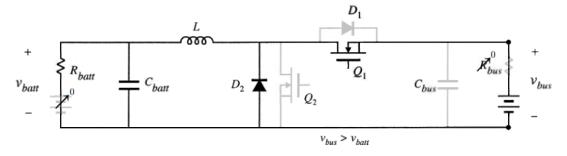

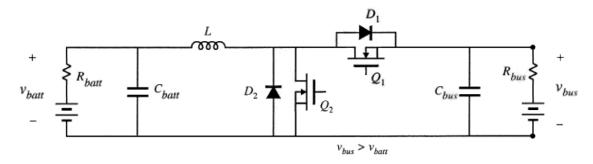

| III.7  | Realization of the DC/DC converter with ideal switches                                                                                                                                                                          | 51  |

| III.8  | Converter operation during boost mode: (1) Interval 1 where A is open, and current builds up in the inductor. (2) In Interval 2 A is closed and the inductor current drives the bus.                                            | 52  |

| III.9  | Buck mode converter operation: (1) Within Interval 1, $A$ is closed allowing current to build up in the inductor, and (2) in Interval 2, $A$ is open and the inductor drives the battery while isolated from the source voltage | 54  |

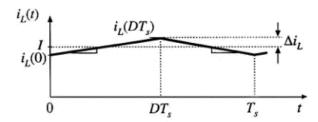

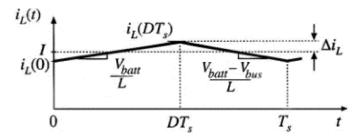

| III.10 | Inductor current waveform $(i_L(t))$ in a boost mode converter circuit. The current varies about the DC value, $I$ , by $\triangle i_L$                                                                                         | 56  |

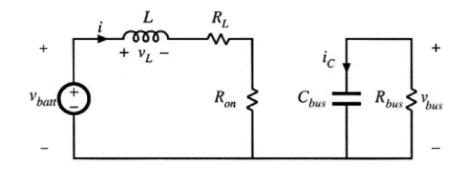

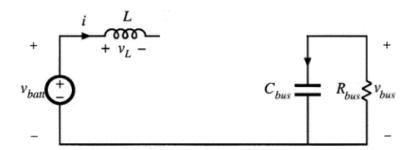

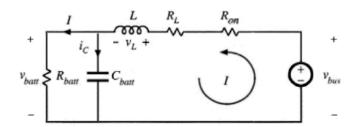

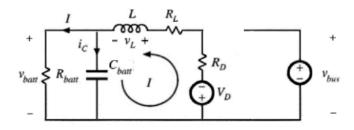

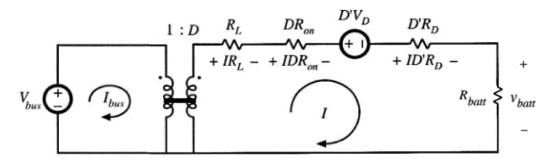

| III.11 | DC/DC converter boost mode equivalent circuit. Some superflous components are greyed out according to assumptions regarding the circuit topology                                                                                | 59  |

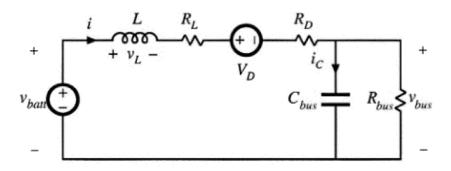

| III.12 | Boost mode equivalent circuit. (1) ON position during the first subinterval 2.) OFF position during the second subinterval                                                                                                      | 61  |

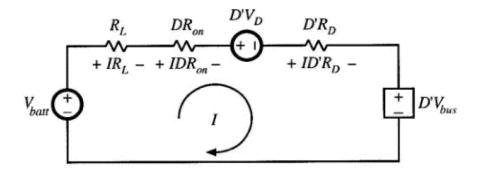

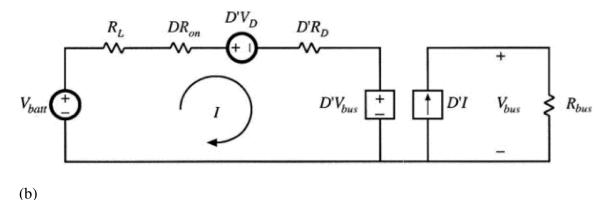

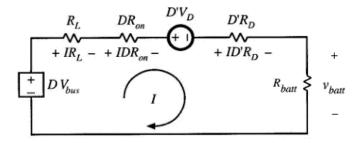

| III.13 | Equivalent circuit to Eq. (III.24)                                                                                                                                                                                              | 63  |

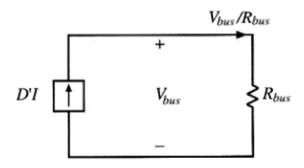

| III.14 | Equivalent circuit to Eq. (III.30)                                                                                                                                                                                              | 65  |

| III.15 | (a) The equivalent circuit models of Eqs. (III.30) and (III.24) aligned adjacently. (b) The dependent sources then are substituted with an ideal DC transformer.                                                                | 66  |

| III.16 | $i_L(t)$ in CCM where $\triangle i < I$                                                                                                                                                                                         | 68  |

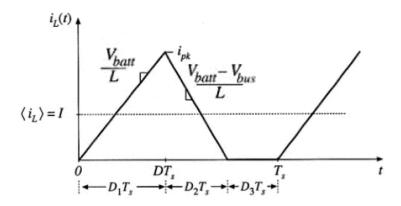

| III.17 | The DCM subinterval where $D1$ turns off while $Q1$ is OFF                                                                                                                                                                      | 71  |

| III.18 | A third subinterval $D_3$ arises while in DCM where $i_L(t) = 0$                                                                                                                                                                | 72. |

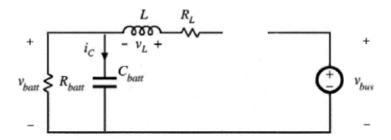

| 111.19 | mode equivalent circuit is achieved after performing circuit reudctions                                                                                      | 75 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| III.20 | Buck mode equivalent circuit (1) during the first subinterval, and (2) during the second subinterval                                                         | 77 |

| III.21 | Equivalent circuit to Eq. (III.79) governing buck mode operation                                                                                             | 78 |

| III.22 | Equivalent circuit to Eq. (III.83)                                                                                                                           | 78 |

| III.23 | Equations (III.79) and (III.83) are combined by realizing an ideal DC converter from the dependent sources                                                   | 79 |

| III.24 | The third subinterval of buck mode operation within DCM                                                                                                      | 82 |

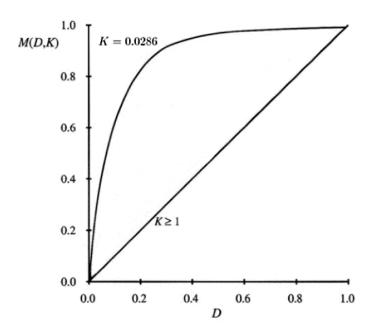

| III.25 | Plot of the conversion ratio vs. duty, where $K \ge 1$ (CCM), and $K = 0.0286$ (DCM)                                                                         | 85 |

| III.26 | Full bidirectional DC/DC converter model                                                                                                                     | 86 |

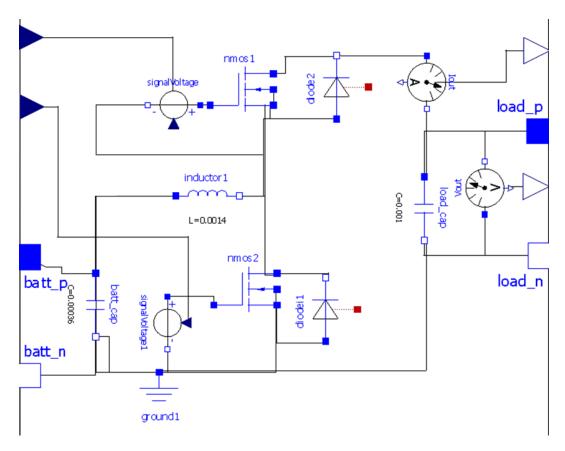

| III.27 | Full bidirectional DC/DC converter realization within Modelica                                                                                               | 87 |

| III.28 | The defining equation of the inductor component within Modelica                                                                                              | 88 |

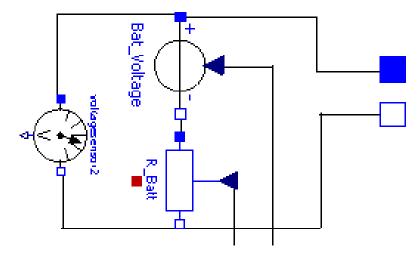

| III.29 | The battery component as defined within Modelica, consisting of a voltage source, a resistor, and a voltage sensor.                                          | 89 |

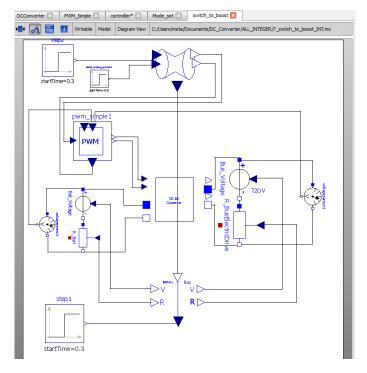

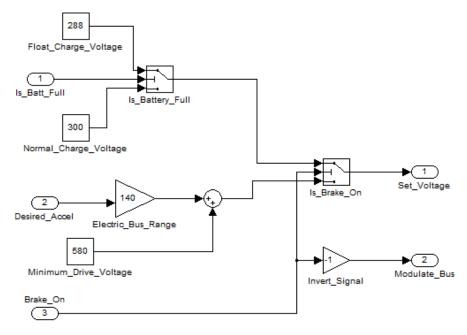

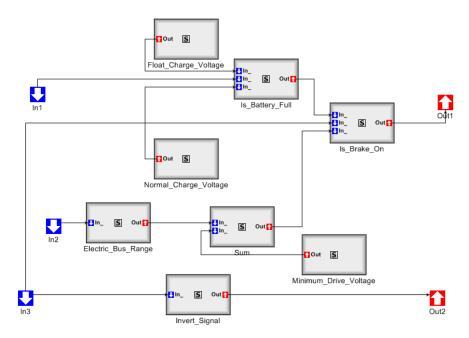

| III.30 | A possible Simulink configuration of the vehicle software controller                                                                                         | 91 |

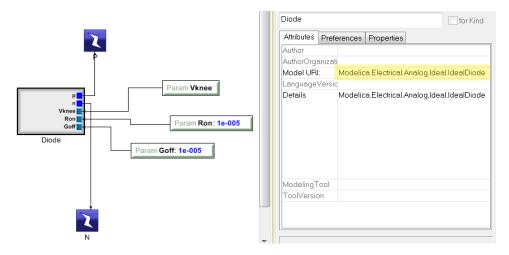

| III.31 | The diode Modelica component as embedded into a CyPhyML component. Two power ports and three parameter ports are exposed as interfaces.                      | 93 |

| III.32 | The vehicle system controller design realized from Signal Flow primitives within GME                                                                         | 94 |

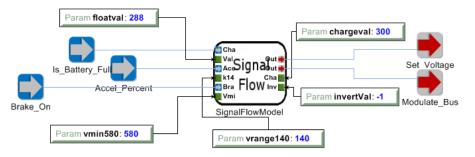

| III.33 | The Signal Flow controller embedded within a CyPhyML component. Numerous causal signal ports and parameter assignments function as component interfaces      | 95 |

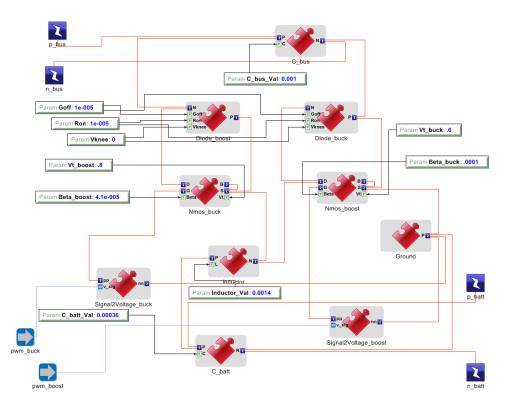

| III.34 | The converter circuit component assembly within GME. The circuit is composed of numerous CyPhyML components which contain embedded Modelica model references | 96 |

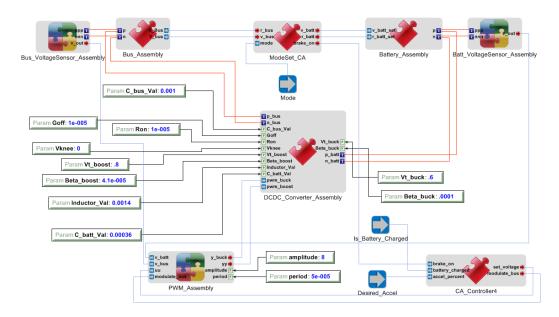

| III.35 | The top-level DC/DC converter component assembly within GME, incorporating the converter circuit, bus, battery, voltage sensors, mode-set, PWM, and vehicle software controller                                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

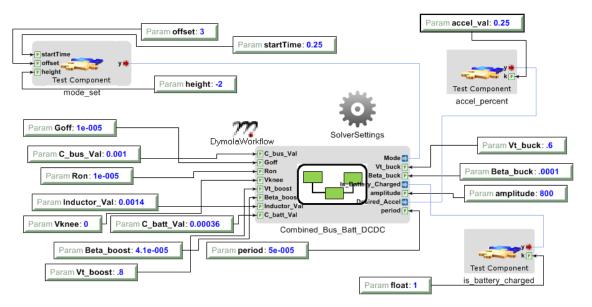

| IV.1   | The full DC/DC converter model instantiated within a testbench. The three test components provide external stimuli to the converter model throughout the simulation window. This testbench describes a transition from float charge operation to hybrid-drive                           |

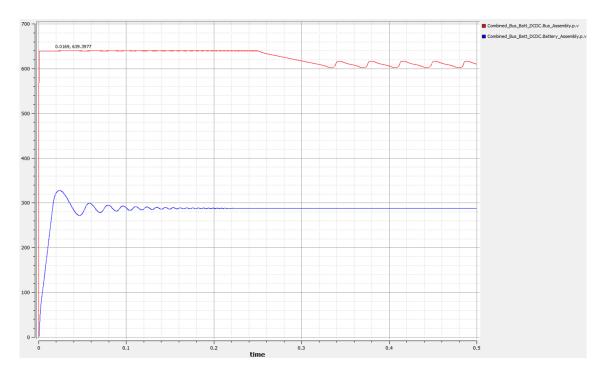

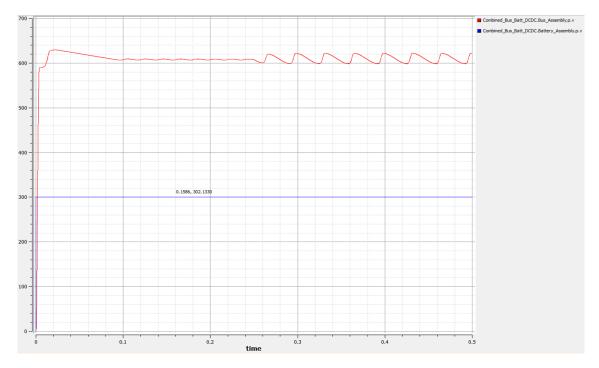

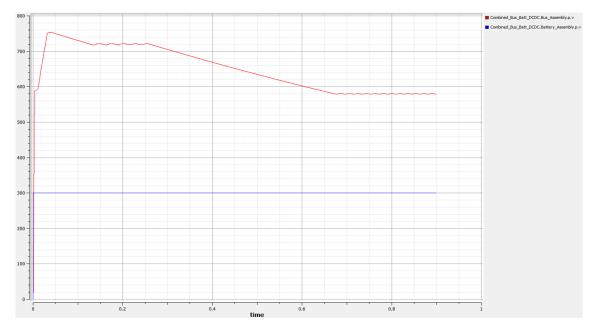

| IV.2   | Float-charge transition to hybrid-drive: Pictured is the voltage response of the bus (top/red), and battery (bottom/blue) during the dynamic simulation of this use case. This simulation corresponds to the testbench in Figure IV.1                                                   |

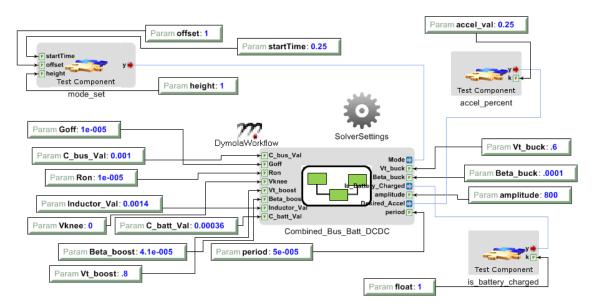

| IV.3   | Testbench of the full DC/DC converter model characterizing a mode transition between hybrid-drive transition and load drop-off. The transition is invoked by varying the Mode signal input at time = 0.25s, which commands a drop-off in bus load resistance                            |

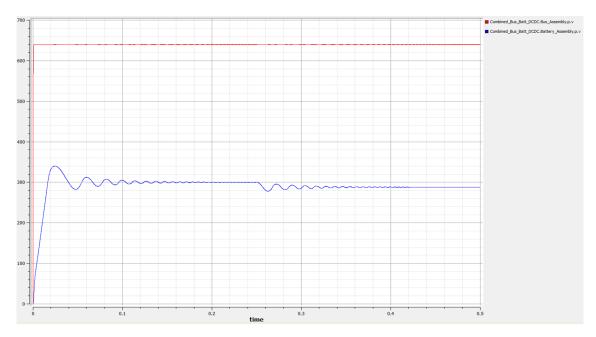

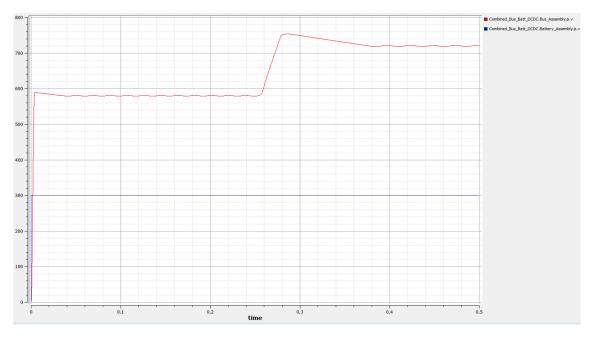

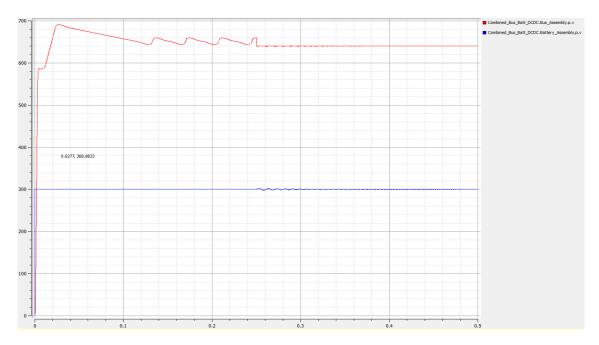

| IV.4   | Hybrid-drive transition to load drop-off: The bus and battery voltage response. This corresponds to the testbench in Figure IV.3. Varying the load alters the conversion ratio and steady-state ripple as visible in the second half of the simulation window                           |

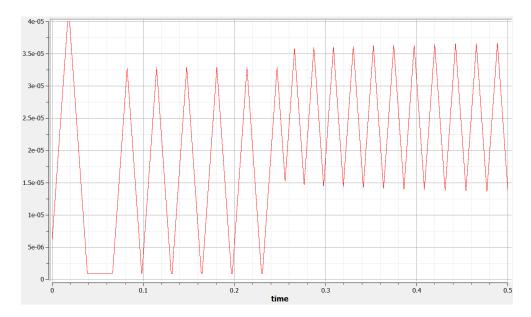

| IV.5   | Plot of PWM pulse width $(D*T_s)$ during a transition from hybrid-drive to load drop-off. A higher duty ratio is witnessed after the transition, even though the target voltage remains the same. The load drop-off causes a change in the converter's conversion ratio                 |

| IV.6   | Battery charging transition to float charging: Voltage response of the bus and battery. Once the controller detects a fully charged battery, a float charge is regulated across the battery to avoid overcharging 107                                                                   |

| IV.7   | Hybrid drive transition to battery-only drive: Plot of bus and battery voltage during this use case                                                                                                                                                                                     |

| IV.8   | Battery-only drive transition to hybrid-drive: plot of bus and battery voltage during this use case. This is the only simulation with a window larger than 0.5 seconds. An area for converter improvement is hastening this negative voltage adjustment during boost mode operation 109 |

| IV.9   | Hybrid-drive transition to battery charging: plot of bus and battery voltage.111                                                                                                                                                                                                        |

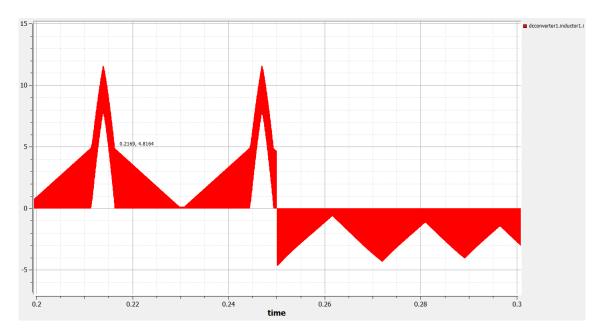

| IV.10 | Plot of inductor voltage during a hybrid-drive transition to battery charg- |

|-------|-----------------------------------------------------------------------------|

|       | ing. The current is positive during boost mode, and negative during buck    |

|       | mode. The circuit operates mostly in DCM, with brief periods of CCM         |

|       | operation during boost mode                                                 |

#### **CHAPTER I**

#### Introduction

Recent and continued advancements in the field of information technology have permitted more and more physical devices to become ingrained with computers. Such devices are called Embedded Systems, and the term encompasses the large number of computers whose job is not primarily information processing, but is instead interacting with processes of the physical world [12]. Embedded Systems—which are typically miniaturized and of specialized design—employ their computational power towards interacting with the physical environment to achieve some specialized purpose. Such systems are typically reactive to their environment which places elevated importance on their timing constraints. For many years designers have sought to develop these systems as efficiently, and inexpensively as possible by pursuing minimalistic designs, and thereby cutting the cost of unnecessary computational features [12].

Traditionally Embedded Systems design has been an industrial problem, and mostly a problem of resource limitations. To cope with the small memory, small data word sizes, and slow clocks of embedded processors, engineers have historically strived to write low level software, to avoid feature-rich operating systems, and to develop minimalistic, specialized architectures and networks [12]. Within this traditional industrial setting a typical, modern design process for Embedded Systems is as follows:

- 1. Write the embedded code

- 2. Build the embedded system

- 3. Test for correct timing and function

This process is highly inefficient and insufficient for the development of comprehensive systems. The unavoidable problem with this process is the inevitability that functional and

temporal constraints will not be met upon initial deployment. This would suggest an iterative design approach, meaning that the software engineers would have to go back to earlier phases of design and reconfigure the embedded code, component mapping, and hardware mapping. Then an entire redeployment of the embedded system would be necessary before the system could be tested for correctness again. For a vehicular system this iterative process of design, deployment, and verification can take years, and often requires several deployments before all requirements are met [22].

Poor understanding of design decisions and implementation details causes defects to surface during system deployment. These inconsistencies arise because designers must utilize multiple specialized tool suites that provide disparate representations of a system's computational behavior and physical dynamics. Software engineers must program by making educated guesses about the physical environment's reaction to the system's computational commands. Without a mathematical model to translate the software commands onto the reaction of the physical system, this process of trial-and-error and of lengthy design cycles is necessary so that the software engineers can slowly begin to understand how their device reacts once fully integrated and deployed in a non-ideal environment. This traditional design process does not lend itself to modularity, take for example the design of an electronic airbag: After the designers configure the inertial sensors—which trigger airbag inflation—for a particular vehicle, deploying this same airbag in a heavier vehicle would compromise the correctness of the system. The reality in designing these safety critical functions is that engineers typically tweak parameters and scheduling priorities in an iterative, ad hoc manner until the system tests correctly during deployment. A system designed using this process would be considered brittle, meaning that small changes in operating conditions or design would cause big changes in behavior [12]. Reconciling these changes may require complete reprogramming, rebuilding and recertification.

On the other hand, if we had a model to govern the physical processes of an airbag during crash, we could tweak the parameters of the vehicle in our model and then simulate how the system would react—all prior to deployment. The resulting design decisions would be founded in calculated physics rather than in trial-and-error. This moves the successive iterations inherent in the design process back into the early drafting phases, and away from the costly phases of componentization and deployment. Model-based design embraces the idea of evaluation and analysis starting from the beginning of the design process. A typical model-integrative design process is as follows:

- 1. Model the environment & dynamic behavior

- 2. Write the embedded code

- 3. Formally verify function and timing via simulation

- 4. Build the embedded system

The motivation behind this process is to drastically reduce the timelines for Cyber-Physical System deployment, by a factor of five [22]. From this academic viewpoint of system design, we see that extra effort is devoted towards accurately modeling the end-system, yet diverted away from time-intensive redeployments. The ability to formally verify the system through simulation is what allows us to move the building of the embedded system to later in the design process [4]. This design process is feasible because certain deployment-related phenomena appear during the extensive modeling process. With the knowledge gained from a model's simulations the final device can be built with more confidence, and with fewer deployments to achieve correctness of design as compared to the ad hoc approach.

This paper discusses model-integrating-computing (MIC) technology along with Cy-PhyML, a modeling language, and then presents a hybrid-engine controller application created using a specialized MIC toolchain. The paper concludes with an evaluation and a discussion of future research directions.

#### I.1 Motivation and Problem

#### I.1.1 Cyber-Physical Systems

Emerging from the abundance of interconnected embedded systems and their underlying networks is a new classification of devices, called Cyber-Physical Systems. These next generation systems are similar to Embedded Systems in that their primary focus is not solely information processing; however, the defining characteristic of Cyber-Physical Systems is that these systems maintain a tightly coupled relationship with their environment [12]. In this way, Embedded Systems comprise a topical subset of Cyber-Physical Systems with a stronger focus on real-time computational elements, as opposed to physical dynamics and cyber-physical interactions. Many Cyber-Physical systems are safety critical-such as fly-by-wire, adaptive cruise control, and nuclear engineering systems-and, therefore, must be able to react properly to physical conditions, even under fault circumstances. Because of their great potential, Cyber-Physical systems were classified by the National Science Foundations as a crucial area of emerging technology and research [27]. Like Embedded Systems, Cyber-Physical systems are fundamentally difficult to design and typically need to be deployed in order to test how the control software responds to the system's dynamics. For this reason, the design process for Cyber-Physical Systems is routinely iterative, and costly with many deployments.

#### I.1.2 Dynamic Simulations

It behooves the developers of Cyber-Physical Systems to employ dynamic simulations to test system behavior. Dynamic simulations allow analysis of the time evolution of a system due to the forces applied by the system's actuators [28]. In comparison, a static simulation would represent the solution to only the first timestep of a modeled system. The physical systems and engineering designs within a dynamic model are represented visually using block diagram notations [10]. Within the Modelica modeling language, the physical constraints imposed by the physical connections of the system are represented as signals which

provide interconnections between the ports of equation-based models and blocks. Characteristic of dynamic modeling languages like Modelica is the support of acausal power ports at component interfaces. A well-formed acausal model corresponds to a similarly well-formed system of dynamic equations [24]. Acausal ports can represent the complex relations between physical components because such ports are bidirectional and carry a two-fold definition of the power of a signal, known separately as effort and flow variables. This type of connection, unlike a functional one-way data flow, is well suited for expressing the physical constraints imposed by the interactions within a dynamic system. For example, an electrical power port shares the variables of voltage (effort) and current (flow) along its connections with other electrical components.

Once a model has been composed and checked for structural correctness, a dynamic modeling environment is able to translate the subsystems and connections within the model into equations which can be simulated and analyzed [24]. Simulations tools perform this task by consistently evaluating and updating the current state of a system starting from its initial state [5]. Typically a dynamic simulation is linked to the system's real-time control software. Within a model, the designer can create realistic use scenarios and then test the consequence of the proposed actions. With these capabilities, designers are able to validate and verify—with reasonable assurance—the behavior of their system in its intended environment, all before system deployment or even componentization [6], [5]. The knowledge feedback from dynamic simulations serves to replace the feedback gained from costly deployment cycles, and leads to faster development timelines.

There are some disadvantages posed by relying on simulation. For example, it can be expensive to measure exactly how one component affects another within a physical system in order to formulate an understanding of the system model. In this way, it takes time to create a system model that instead could have been devoted towards developing the actual system. However, our approach to system design advocates that the extra time spent to comprehend the intricacies of a system is invaluable in terms of the resulting ability to ver-

ify system properties prior to full implementation. With simulations, critical situations can be investigated without any risk or danger of faults. Furthermore, simulations can perform lengthy experiments which would be infeasible to test with a physical implementation, by leveraging a sped up notion of time,

#### I.1.3 Software Modeling

The computational aspects of Cyber-Physical Systems are governed by control loops and data flows, which could cause a system to behave differently depending on how the control elements are implemented within software and hardware. A control loop is the underlying process management scheme of a system that determines how a process variable is maintained at a set point, notwithstanding the destabilizing effect of external disturbances [9]. How this process is allocated within the confines of software architecture is termed the data flow: the abstract functions which passed control signals become instantiated as tasks which send messages between software components [10]. Furthermore, hardware allocation refers to how these software tasks are deployed onto a platform. Allocation details cover the mapping of tasks onto processing nodes, and messages to network interfaces. The entire process of mapping a control loop onto software, then onto hardware is called componentization. It is typically a costly and vaguely specified process that occurs prior to deployment [10].

To avoid the need of ad hoc componentization and deployment prior to system-level testing, system engineers have embraced the idea of software modeling. Software modeling supports educated project planning, allows detection of faults, and provides a rationale for refining code [30]. Most-importantly, as with dynamic simulation, software modeling allows the designers to evaluate and analyze system performance and timing. Software modeling tools, like the proposed ESMoL tool suite, facilitate the process of conforming a control-loop to proper software abstractions. Moreover, complex componentization concepts such as shared memory, partitioning, and distributed processors can be easily speci-

fied and simulated by mapping abstracted software components onto hardware platforms. Software simulation can be done with high assurance because tool suites allow the designers to specify crucial timing aspects such as clock speeds, worst case execution times, and network interface delays.

The described process for CPS design falls apart in practice due to inconsistencies across tool suites, which lead to ambiguous definitions of crucial design components. The resolution of ambiguous details between design domains and subsystems in a Cyber-Physical System is the main cause of failures during deployment and, therefore, project overruns [29]. Thus full system-level integration is not automatic or intuitive, and instead requires a specialized design solution for incorporating the signal-flow, software architecture, and hardware architecture aspects of system. In this sense, implementation becomes an extra design phase in which designers must painstakingly adjust integration details until the modeled behavior is exhibited in the integrated system.

# **I.1.4** Model-Integrated Computing (MIC)

In this paper we describe the META tool suite as well as its accompanying languages, which realize the broader Model-Integrated-Computing (MIC) approach to system design. MIC is emerging as a powerful and efficient means for designing, maintaining, and progressing large-scale computational systems such as Embedded Systems, and Cyber-Physical Systems. The MIC technique employs a model-based approach to system-level software development in which users are able to synthesize deployable program code from the formalized models of META's heterogeneous integration language, CyPhyML [3]. On top of capturing the requirements of the system, models in CyPhyML also explicitly capture details of the system's embedded software and environment in a multi-domain, heterogeneous manner [1]. No longer are models obscure or isolated representations of non-practical system behavior, but instead provide a reliable means for analyzing computational and dynamic behavior wherein model subcomponents correspond to real physical components.

The Model-Integrated approach reconciles the issue of incompatibility and ambiguity across specialized tool-suites by aggregating numerous aspects of system-level design together into a single unified semantics/representation [29]. This means that the crucial yet obscure implementation decisions no longer take place outside of the modeling framework in an ad-hoc fashion during manual deployment. The META approach permits the full integration of multi-domain, specialized models all within a single tool suite so that implementation details can then be carefully modeled, and done so within early phases of design. This capability shortens the iterative design cycle by allowing valuable integrationtime simulation analysis, verification, and validation to take place prior to the costly deployment phase [1]. To capitalize on the numerous models which already reside in existing engineering and analysis tools, CyPhyML allows the seamless-yet specialized-exchange of semantic definitions from popular tool suites like Simulink and Modelica [4]. This semantic exchange seeks to foster the adoption of these Model-Integrated techniques by system designers who are already proficient with the current-generation of design tools. The Model-Integrated-Computing approach permits full realization of the aggregate design goals sought by these current tools, to create a next-generation design suite capable of efficient and effective modeling and simulation of Cyber-Physical Systems.

## I.2 Approach

## **I.2.1** Integrated Dataflow Programming

In our attempt to model an electrical Cyber-Physical system, we require a modeling framework that will allow us to compose physical dynamical components alongside control flow components. ESMoL currently lacks a free and open language for representing synchronous control logic. The MIC approach does not warrant switching tool suites without model exchange, thus creating a similar model which is semantically unrelated. Therefore, we require a Domain Specific Modeling Language (DSML) integrated within CyPhyML to support the hybrid composition of control systems with attributes of physical dynamics.

With this said language, it would be possible to use discretely modeled software functions to enact change in continuously evolving continuous-time models, and vice versa. CPS are tightly coupled with their environment, and we need to be able to represent this tight coupling within our design suite so that we can fully embrace the MIC technique: If we are able to compose these different Models of Computation (MoC) together, then we will be able to test embedded CPS software with high assurance by being able to analyze, evaluate, and verify formal system properties from a heterogeneous simulation, without first deploying the system.

Since we desire flexibility and interoperability, such a DSML must be able to exchange models with other dataflow programming suites. Additionally since the ESMoL suite focuses on model-based deployment, atomic components should correspond to C code which can be easily componentized and executed on diverse hardware platforms. Through graph transformation techniques, this underlying C code would allow the system model to directly generate the specified system software. Behavior of the dataflow simulations should accurately match up with the eventual deployed behavior of the system.

#### **I.2.2** Solution Summary

Therefore, we propose the Signal Flow language and block library as a sublanguage of CyPhyML to provide heterogeneous composition of control systems and dynamic models. The Signal Flow metalanguage can interact with non-Signal Flow blocks within CyPhyML, closing the semantic gap between physical components and functional components. Our work extends upon an older Domain Specific Modeling Language (DMSL) for functional modeling which had previously relied on a closed-source backend. Signal Flow models are semantically linked with dynamic models by means of the CyPhyML integration language. The Signal Flow DSML is an open-source dataflow programming language, similar to Simulink or LabVIEW, designed specifically for modeling embedded systems and their underlying computational semantics. Since the continuous-time, high-precision simulation

environment of Simulink has gained widespread acceptance in the control and modeling community, we have devised a way of exchanging models between Simulink and Signal Flow. Signal Flow's block library bears many of the same constructs as the Simulink library, so that the large preexisting pool of Simulink models can be easily regraphed as Signal Flow functional blocks. Moreover, Signal Flow models can be transformed back into the Simulink environment which may be desirable if the user wishes to employ True-Time kernels as a basis for simulation. As desired, the Signal Flow language is capable of rewriting the dataflow model as C snippets, so that its models can be used to directly generate the software expressed by its models.

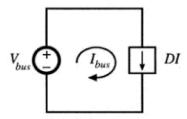

In this work, our primary goal is to offer a fundamental understanding of the use of MIC towards Cyber-Physical System design. To better demonstrate this process, we propose the design of an electrical Cyber-Physical System: a bidirectional DC/DC power converter. This type of electronic device integrates into a hybrid-electric vehicle and regulates power to and from the vehicle's electric battery. The converter's controller functions by flipping electrical switches to alternate the direction of operation. Within either operating mode, the circuit opens and closes a NMOS switch with high-frequency to regulate the voltage at specific nodes within an RLC circuit. Input signals from the vehicle, such as brake-down or accelerator-down, govern whether or not the converter is driving the electric motor, or charging the battery.

In this proposed design, we will model the power converter circuit as well as the software controller. The MIC framework will allow us to model the dynamics of the converter circuit in conjunction with the software logic of the controller. In order to represent the synchronous semantics of the controller logic, we will employ the SignalFlow language to import the controller design from a Simulink model. The controller dataflow will be paired with the DC/DC converter circuit which it will drive within the CyPhyML environment. The heterogeneous model will allow us to create simulations in the dynamic simulation environment of Modelica. Our goal will be to analyze these simulations in order to verify the

stability, and appropriate behavior of our bidirectional converter as it transitions between five different operating modes. The final model will allow us to easily generate deployable code so that the converter can be tested in the context of the physical circuit.

#### I.2.3 Related Works

Embedded and Cyber-Physical Systems modeling is not new, and there are already numerous and diverse approaches towards Embedded and Cyber-Physical Systems modeling. Similar to the approaches of Ptolemy II [33] and ModHel'X [34], our CyPhyML language is centered on genericity, composition and integration. The compositional approach to heterogeneous modeling means that the ability to "glue" disparate models together is inherent in the underlying language framework. Unlike CyPhyML, however, Ptolemy II provides support for a diverse range of Models of Computation on the condition that the outputs of Ptolemy models (or actors) are functional with respect to their inputs and internal states. The strict definition of input and output ports means that model interfaces are casual and one-directional, limiting the scope of physical components that can be represented. In our approach, ports can be directionless and interconnections between components outline strict mathematical constraints between variables at the interfaces. This allows for more complex equations to govern component interactions, like the sharing of flow and effort variables across interfaces in order to represent linked dynamical quantities such as current and voltage, or position and force.

Hardebolle and Boulanger [31] provide a canonical overview of the current state-of-the-art of heterogeneous modeling approaches. In this summary, the CyPhyML language stands out because of its support for an open set of modeling languages, and also because of its underlying metamodeling framework. Some tools, such as Kermeta [35] and AToM3 [36], also employ a metamodeling framework for model composition and translation. Kermeta seeks to attach strict operational semantics to the elements of a metamodel, however, it provides only the fundamental framework for the future prospect of weaving executabil-

ity into metalanguages: it would require specialized effort to apply these principles onto each desired Domain Specific Modeling Language. Our ESMoL framework already contains developed behavior models for many metalanguages catered towards Cyber-Physical System modeling, and supports rich semantic exchange between DSMLs. Additionally, the operational semantics of CyPhyML are provided by the Modelica language. The AtoM3 metamodeling language is strikingly similar to CyPhyML in that metamodels are used to describe Domain Specific Languages, and the AtoM3 or CyPhyML environments themselves can automatically function as tool suites for specifying the resulting metalanguages. AtoM3 does not support some key modeling fundamentals such as hierarchical composition, or built-in model exchange. Furthermore, AtoM3 does not support the continuous evolution of a metalanguage as the needs and scope of the project change. Updated metalanguages have difficulty importing designs created in older versions of the same metalanguage in AtoM3. By comparison CyPhyML can update model files from upstream metamodel changes, threby permitting a continously evolving metamodel.

Some approaches have arisen from coming to terms with the fact that tools which are used in different phases of the design cycle are based on different theoretical foundations and, therefore, it is too difficult to maintain consistency of the models between verification tools and implementation tools. For example, the Rosetta [32] specification language implements a multi-aspect framework similar to CyPhyML and is capable of representing different views and domain characteristics of a component. Additionally, the language bears excellent aspect merging capabilities for supporting formal verification and validation. However, the highly-abstracted Rosetta models are not directly executable, meaning that its users must switch to a different tool for the design phases of the development process, and redraw a similar model. This "similar models" approach stands in high contrast with ESMoL approach in which models used for specification and composition are the same models used for analysis, verification, deployment, and execution.

#### **CHAPTER II**

## **Background**

#### **II.1** Cyber-Physical Systems

While Embedded Systems have been in existence for decades, a new "revolution" in information technology is mounting due to the increased pervasiveness of Embedded Devices, and their proliferation into everyday life. As stated by the National Research Council, "IT is being embedded into a growing range of physical devices linked together through networks," and is doing so with continued momentum as technologies become smaller, faster, and cheaper [13]. The Research Council predicts that the collectivization and interoperability of these numerous devices will yield even greater systems, causing a revolutionary shift in how we interact with the physical world: "These networked systems of embedded computers...have the potential to change radically the way people interact with their environment by linking together a range of devices and sensors that will allow information to be collected, shared, and processed in unprecedented ways" [13]. These proclaimed integrative systems have become commonly known as Cyber-Physical Systems.

To approach the problem of modeling these complex Cyber-Physical Systems, we start by introducing three fundamental models of computation. Each of these models is crucial in representing the behvaior of computational and physical processes. Our model-integrated approach aims to unify these mixed domains in order to describe a comprehensive system in a single framework.

#### **II.1.1** Synchronous Reactive Systems

As we have just discussed, Embedded and Cyber-Physical systems mix the hardware and software of digital controllers with the continuous dynamics of physical systems. These systems are intrinsically Heterogeneous, in the sense that such systems combine asynchronous events, periodic timed components, and continuous dynamics [14]. Of these

Models of Computation we will first delve into the one based on asynchronous events: synchronous-reactive systems.

Real-Time Systems are precisely defined synchronous reactive systems, in that they are reactive systems subject to externally defined timing constraints [16]. However, formal synchronous-reactive systems are devoid of the idea of time; therefore, they are not time-triggered. Rather these systems operate only in reaction to their environment, and—in a sense—run at the speed of their environment. In this way synchronous reactive systems maintain a permanent interaction with their environment [15]. It behooves us to apply this synchronous-reactive model of computation to Cyber Physical systems which foment a close relationship with their operating environment.

Figure II.1: (a) On the left we have an example SR system. (b) The traces of these NOT blocks in response to a change at time = 3.45s

An example of a synchronous-reactive system would be the Logical NOT component. (Diagram of logical NOT) Operating within the confines of Boolean logic, the Logical NOT simply inverts its input signalwhich will be considered the environment in this isolated example. When implemented a Logical NOT essentially remains passive and holds the output value until an instant of change in the environment alters the input signal. When the instant of change occurs, the system immediately inverts the output so that its function holds true wherein the output is always the logical inverse of the input. This system is reactive in the sense that instants of change are initiated by environmental events, and also synchronous because the notion of time arises within the model as a series of ordered instants

[17]. To clarify the system's operation is not driven by or reliant on time, yet the concepts of "Before", "After", and "At the time same" are all well-defined and controllable. These attributes make synchronous-reactive systems easy to describe as a model: such models compose well into other models of computation by permitting deterministic, hierarchical, concurrent programming [16].

By continuing to study the Logical NOT example, we see that the component is a proper synchronous-reactive system because it operates instantaneously. The logic block's outputs are produced in synchronization with its inputs. Therefore, the Logical NOT is only operational for an infinitesimally short instant when triggered by the environmental input (an abstraction of the electrical current swing) and then remains passive for all other time. Nothing happens between the instants of synchronous-reactive systems and the inverter's continuous-time signal inversion is abstracted as an instantaneous step event. Because no operations take place during between instants, a deployed synchronous-reactive system only needs to be fast enough to simulate synchronous behavior by ably responding to each discrete event [17].

Because of these described properties, synchronous-reactive systems are relatively easy to model. These systems are simple because they have no inherent notion of time. From a programming perspective, this means that components only need to be called or invoked when a change in input occurs. In practice the simulation behavior of a fully synchronous-reactive system much resembles a chain-reaction. Consider the picture chain of Logical NOT blocks as in Figure II.1a: When a change causes 'a' to flip from LOW to HIGH, the f1 block reacts by instantaneously changing output b from HIGH to LOW. Then without any time transpiring f2 detects a change in its input, and reactively flips the output to the correct value. This behavior is depicted in Figure II.1b. From an observation standpoint, the changes in signals 'a', 'b', and 'c' all occur concurrently at the exact same simulation-time.

#### **II.1.2** Discrete-Event Systems

In discrete-time systems, phenomena change value or state at discrete points in time, rather than continuously or as a reaction to external stimuli [18]. What this means is that a discrete-time system will not reevaluate inputs if an input change occurs between 2 discrete events: changes can only transpire after a specified—and often periodic—interval has elapsed, at a specific point in time. This is different from synchronous-reactive systems which do not have delays or any conceptualization of time, and instead evaluate changes in input immediately [15]. However, a discrete-event model suddenly resembles a synchronous-reactive model if we ignore time and focus only on the sequence of events. In a sense, the synchronous-reactive model is an abstraction of the discrete-event model [14]. So while both models of computation were subject to instants of change, real numbers will now represent time increments between the instants of the discrete-event model.

The Signal Flow metalangauge for modeling control loops obeys discrete-event semantics. Each block contains an intrinsic samplePeriod variable which determines the frequency of invocation. At the end of each period, a Signal Flow block will call its governing C code and produce functional output with respect to the current input. This semantic definition is sufficient for describing the computational process execution that we seek to model with the Signal Flow language.

Let's examine a climate-control system as an example discrete-event system. When the system detects that the room temperature has raised above 70 degrees, the controller starts the air-conditioning unit. Within this system the input temperature changes continuously, yet the temperature sensor performs a sample every 60 seconds. This specific process is only active once every minute, but reliably so. Unlike a synchronous reactive system, it is not an input change which triggers a system event: Rather, the system can only "see" the physical temperature input at specific discrete-events which occur periodically every minute [14]. If the temperature rises above 70 degrees only 2 seconds after a temperature sampling event, then the climate control system will not be able to react for another 58

seconds—when the sensor is next scheduled to operate. Regardless of the fluctuations in temperature, the climate control unit will experience events at 0 seconds, 60 seconds, 120 seconds, and so on. Unlike their synchronous-reactive counterparts, discrete-event systems may retain the same previous inputs and outputs even as an event related invocation occurs.

Discrete-event systems are useful to model because most real-time systems operate according to discrete-event principles. Both systems are defined by their logical correctness as well as their temporal correctness. Furthermore, the scheduling of discrete-event systems very closely resembles the sequencing and scheduling of real-time processors [18]. Take, for example, a typical 1GHz processor which not continuously evolve, nor is its operation a sole reaction to changing input. Instead, the computer processor in operation for infinitely small instants of change which periodically recur every nanosecond. The processor is time-triggered to process inputs at an interval set by the clock crystal. This behavior is very closely modeling by a discrete-event model of computation.

Discrete-event systems simulate similarly to synchronous-reactive systems, but with one small change: a discrete-event component is allowed to schedule itself to run again in the future. Models that obey these discrete-event semantics would no longer react asynchronously to changes in input. This periodic rescheduling is accomplished through persistent creation of super-dense time tags. After a discrete-event component executes it will create a tag for itself to run again in the future, with the specific time determined by its operating frequency. To give an example, a computer's main 1GHz processor might trigger itself to execute 1 nanosecond later in the future. The tag would resemble  $tag_{main, 1} = (t + 1ns, 0)$ . If the graphics processor operates at 4GHz, then after an event instance it would create a tag of the form  $t_{graph, 1} = (t + 0.25ns, 0)$ . These multiple tag requests create an ordered event-queue. It is the job of the simulation tool to walk forward in time and invoke discrete-event elements according their tag-time. This is how the notion of time is instantiated within a discrete-event model. Presumably, the inputs to the model will change along with the passing of simulation time. If the output of a discrete-event block

flows into a synchronous-reactive block, then the synchronous-reactive element would be triggered and would operate instantaneously at the instant of the discrete-event. This execution model interacts smoothly with synchronous-reactive elements because both models of computation are semantically similar. With the addition of periodic rescheduling abilities, there is now a measureable notion of time between instants of change within the model, so that any discrete-event system can be properly described and simulated [14].

# **II.1.3** Continuous-Time Systems

Whereas the discrete-event systems that we have rehashed center around the concept of "when", continuous-time systems focus instead on the concepts of "eventually" and "always" [19]. Signals in these systems do not only undergo change at discrete intervals, but rather are persistently evolving. This is akin to the behavior of physical processes which act as continuously evolving systems. System designers and programmers have come to terms with the fact that models for the computation and the physical world diverge and while not suited for simulating aspects of computational systems, continuous-time models are perfectly suited for modeling physical dynamics [12]. Continuous time models do not undergo discrete instants of change, and instead are constantly evolving along a time continuum with their behavior defined by ordinary differential equations. Concepts such as rotational motion, temperature change, current flow, and air resistance are naturally described by differential equations and are a perfect fit for the continuous-time model.

The Simulink and Modelica languages employ an underlying continuous-time framework [25], [21]. Therefore, modeling physical plants—for example through state-space models—is intuitive, and well supported. Because the discrete-event MoC is an abstraction of continuous-time semantics, these languages are capable of implementing discrete-event blocks which have configurable periodic properties [21]. Modelica is suitable for simulating the execution of mixed MoC's and will be used for analyzing the interaction between discrete computations, and continuous-time elements for our DC/DC converter system [25].

Figure II.2: Circuit layout for a Linear Variable Differential Transformer Displacement Transducer

Let's consider a Linear Variable Differential Transformer Displacement Transducer, or LVDT for short. An LVDT is essentially a high-precision position sensor. Its construction consists of a cylindrical array of solenoid coils aligned adjacently, and placed around a ferromagnetic core as visualized in Figure II.2. The ferromagnetic core is placed around the object whose position is to be measured. An alternating current drives excitation in the center primary coil, and the resulting magnetic field induces current in the secondary coils (as in an electrical transformer). The displacement is measured as a function of the voltage differential between the two secondary coils. When the solenoids are at the center of the ferromagnetic core as in the leftmost diagram of Figure II.3, the differential is precisely zero since the secondary solenoids are out of phase by 180 degrees. However, as the solenoids slide positively away from the core, there becomes an increase in voltage at one of the secondary coils and a decrease in another as seen in Figure II.3. The amplitude of the resulting voltage differential signifies the amount of displacement along the core. The phase of the output allows the system operator to know in what direction the displacement takes place: positive displacement means the differential signal is in phase with the primary, and negative displacement means the signal is out of phase with the primary.

Figure II.3: Behavior of an LVDT across 3 different operating conditions

This device fits into the realm of continuous-time models because its operation is governed by the analog behavior of its circuit. This is not a digital system which undergoes change at clock ticks. Instead the system's currents, fluxes, and voltages are all constantly evolving according to position and as governed by differential equations. Even if the system's input bears discontinuities, the system response will maintain its continuous characteristics. Because the system has analog voltage signal as output, it can provide boundless precision. Unlike discrete-event systems, the signals of continuous-time systems do not pause between the various instants of change.

## **II.2** Dynamics Simulations

#### II.2.1 Modelica

Modelica is a modeling language well suited for modeling large, complex, and heterogeneous systems [20]. Unlike other languages, Modelica has been specifically designed to facilitate the exchange of models, model libraries, and simulation specifications [21]. These models, together with connections and blocks, make up the fundamental building blocks of the Modelica environment. Models can be composed hierarchically, can support multi-domain capability, and can involve mixed models of computation [24]. Modelica's multi-physics engine provides the user with the opportunity to combine electrical, mechanical, hydraulic, and thermodynamic components together in one model [20]. Additionally, Modelica is designed for the modeling of continuous-time and discrete-event physical sys-

tems and, therefore, is able to solve continuous-time equations as well as discrete equations [21].

Figure II.4: Example of a mixed domain model in Modelica

Modelica's models use equation-based signals to express the physical constraints imposed by the physical interconnections within a system [24]. These connections are created simply by clicking on both endpoints within a model's schematic, or object diagram. The models themselves, like resistors or gears, can be added to a model in "lego-like" fashion by dragging them onto the object diagram from the predefined object library [21]. The model components can be comprised of additional object diagrams, however, atomic components are defined by an equation based description of the model behavior. At simulation time a Modelica compiler will translate all of the model's subsystems and connections into equations which permit simulation and analysis. The acausal nature of Modelica's connection ports supports simulation of the continuous processes of physical dynamics. Unlike typical casual ports, acausal ports represent a simultaneous, bidirectional energy exchange between components [24]. For example, Modelica's Electrical Pin interface contains both

voltage (effort), and current (flow) variables. Modelica compilers enforce the rule that effort on both ends of a connection remains equal, and that flow on both ends of a connection sums to zero. (In terms of electrical connections, this rule enforces Kirchhoff's Current Law.) This acausal support permits the modeling of complex continuous, physical dynamics.

If we examine Figure II.4 we get a glimpse of a mixed-domain model within Modelica. The large blue and white squares which appear on the periphery of components are the bidirectional acausal pins. Each component has at least two pins corresponding to the component's positive and negative terminals. Also visible in Figure II.4 are the causal signal ports, which resemble blue and white triangles. The purely computational components—like the vehicle controller—possess only causal ports, and the ports are strongly typed as input or output signals. This type of component interface is not well suited for physical dynamics, but is adept at modeling computational processes. Hence, the illustrated model is a mixed-domain model because it composes causal computational connections with acausal physical connections.

The Modelica language is configured to allow the generation of efficient simulation code automatically by the compiler. An example of one such compiler is OpenModelica, an open-source editor that also permits the graphical editing of object diagrams. Since its first version in 1997, Modelica has become warmly accepted by the modeling and simulation community [21].

#### II.2.2 Simulink

Another popular simulation tool is Simulink, which is centered on continuous-time simulation [25]. Unlike Modelica, Simulink is a closed-source language; however, both tool suites provide a similar "drag and drop" type modeling environment. Both tools are adept at modeling and simulating multi-domain dynamic systems, and hybrid models of continuous and discrete components are permitted. Simulink is a causal modeling environment,

Figure II.5: Example of a Simulink control loop

so all signal flow diagrams have distinct input and output ports [24].

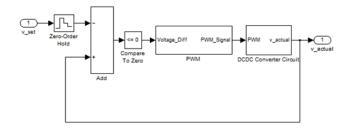

Figure II.5 shows a view of a control loop within Simulink. The model has one input signal, v\_set, and one output signal, v\_actual. The input signal is connected to the input of a Zero-Order Hold Simulink block which discretizes the input signal at a given sample period. The output is relayed on the right side of the block. Akin to Modelica's causal ports, all Simulink ports are strongly typed as either input or output so the input signal itself is not altered by the block. In the diagram, a chain of blocks manipulate the input signal until it finally reaches the output. This specific control loop determines the amount of error in the output signal compared to the input signal in trying to regulate a target output. The output is used as a feedback loop and is summed with the input through the Add block. The output of a block can be replicated and distributed to multiple other Simulink blocks.

Simulink's semantics and syntax make it especially proficient at modeling software and control loops. Once designs are complete, Simulink then allows users to automatically generate C code for deployment on the operational platform [25]. Simulink has gained widespread acceptance within the control and modeling community with many high-profile project implementations.

#### **II.2.3** Software Modeling

Embedded Systems designers are undoubtedly faced with the issue of conceptual incompatibility across mixed semantic domains, since they are highly specialized and since tool suites for these aspects of design diverge with no single unifying model. The described

process is lengthy and often requires exorbitant manual rework, and failing to develop a cohesive system model can lead to unintended disruptions in the design cycle. For example, the seemingly innocuous change of a faster data-rate—while compatible in the signal-flow domain—could completely invalidate the system when implemented within the software and hardware architectures. The current solution to avoid ensuing rework is to program conservative performance margins in anticipation of an eventual integration with the hardware platform. Still, peculiarities arising from the choice of hardware or software architecture may not surface until late in the design cycle, or until the system is fully deployed [10]. Long development, deployment, test cycles limit the amount of iterative rework allowed within a timeline, and often schedules do not permit going back and reworking early design phases. However, current state-of-the-art still requires designers to backtrack and rework earlier stages of design in order to patch these issues due to faulty understanding of the interaction between control, software, and hardware [29]. If the domain-specific modeling tools bare different interpretations of a model across tool suites, then the resulting model will become invalid when integrated together. The solution of structuring and patching tool suites to create consistent, exchangeable model definitions is time-consuming in itself, and is not warranted unless the finished products are applicable to multiple different designs.

## **II.2.4** Modeling within Simulink

Simulink, developed by MathWorks, is widely used for the modeling and simulation of embedded system controllers. Its popularity has led to the formulation of many specialized and third-party function libraries, namely the "Real-Time Workshop Embedded Coder", and "Aerospace Toolkit." Specialized functions aside, Simulink provides the user with the fundamental control system formalisms such as Integrators and Transfer Functions.

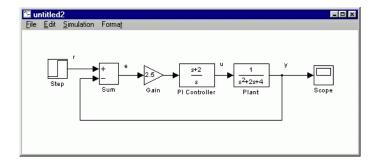

For example, Figure II.6 shows a simple control loop within the Simulink environment. Starting on the left, we observe that the signal from the input Step Function flows into a

Figure II.6: Example of a Simulink control loop

Sum block where it gets added to negative feedback. The output flows next into a familiar Gain block, followed by a PI Controller block. Finally, the signal flows into plant dynamics, as represented by the Transfer Function block. The functional meaning of these blocks, as well as their graphical syntax is standard in the modeling and control community.

Simulink provides a robust continuous-time environment for coupling plant dynamics with discrete-event signal-flows. Hardware-in-the-loop simulations are also possible. Many design engineers prefer Simulink because its syntax checker can accurately detect faults and algebraic loops within a design. Furthermore, its debugging engine is powerful making Simulink easy to adopt. It has been used for modeling the signal-flows of automotive, avionic, and embedded systems in general. Simulink has received widespread adoption among control engineers, largely due to its flexibility in accommodating different types of diverse design problems [26].

## **II.2.5** Embedded Systems Modeling Language (ESMoL)

ESMoL reconciles the problem of cross-domain modeling, by incorporating the multiple aspects of dynamics, signal flow, software architecture, and hardware architecture together into a single multi-aspect design environment. ESMoL, created at Vanderbilt University, is a flexible tool suite for creating Embedded Systems that aims to provide a resolution of semantic inconsistency between tool suites [10]. ESMoL's designers took into account the fact that Simulink has become a de facto standard for control and signal-flow composition

and, therefore, have allowed ESMoL's users to import existing Simulink and Stateflow models, while still permitting native control loop specification. Within the signal flow paradigm ESMoL possesses many functional blocks that resemble Simulink blocks, and its simulation framework similarly supports synchronous discrete-event semantics, so that no information is lost during the model exchange. What sets ESMoL apart from Simulink is that ESMoL permits the componentization of working signal flows in order to define the actual data flows on the deployed software platform. Details of the target hardware can be linked with the software components, leading to a holistic definition of the modeled system [7]. These are among ESMoL's many processes and techniques which aid in the development of safety-critical embedded systems:

- 1. The ESMoL tools confine the system design to a single design environment with multiple aspects for representing mixed-domain details of design. This unified environment allows the composition, analysis, and simulation of models as well as the synthesis of deployable program code. ESMoL employs the principles of MIC by regarding modeling as the central activity for system development [3].

- 2. ESMoL aims to shorten design cycles by providing models with strong analysis and simulation capabilities. ESMoL permits a rapid transition to deployment by supporting code synthesis techniques such as hardware-specific task code generation, as well as data communication code generation.

- 3. ESMoL allows the definition of deployment related information, such as the mapping of control loops to software constructs, and the mapping of software constructs to hardware platforms. Simulations execute under the constraints of the software and hardware mappings.

- 4. The two-stage design of ESMoL model interpretation isolates the interpreter code from ESMoL's compositional framework. The motive for this approach is to allow the flexible integration of simulation tools and code generators. The syntax

and semantics of an ESMoL model are first transformed into the intermediate ES-MoL\_Abstract language. Then simulation and analysis tools create feedback and deployable code from this intermediary representation of the model.

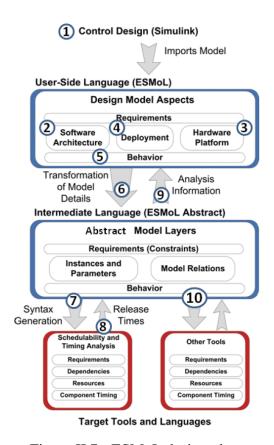

Figure II.7: ESMoL design phases

Figure II.7 shows a process flow that encompasses all phases of ESMoL development. Starting from the top of the diagram at Step 1, the first step in the ESMoL design flow is importing the control design from Simulink. Once the Simulink design is within Cy-PhyML, Step 2 covers the mapping of the control loop blocks to software processes, and signal flows to data messages. In a similar fashion these hardware components are mapped onto hardware platforms and network interfaces as per Step 3. Development at Steps 4 and 5 covers the specification of timing and scheduling details within the hardware platform. At this point in the process, the model is sufficiently defined to be transformed into the intermediate ESMoL\_Abstract language putting all relationships and structural models into

a consistent representation (Step 6). A specific interpreter is chosen for Step 7 to generate the simulation code for the model (in our case Modelica), and then this information is fed back into the design to support optimal design modifications (Steps 8 and 9). ESMoL is also capable of synthesizing deployable code for target platforms directly from the models which allows for rapid deployment techniques (Step 10).

The goal of ESMoL and of its unified semantics is to shorten design cycles by automating the software and hardware integration stages of design. As discussed earlier, ESMoL is able to compose Simulink control structures within software and hardware concepts to define the final system implementation. Since componentization information is captured within aspects of the model, ESMoL can automate the deployment process. During simulation, Simulink blocks become realized as C language templates whose code is automatically organized according to the hierarchical and architectural mappings within the model. Simulation models can either be run on the tool suite computer, or on a specific platform to accurately observe the behavior of the model upon target system. If the system does require rework after a simulation, ESMoL facilitates the backtracking process by feeding simulation information back to earlier stages of design. For example, timing information from the simulation is saved and made available in the signal-flow and timing aspects, making it easy to reconcile missed execution deadlines.

The goal of automating these design, simulation and analysis tasks is to foster quicker iterations within the development cycle. With the current state-of-the-art, inconsistencies across tool suites can effectively distort designers' perceptions of a system and mislead them into developing a separate design solution, unrelated to the specified requirements or unable to be implemented. The ESMoL tool suite evades this issue (and additional design iterations) by unifying the multiple design domains within a single multi-aspect environment. The intended goal of ESMoL is for the overall project to move towards a correct implementation that most accurately reflects the designers' understanding of the design problem [10].

# **II.3** Model-Integrated Computing

Model-Integrated-Computing(MIC) addresses the needs of creating complex multi-domain systems by adopting a fully model-integrated approach to design at all levels of design. In this sense, models not only achieve the objective of designing and representing a system, but also provide the main avenues for analyzing, testing, generating, simulating and even operating embedded systems [1].

Models both become the design language and the analysis tools that underlie every level of system design from beginning to end. As opposed to an animator's model—for example—of a story board which mostly serves as a rough palette for initial brainstorming that is ultimately scrapped, MIC embraces models as the very foundation and continuously evolving architecture of the desired system. Rather than looking to the system model for an oblique outline during design, within the MIC approach the model is actually the platform in which the designer creates and programs the system. Modeling serves as the metalanugage for which system information is drafted, designed, analyzed, simulated, and even deployed [3].

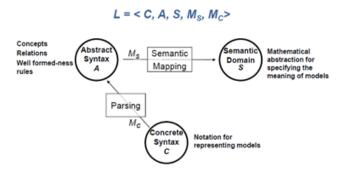

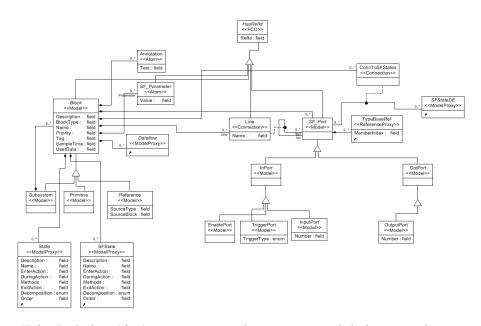

By embracing MIC, we can create metalanguages that represent all necessary system information in the form of models. These languages represent not only the system's operation, but also physical dynamics assumptions about the system's environment [1]. With this specialized approach, we guarantee a tightly coupled design process where we can model the integration constraints and analyze not only the standalone software operation, but also the operation of the software system in its environment.