# CHARACTERIZATION OF THE MECHANISMS AFFECTING SINGLE-EVENT TRANSIENTS IN SUB-100 NM TECHNOLOGIES

By

Jonathan Ragnar Ahlbin

#### Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

May, 2012

Nashville, Tennessee

## Approved:

Professor Lloyd W. Massengill

Professor Bharat L. Bhuva

Professor Arthur F. Witulski

Professor Robert A. Reed

Dr. Stephen P. Buchner

# **DEDICATION**

This dissertation is dedicated to my grandfather, Frank R. Ahlbin Sr., who was the first engineer I ever knew. He provided me guidance and encouragement on my path to becoming an electrical engineer.

#### **ACKNOWLEDGMENTS**

The first person I would like to thank is my wife Holly who has been supportive and patient with me on my journey of attaining a Ph. D. She has stayed up late with me countless times listening to me talk about my work and has even taken an interest in learning more about radiation effects work herself! I would also like to thank my parents and my entire family for their encouragement and understanding. Next, I would like to thank Dr. Lloyd Massengill for his continual support, confidence, patience, and mentoring throughout this project. He has pushed me to look critically at my work and become a better researcher.

I would also like to thank Dr. Bharat Bhuva, whose has helped me identify new paths in my research and has been a constant source of ideas. Additionally, I would like to thank Drs. Art Witulski, Robert Reed, and Steve Buchner for serving on my committee. This process has been exciting because of them.

Special appreciation is also deserved for Drs. Tim Holman, Ron Schrimpf, and Dan Fleetwood, Mike Alles, and Daniel Loveless. A special thanks goes to Dr. Matt Gadlage for helping me develop and test the numerous test structures used in this work. Additional thanks needs to be given to Drs. (or soon to be) Wole Amusan, Sarah Armstrong, Nick Atkinson, Megan Casey, Sandeepan DasGupta, Nick Hooten, Nelson Gaspard, and Brian Olson. They have directly or indirectly provided valuable input to this work. I would also like to thank Dennis (Scooter) Ball, Jeff Kauppila, and Brian Sierawski from Vanderbilt-ISDE for their contributions in helping me develop my TCAD models. Recognition is also deserved for my friends in the Radiation Effects group.

Finally I would like to thank the Defense Threat Reduction Agency Rad-Hard Microelectronics Program for their financial support of this research.

# TABLE OF CONTENTS

|                       |                                                         | Page  |

|-----------------------|---------------------------------------------------------|-------|

| DEDICATION            |                                                         | ii    |

| ACKNOWLEDGMENTS       |                                                         | iii   |

| LIST OF FIGURES       |                                                         | ix    |

| LIST OF TABLES        |                                                         | XV    |

| I. FUNDAMENTAL ME     | ECHANISMS OF SINGLE-EVENTS                              | 5     |

|                       | Charge Generation, & Charge Collection                  |       |

|                       |                                                         |       |

|                       | OF SINGLE-EVENT TRANSIENT GENERATION                    |       |

|                       |                                                         |       |

|                       | ility                                                   |       |

| -                     | haracterization                                         |       |

| <u> </u>              |                                                         |       |

| III. EFFECT OF N-WELL | CONTACT AREA ON SINGLE-EVENT TRANSIEN                   | NTS27 |

| Introduction          |                                                         | 27    |

|                       | ence on SET Pulse Widths                                |       |

| Design of a Test Circ | cuit to Quantify the Influence the Percentage of N-Well | Area  |

| Contacted has on SE   | T Characterization                                      | 30    |

|                       | -ion Broadbeam SET Measurements                         |       |

| Conclusion            |                                                         | 42    |

| IV. EFFECTS OF CHARG  | GE SHARING ON SINGLE-EVENT TRANSIENTS                   | 44    |

| Introduction          |                                                         | 44    |

| Pulse Quenching       |                                                         | 44    |

|                       | e Quenching at the 130 nm Technology Node               |       |

|                       | Ieasurements Demonstrating Pulse Quenching              |       |

|                       | Pulse Quenching in Sub-100 nm Bulk CMOS                 |       |

| V. DOUBLE-PULSE-SIN   | IGLE-EVENT TRANSIENTS                                   | 85    |

| Introduction                     | 85  |

|----------------------------------|-----|

| SET Measurement Circuit Design   |     |

| DPSET Experimental Results       | 87  |

| Simulation Setup                 |     |

| Discussion                       |     |

| Conclusion                       | 100 |

| VI. CONCLUSIONS                  | 101 |

| Conclusion                       | 101 |

| REFERENCES                       | 103 |

| APPENDIX A: PUBLICATIONS         | 110 |

| Published Journal Articles       | 110 |

| Published Non-Journal Articles   | 113 |

| APPENDIX B: PRESENTATIONS        | 114 |

| Conference Presentations to Date | 114 |

# LIST OF ACRONYMS

| ASET       | Analog Single Event Transient           |

|------------|-----------------------------------------|

| BJT        | Bipolar Junction Transistor             |

| CME        |                                         |

| CMOS       | Complementary Metal Oxide Semiconductor |

| DD         | Displacement Damage                     |

| DICE Latch | Dual Interlocked Cell                   |

| DPSET      | Double-Pulse-Single-Event Transient     |

| DRAM       | Dynamic Random Access Memory            |

| DSET       | Digital Single Event Transient          |

| DUT        |                                         |

| EHP        |                                         |

| GCR        |                                         |

| IC         |                                         |

| LET        | Linear Energy Transfer                  |

| MBU        |                                         |

| RHBD       |                                         |

| SCR        | Solar Cosmic Rays                       |

| SE         | Single Event                            |

| SEB        | Single Event Burnout                    |

| SEE        | Single Event Effect                     |

| SEGR       | Single Event Gate Rupture               |

| SEL  | Single Event Latchup               |

|------|------------------------------------|

| SET  |                                    |

| SEU  | Single Event Upset                 |

| SOHO | Solar and Heliospheric Observatory |

| STI  |                                    |

| TCAD | Technology Computer-Aided Design   |

| TCR  |                                    |

| TID  |                                    |

| TMR  | Triple Modular Redundancy          |

| ТРА  | Two-Photon Absorption              |

# LIST OF FIGURES

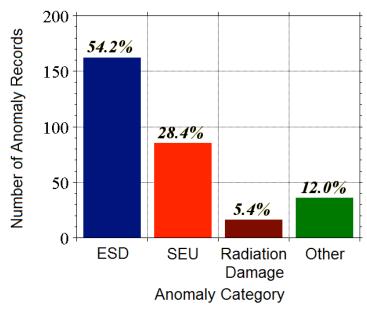

| Fig. II-1. Distribution of spacecraft anomaly records versus anomaly type (ESD: electrostatic discharge; SEU: single event upset) [Ma02] (data from [Ko99]) 6                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

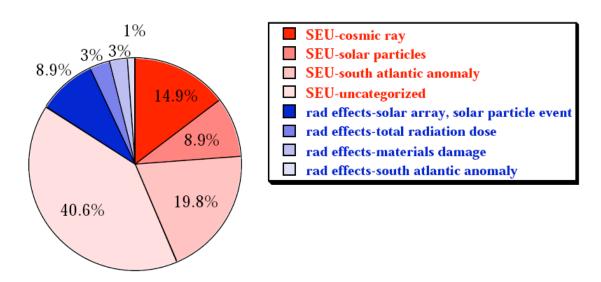

| Fig. II-2. Breakdown of SEU and radiation damage anomaly records [Ma02] (data from [Ko99])                                                                                                                                                                                                        |

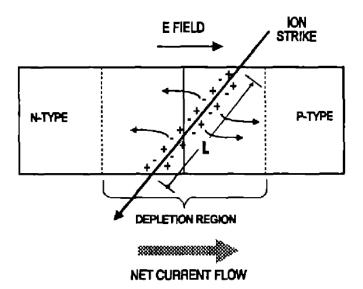

| Fig. II-3. Depletion region charge collection via drift transport from an ion strike [Ma93]                                                                                                                                                                                                       |

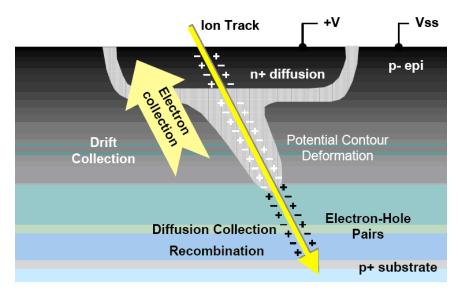

| Fig. II-4. Illustration of an ion strike on a reverse-biased n+/p junction [Ba05]                                                                                                                                                                                                                 |

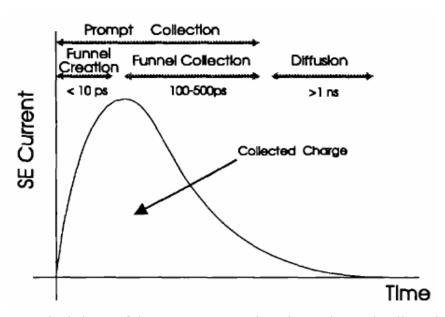

| Fig. II-5. Typical shape of the SE current at a junction. The total collected charge corresponds to the area under the curve. [Me82]                                                                                                                                                              |

| Fig. II-6. Qualitative view of the funnel effect: a) creation of the ion-induced plasma track, b) movement of electrons toward the positive bias, and c) potential drop along the track and redistribution of equipotential lines down the track [Ma93]                                           |

| Fig. II-7. Illustration of the horizontal parasitic bipolar junction transistor in a pMOS transistor [Am06]                                                                                                                                                                                       |

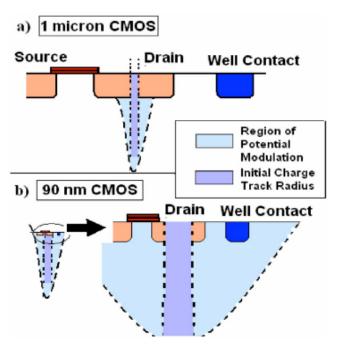

| Fig. II-8. Relative range of the "field funnel" in a 1 µm and a 90 nm technology. Top figure (a) shows the "funnel" creating a potential perturbation only on a small portion of the drain. Bottom figure shows a strike with the same radius covering the source, drain and well contact [Da07]. |

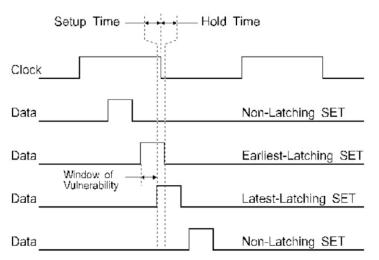

| Figure III-1. An illustration showing how a pulse may or may not be latched by a storage [Mav02]                                                                                                                                                                                                  |

| Fig. III-2. Illustration of the horizontal parasitic BJT in a pMOS transistor [Am06] 17                                                                                                                                                                                                           |

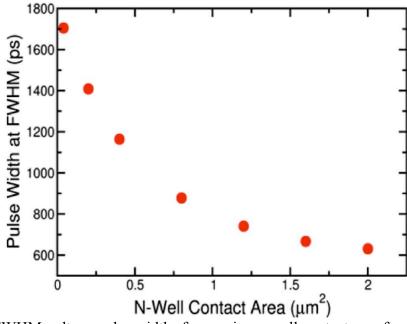

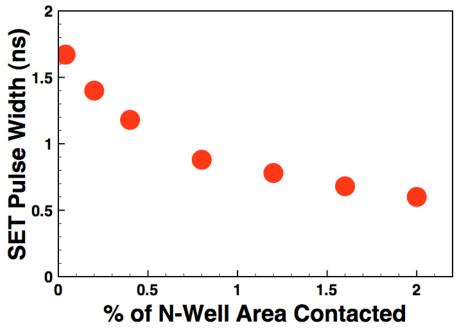

| Fig. III-3. FWHM voltage pulse widths for varying n-well contact area from 200 nm x 200 nm to 200 nm x 10 nm. The decrease in the pMOS transistor pulse width (from 1671 to 601 ps) with increased contact area is due to reduced well resistance [Amus07] 18                                     |

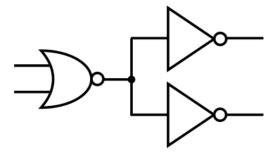

| Fig. III-4. Gate level schematic of a NOR gate followed by two inverters                                                                                                                                                                                                                          |

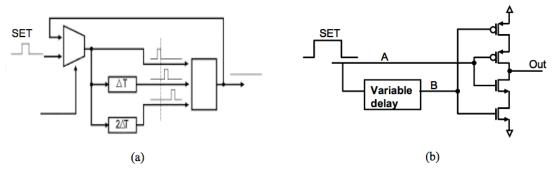

| Fig. III-5 (a) Variable temporal latch technique and (b) guard gate based technique for characterizing the width of SET pulses [Ea04] [Ba06]                                                                                                                                                      |

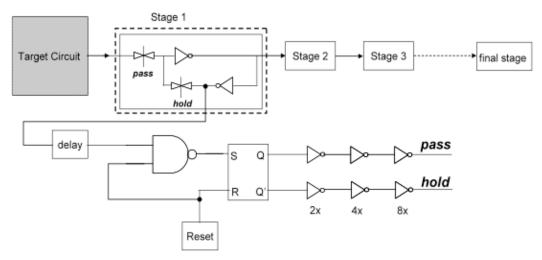

| Fig. III-6 Autonomous pulse-width measurement technique [Na06]                                                                                                                                                                                                                                    |

| Fig. IV-1. 3D TCAD simulations at an LET of 40 MeV-cm <sup>2</sup> /mg illustrating the effect n-well contact area has on parasitic BJT conduction [Ol07]                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. IV-2. 3D TCAD simulations at an LET of 40 MeV-cm <sup>2</sup> /mg illustrating the effect n-well contact area has on SET pulse width [Am07]                                                                                                                                      |

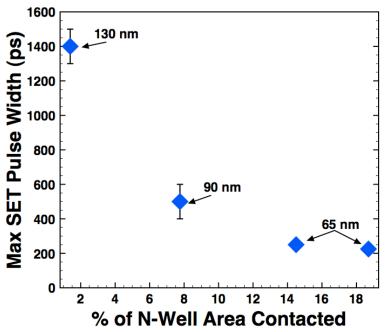

| Fig. IV-3. Experimental SET pulse width measurements for 130 nm, 90nm, and 65 nm bulk CMOS technologies at an LET of 58 MeV-cm <sup>2</sup> /mg [Ga10]                                                                                                                                |

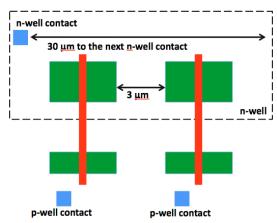

| Fig. IV-4. N-well contacting scheme that covers $0.14\%$ of the n-well area (minimum n-well contact design rules). Twelve minimum sized n-well contacts of $0.26~\mu m$ x $0.26~\mu m$ were placed 30 $\mu m$ apart in each of the ten n-well chains dedicated to that target design. |

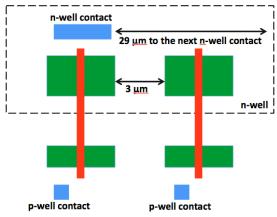

| Fig. IV-6. N-well contacting scheme that covers 1.2% of the n-well area because each inverter has a 0.26 μm x 0.26 μm n-well contact                                                                                                                                                  |

| Fig. IV-7. N-well contacting scheme that covers $5.0\%$ of the n-well area. Each inverter has its own $1.13~\mu m \times 0.26~\mu m$ n-well contact.                                                                                                                                  |

| Fig. IV-8. N-well contacting scheme that covers 15.7% of the n-well area because a 0.26 µm wide n-well contact spans the entire length of the n-well                                                                                                                                  |

| Fig. IV-9. Experimental results for an LET of 58 MeV-cm <sup>2</sup> /mg showing the distribution of SET pulse widths for the five different n-well contacting schemes                                                                                                                |

| Fig. IV-10. Experimental results for an LET of 30.86 MeV-cm <sup>2</sup> /mg showing the distribution of SET pulse widths for the five different n-well contacting schemes 35                                                                                                         |

| Fig. IV-11. Experimental results for an LET of 21.17 MeV-cm <sup>2</sup> /mg showing the distribution of SET pulse widths for the five different n-well contacting schemes 35                                                                                                         |

| Fig. IV-12. Experimental results for an LET of 9.74 MeV-cm <sup>2</sup> /mg showing the distribution of SET pulse widths for the five different n-well contacting schemes 36                                                                                                          |

| Fig. IV-13. Experimental results for an LET of 3.49 MeV-cm <sup>2</sup> /mg showing the distribution of SET pulse widths for the five different n-well contacting schemes 36                                                                                                          |

| Fig. IV-14. Comparison of TSMC 90 nm SET results to [Ga10] SET results for an LET of 58 MeV-cm <sup>2</sup> /mg.                                                                                                                                                                      |

| Fig. IV-15. Cross section versus LET for the five different inverter chain test structures.                                                                                                                                                                                           |

| Fig. IV-16. Cross section for the five TSMC 90 nm inverter chain test structures for an LET of 58 MeV-cm <sup>2</sup> /mg. 40                                                                                                                                                         |

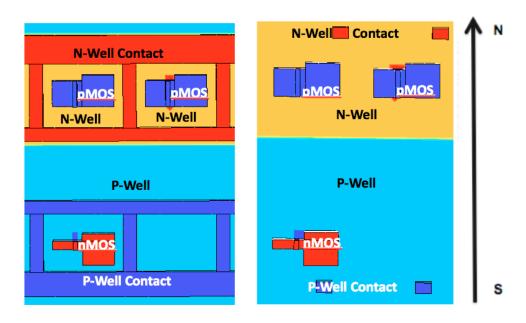

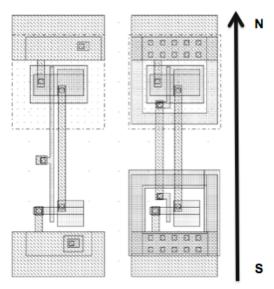

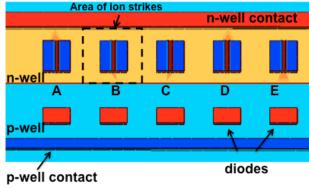

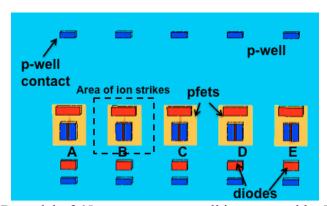

| Fig. V-18. Layout of the 65 nm target inverter chain where each row of inverters shares a common n-well (common n-well).                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. V-19. Layout of the 65 nm target inverter chain where each inverter has its own separate n-well (separate n-well).                                                                                                                                        |

| Fig. V-20. TCAD model of 65 nm common n-well inverters with pMOS transistors modeled in TCAD and nMOS transistors as compact models                                                                                                                            |

| Fig. V-21. TCAD model of 65 nm separate n-well inverters with pMOS transistors modeled in TCAD and nMOS transistors as compact models                                                                                                                          |

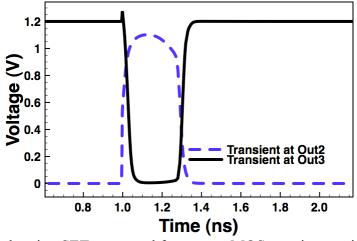

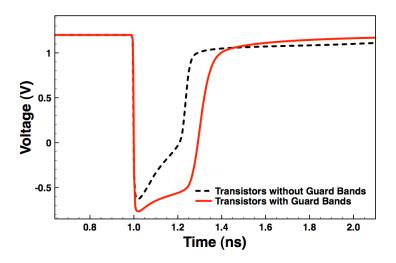

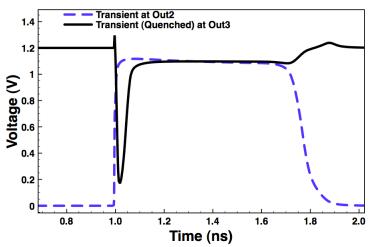

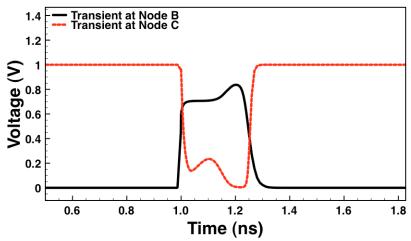

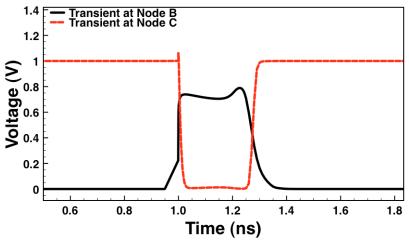

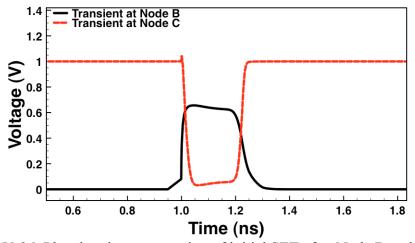

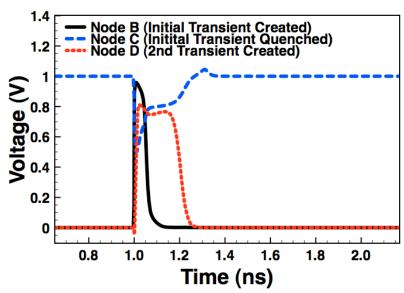

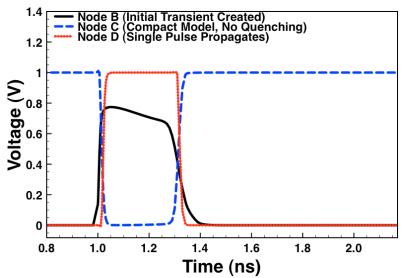

| Fig. V-22. Plot showing propagation of initial SET after Node B and then after Node C. The SET is from a normal incidence LET of 58 MeV-cm <sup>2</sup> /mg ion strike on the drain-center of the pMOS transistor at Node B in the common n-well circuit       |

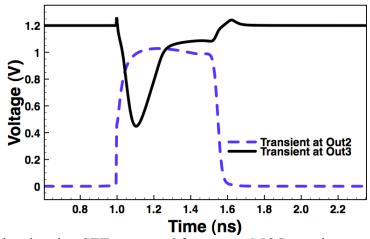

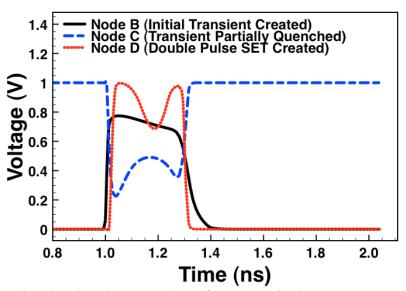

| Fig. V-23. Plot showing propagation of initial SET after Node B and then after Node C. The SET is from a normal incidence LET of 58 MeV-cm²/mg ion strike 100 nm away from the drain-center of the pMOS transistor at Node B in the common n-well circuit. 67  |

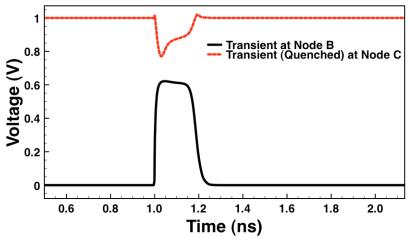

| Fig. V-24. Plot showing that by replacing the pMOS transistor at node C with a compact model, the SET is no longer quenched.                                                                                                                                   |

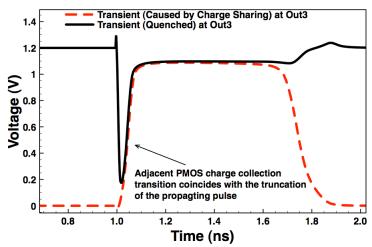

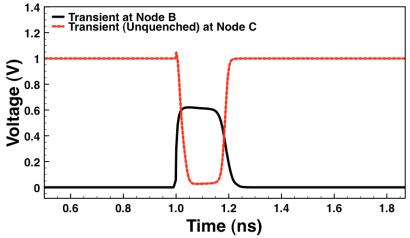

| Fig.V-25. Plot showing propagation of initial SET after Node B and then after Node C. The SET is from a normal incidence LET of 58 MeV-cm <sup>2</sup> /mg ion strike on the drain-center of the pMOS transistor at Node B in the separate n-well circuit      |

| Fig. V-26. Plot showing propagation of initial SET after Node B and then after Node C. The SET is from a normal incidence LET of 58 MeV-cm²/mg ion strike 100 nm away from the drain-center of the pMOS transistor at Node B in the separate n-well circuit 69 |

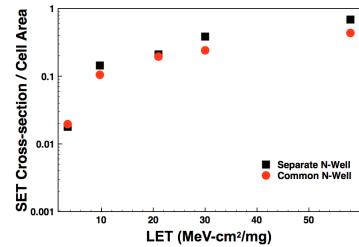

| Fig. V-27. Plot of SET cross-section versus LET with the measurements normalized to the cell area.                                                                                                                                                             |

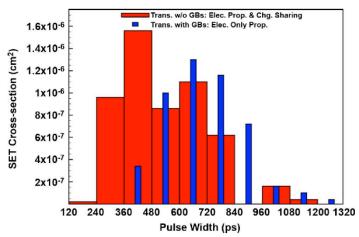

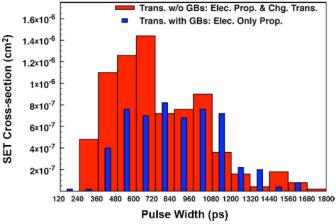

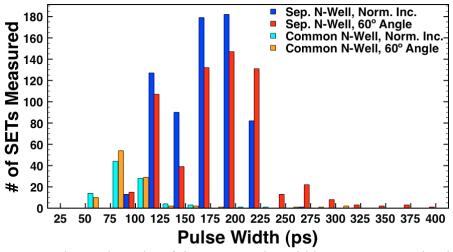

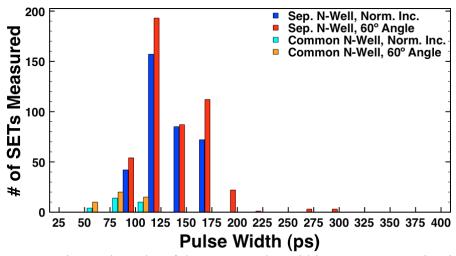

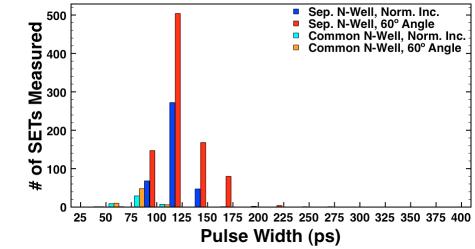

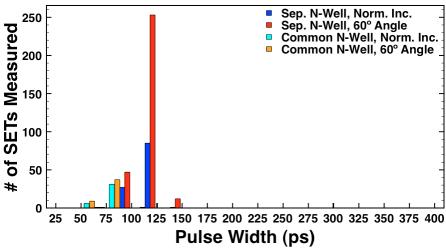

| Fig. V-28. Experimental results of the 65 nm pulse width measurement circuit for the common n-well and separate n-well inverter designs for a 58 MeV-cm <sup>2</sup> /mg ion                                                                                   |

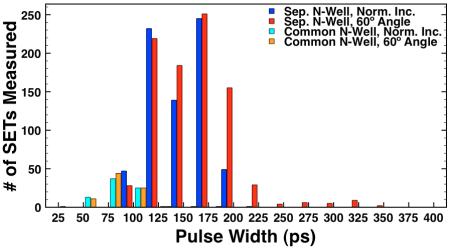

| Fig. V-29. Experimental results of the 65 nm pulse width measurement circuit for the common n-well and separate n-well inverter designs for a 30 MeV-cm <sup>2</sup> /mg ion                                                                                   |

| Fig. V-30. Experimental results of the 65 nm pulse width measurement circuit for the common n-well and separate n-well inverter designs for a 21 MeV-cm <sup>2</sup> /mg ion                                                                                   |

| Fig. V-31. Experimental results of the 65 nm pulse width measurement circuit for the common n-well and separate n-well inverter designs for a 9.7 MeV-cm <sup>2</sup> /mg ion                                                                                  |

| Fig. V-32. Experimental results of the 65 nm pulse width measurement circuit for the common n-well and separate n-well inverter designs for a 3.5 MeV-cm <sup>2</sup> /mg ion                                                                                  |

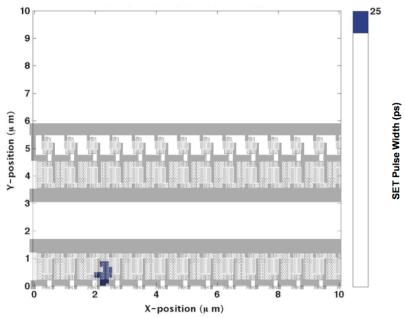

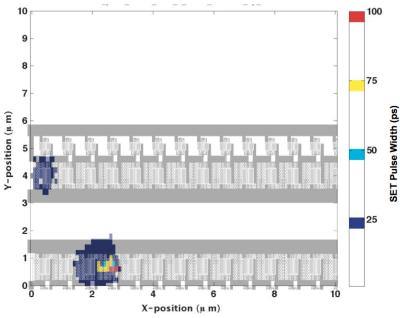

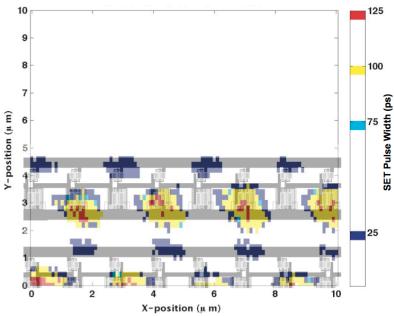

| Fig. V-33. An XY map of the common n-well 65 nm inverter target chain for a 10 μm x 5 μm area at 251 pJ laser energy                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. V-34. An XY map of the common n-well 65 nm inverter target chain for a 10 μm x 5 μm area at 638 pJ laser energy                                                                                               |

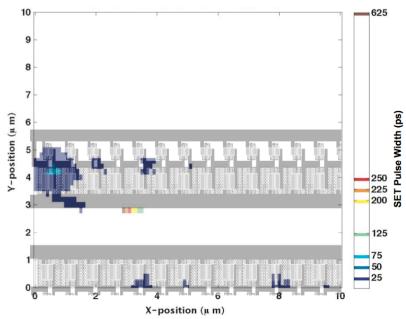

| Fig. V-35. An XY map of the common n-well 65 nm inverter target chain for a 10 µm x 5 µm area at 1025 pJ laser energy                                                                                              |

| Fig. V-36. An XY map of the separate n-well 65 nm inverter target chain for a 10 µm x 5 µm area at 386 pJ laser energy                                                                                             |

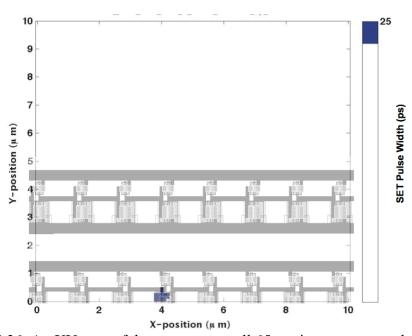

| Fig. V-37. An XY map of the separate n-well 65 nm inverter target chain for a 10 $\mu$ m x 5 $\mu$ m area at 773 pJ laser energy                                                                                   |

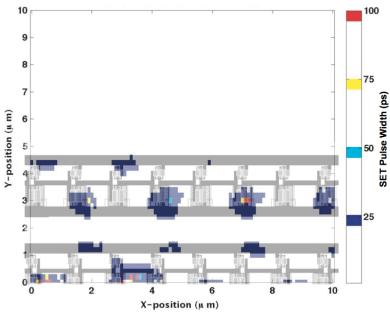

| Fig. V-38. An XY map of the separate n-well 65 nm inverter target chain for a 10 $\mu$ m x 5 $\mu$ m area at 1160 pJ laser energy                                                                                  |

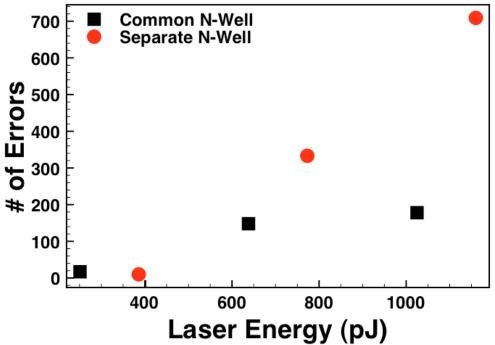

| Fig. V-39. Plot showing the number of errors observed for each target chain at different laser energies. A 5 $\mu$ m x 10 $\mu$ m area was rastered for each target chain                                          |

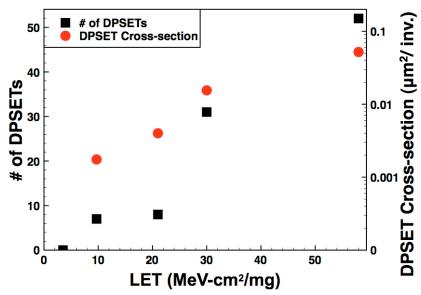

| Fig. VI-1. Number of DPSETs and cross-section for separate n-well inverter target chain with all ions incident at 60° angle longitudinal to the n-well.                                                            |

| Fig. VI-2. Single pulse voltage transient.                                                                                                                                                                         |

| Fig. VI-3. Double pulse voltage transient                                                                                                                                                                          |

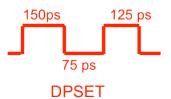

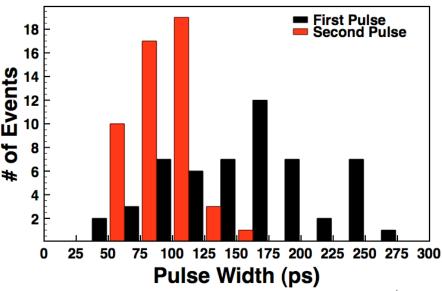

| Fig. VI-4. Plot showing the different pulse widths measured for the 1 <sup>st</sup> and 2 <sup>nd</sup> pulses of the DPSETs that occurred during the LET of 58 MeV-cm <sup>2</sup> /mg experimental run 88        |

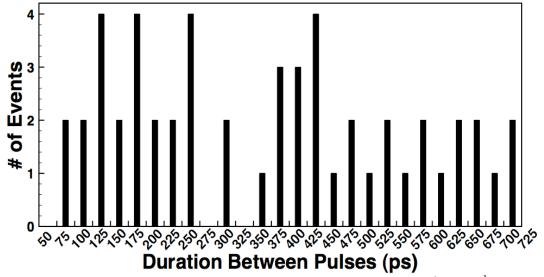

| Fig. VI-5. Plot showing the time durations measured between the 1 <sup>st</sup> and 2 <sup>nd</sup> pulses of the DPSETs that occurred during the LET of 58 MeV-cm <sup>2</sup> /mg experimental run               |

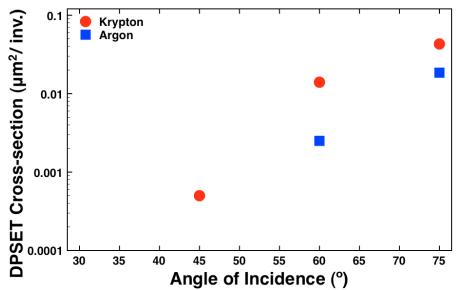

| Fig. VI-6. Plot showing the DPSET cross-section of the separate n-well circuit for both the ions of Krypton and Argon. As the angle of incidence increases, the number of DPSETs that are observed also increases. |

| Fig. VI-7. TCAD model of 65 nm common n-well inverters with pMOS transistors modeled in TCAD and nMOS transistors as compact models                                                                                |

| Fig. VI-8. TCAD model of 65 nm separate n-well inverters with pMOS transistors modeled in TCAD and nMOS transistors as compact models                                                                              |

| Fig. VI-9. Plot showing the generation of a transient at node B, then being quenched at node C, and then finally a second transient being generated at node D                                                      |

| Fig.VI-10. Plot showing the generation of a DPSET in the separate n-well inverter chain simulation. An initial pulse is created at node B, then it is partially quenched at node C. It then propagates through node D and forms a DPSET.                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. VI-11. Plot showing that pulse quenching is responsible for the generation of the DPSET. A compact model replaces the pMOS transistor at node C, which stops pulse quenching from occurring                                                                                                                                                                              |

| Fig. A-1. Entire 10 μm x 10 μm 65 nm pMOS transistor 2D model                                                                                                                                                                                                                                                                                                                 |

| Fig. A-2. Channel region of the 65 nm pMOS transistor 2D model                                                                                                                                                                                                                                                                                                                |

| Fig. A-3a. $I_d$ - $V_g$ and $I_d$ - $V_d$ calibration curves for 2D and 3D pMOS transistors TCAD models.                                                                                                                                                                                                                                                                     |

| Fig. A-4. Entire 5 μm x 5 μm x 10 μm 65 nm pMOS transistor 3D TCAD model 112                                                                                                                                                                                                                                                                                                  |

| Fig. A-5. I <sub>d</sub> -V <sub>g</sub> curve showing a low voltage mismatch where there is not enough leakage current occurring. To fix this mismatch you can try to move the LDDs closer together or increase the LDD doping.                                                                                                                                              |

| Fig. A-6. $I_d$ - $V_g$ curve showing an incorrect $T_{ox}$ value. By increasing or decreasing the $T_{ox}$ value, the TCAD curve will move uniformly down or up                                                                                                                                                                                                              |

| Fig. A-7. $I_d$ - $V_g$ curve showing a mismatch because of the wrong $V_t$ value. To change the $V_t$ value, you can adjust the position or doping of the halos. You can also add a $V_t$ implant in addition to the halos.                                                                                                                                                  |

| Fig. A-8. $I_d$ - $V_g$ curve showing a mismatch caused by the wrong workfunction value. To fix this issue, the doping of the poly-gate can be changed, or instead of using a poly-gate an ideal contact can be put directly on top of the gate oxide. Then in the sdevice script, the workfunction of the gate can be defined and in turn calibrated until the curves match. |

# LIST OF TABLES

| Table V-1 – Average SET pulse widths at 60° strike along the well | . 57 |

|-------------------------------------------------------------------|------|

| Table V-2 – Average SET pulse widths at normal incidence          | . 75 |

#### **CHAPTER I**

#### INTRODUCTION

Single-event effects (SEE) have been a growing concern for the space, military, and commercial electronic sectors since the 1970's [Do03]. These concerns have increased as circuit error data is collected on modern-day integrated circuits (ICs) showing an increased susceptibility to SEE as feature sizes decrease and frequencies increase [Bu01]. A single-event (SE) occurs when a charged particle, such as a heavy-ion, passes through a semiconductor material creating electron-hole pairs (EHPs) along its strike path until it has lost all its energy or left the semiconductor [Ma93]. Sensitive junctions within the material, usually reverse-biased p/n junctions, can collect these extra carriers causing harmful effects based on the circuit topology and the amount of charge collected [Ma93].

Many different types of energetic particles can cause a SE. Four particular types of energetic particles have been shown to cause SEs: alpha particles, neutrons, protons, and heavy-ions [Ma79] [Na08].

One type of effect resulting from a SE is a spurious voltage pulse called a single-event transient (SET) [Ma93]. SETs are a significant reliability concern, as they can compete with legitimate logic signals and corrupt downstream logic and latches. In digital circuits, SETs that propagate unhindered in a circuit can become single-event upsets (SEUs) [Ma93]. A SEU is an alteration in the state of a memory circuit (e. g. a memory call can change from a logic "1" state to a logic "0" state) or when corrupted

data propagates to an output of the circuit -- leading to an observable error. These types of errors are termed "soft errors" as they do not result in a permanent failure (hard error) within the circuit.

As transistor density increases with each new CMOS technology node, the probability of a single ion causing a SET in a circuit or depositing charge on multiple nodes increases [Ba05][Ro07]. Multiple-node charge collection from a single ion strike can render hardened storage cells and SET mitigation techniques (such as guard rings, guard drains, additional well contacts, etc.) ineffective [Ol05, Am06]. Therefore, it is important to understand SET characteristics at each new technology node and resulting impacts on circuit designs.

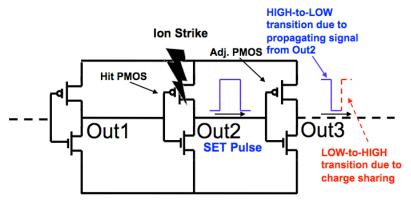

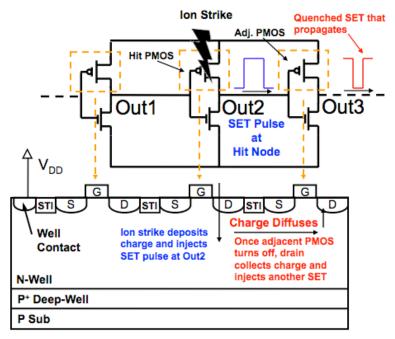

In a 130 nm bulk CMOS technology, research has shown that charge sharing resulting from heavy-ions incident at high angles (> 60°) can affect the pulse width of a propagating SET [Ah09]. The interaction of the electrical signal propagation and charge sharing through the substrate can cause the SET to shorten -- termed "pulse quenching." Mixed-mode 3D technology computer aided design (TCAD) simulations at the 90 nm technology node have shown that pulse quenching can occur at normal incidence (0°) for minimally spaced and sized circuits. This result indicates that charge sharing is becoming prevalent in sub-90 nm bulk processes.

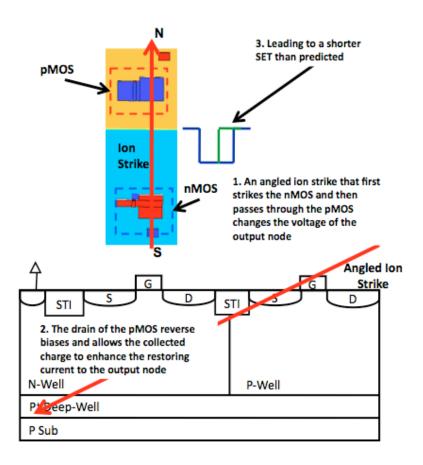

At the 65 nm technology node, heavy-ion data (normal and at angle) highlight the prominence of charge sharing and pulse quenching [Ah10]. While at 130 nm, where pulse quenching was observed only for ion strikes at high incident angles, pulse quenching (thus the presence of charge sharing) has been observed to occur in a 65 nm bulk technology for ions at normal incidence. This result is attributed to the increase in

transistor density at 65 nm. Additionally during TCAD simulations and heavy-ion testing, it has been observed that single-ion strikes at high angles can cause double-pulse SETs (DPSETs) on a single electrical path [Ah11].

Through a thorough characterization of different technology nodes (130 nm, 90 nm, and 65 nm) this dissertation notes significant mechanisms that affect the operation of digital circuits. These mechanisms have in several cases nullified the effects of traditional radiation-hardened-by-design (RHBD) techniques, but have also led to the creation of new RHBD techniques designed to consider, and occasionally take advantage of mechanisms such as charge sharing and pulse quenching [At11]. Moreover, by examining charge sharing in multiple technology domains, the specific mechanisms, the interaction of the mechanisms, and the resulting device/circuit responses can be isolated and analyzed as they present themselves through technology scaling. Without thorough analysis at each technology level, predictions of how new CMOS technology nodes will perform in the space environment will be inaccurate.

This dissertation uses both three-dimensional mixed-mode technology-computer-aided design (TCAD) simulations and experimental analysis at the 65 nm, 90 nm, and 130 nm technology nodes to fully characterize the mechanisms that affect SETs in sub-100 nm bulk CMOS technologies. Chapter I introduces the motivation for this work. Chapter II presents background on single-event effects. Within the chapter, single-event effects are identified and explained in context to digital circuits. Chapter III then focuses on the specific single-event effect of SETs and the factors that influence them. In the second part of the chapter, the discussion focuses on common methods of experimental SET measurement and the typical target structures used. Chapter IV discusses the

relationship between the parasitic bipolar and n-well contacts, and how it affects the pulse width of SETs. Chapter V then introduces the mechanism of pulse quenching by using TCAD simulations, heavy-ion data, and laser data, to identify pulse quenching in multiple technology nodes. Additionally the chapter explains in detail how the layout and circuit design can influence pulse quenching. Finally, Chapter VI presents simulation and experimental heavy-ion results that explain a new SET mechanism called DPSETs. Instead of a single ion strike creating a single pulse SET, a single ion strike can result in a DPSET.

The research presented in this dissertation directly impacts the SEE circuit qualification and analysis techniques used in the radiation effects community. Simulations supported by experimental data illustrate how there are new mechanisms in sub-100 nm bulk CMOS that can affect SET pulse widths. These mechanisms can negate traditional RHBD solutions, but also can be used as new RHBD solutions. Designers and researchers can use this work to better analyze SET results, and they can predict how SET pulse width will be affected in future bulk CMOS technologies.

#### **CHAPTER II**

#### FUNDAMENTAL MECHANISMS OF SINGLE-EVENTS

#### Introduction

Microelectronic circuits are exposed to various radiation environments in space and on earth. The exposure of electronics to radiation can lead to temporary or permanent damage of circuits through effects of ionizing particles such as total-ionizing dose (TID), displacement damage (DD), prompt dose (Dose Rate), and single-event effects (SEE). As predicted in [Ma93] with the scaling of microelectronic circuits and the increase in transistor density with each new technology generation, SEEs have become a dominant failure mechanism affecting the reliability of ICs. Therefore, this discussion will focus on SEEs in microelectronic circuits. Though DD [Sr03], Prompt Dose [Al03], and TID [Ol03] are not discussed in this work, references are included for the interested reader.

As shown in Fig. II-1, Koons *et al.* found that in comparison to electrostatic discharge (ESD) damage, other radiation damage (TID), plasma and micrometeroid impacts, and uncategorized energetic particle effects spacecraft anomaly records attributed over 28% of anomalies to SEEs [Ma02]. Of spacecraft anomalies caused only by radiation, 84% are SEE related as illustrated in Fig. II-2 [Ma02][Ko99].

The remainder of this chapter will focus on how energetic particles interact with a semiconductor device, the physical mechanisms of the interactions, and their effects on circuits.

Fig. II-1. Distribution of spacecraft anomaly records versus anomaly type (ESD: electrostatic discharge; SEU: single event upset) [Ma02] (data from [Ko99]).

Fig. II-2. Breakdown of SEU and radiation damage anomaly records [Ma02] (data from [Ko99]).

### Energetic Particles, Charge Generation, & Charge Collection

For a SE to occur, an energetic particle must interact with a semiconductor device. The primary particles of concern in the space environment are protons, heavyions, alpha particles, and electrons. Typically, these particles are a result of cosmic ions, solar flares, products of secondary interactions, or from a natural radiation decay [Ba03].

SEs can also occur within the earth's atmosphere at commercial flight altitudes and even on the ground. For terrestrial electronics, neutrons are the primary radiation effects concern, but particles from device packaging (alphas) along with heavy-ions, protons, electrons, muons, and pions can also be the source of SEs.

When a SE occurs, three things happen: charge generation, charge collection and recombination, and the circuit response. As an energetic particle passes through a semiconductor material, carriers are generated and may directly affect a circuit's operation through coulombic interaction or indirectly through nuclear reactions with the lattice. In direct ionization, electron-hole pairs (EHPs) are created along the particle's strike path until it has lost all its energy or left the semiconductor as shown in Fig. II-3 [Ma93]. For indirect ionization, a collision of particles occurs that results in nuclear reactions that may cause scattering or spallation. The secondary particles then generate charge through coulombic interactions because they have a lower energy than the primary particles. When an energetic particle loses energy, the amount of energy that is lost is referred to as a *linear energy transfer* (LET) value. LET describes the energy loss per unit path length of the particle as normalized by the density of the material and has units

of MeV-cm<sup>2</sup>/mg. As a reference, in silicon an ion with an LET of 97 MeV-cm<sup>2</sup>/mg corresponds to a charge deposition of 1 pC/ $\mu$ m [Do03].

When excess carriers are created by the particle in the material, the carriers must recombine or be collected. Charge can be collected on circuit nodes and cause the circuit to respond incorrectly. One method of charge collection is through drift transport. If charge is within the built-in electric field of a reverse-biased p-n junction, the electric field causes the holes to be swept into the p-region and the electrons into the n-region (drift current), as illustrated in Fig. II-3. Drift transport is a quick process on the order of picoseconds in duration because the carriers are limited only by their saturation velocity.

Fig. II-3. Depletion region charge collection via drift transport from an ion strike [Ma93].

A second method responsible for charge collection is diffusion transport. If charge exists outside of the built-in electric field at the junction, but is within a diffusion length of the junction, then it can be collected. Depending on the size of the diffusion length and the spacing of transistors, a single node or multiple nodes near the particle strike may

collect charge. Unlike drift transport, the diffusion process is a very slow process which can take on the order of microseconds depending on the distance. With the carriers surviving longer in the doped regions than those exposed to drift collection, some carriers may recombine – decreasing the amount of electrons and holes that reach the junction. Fig. II-4 illustrates the charge collected through drift and diffusion processes in a reverse-biased n+/p junction [Ba05]. The initial charge collection is due to field-assisted drift, followed by the collection of charge diffused through the substrate.

Fig. II-4. Illustration of an ion strike on a reverse-biased n+/p junction [Ba05]

When charge is collected by a semiconductor device, radiation-induced photocurrents are observed at the device terminals. The shape of the current pulse on these terminals is the direct result of the charge collection mechanisms involved. Looking at Fig. II-5 [Me82] the initial spike is due to the quick collection of charge via drift with the tail part of the curve due to the slow collection of charge via diffusion. In deep submicron processes, there can be a plateau effect immediately after the initial spike as a result of the circuit load [Da07]. Last, the integral of the current over the total time of the SE is the total charge collected by the circuit node.

Fig. II-5. Typical shape of the SE current at a junction. The total collected charge corresponds to the area under the curve. [Me82].

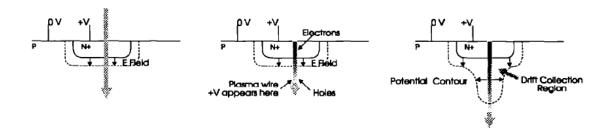

The electric field plays an important role in the charge collection of carriers near p-n junctions as noted in the description of charge collection via drift transport. Additional to charge collection via drift transport, early research found the plasma track created by ionizing particles in a semiconductor can distort the surrounding electrostatic potential gradients, creating a field funnel [Hs81]. When the deposited charge is greater than the doping density of the silicon and a plasma track is formed, a path of free carriers exists between the n and p regions. The depletion region is then effectively hidden from the carriers, which are free to move toward (electrons) or away from (holes) the positively-biased n-region. The spreading resistance along the track leads to a voltage drop in the region, which results in the potential initially at the depletion region to spread down the length of the track. Carriers that were outside the depletion region are now susceptible to the electric field and are quickly collected at the junction by a drift mechanism, known as the funneling effect. An illustration of the plasma wire and the mechanism of field-assisted funneling is shown in Fig. II-6 [Ma93].

In devices at the nanometer scale, the radial dimension of the wire in field-assisted funneling may be wide enough to encompass more than one transistor. However, the basic concept remains the same and for the curious reader, recent work at the nanometer scale are referenced [Da07] [Das07].

Fig. II-6. Qualitative view of the funnel effect: a) creation of the ion-induced plasma track, b) movement of electrons toward the positive bias, and c) potential drop along the track and redistribution of equipotential lines down the track [Ma93].

Similar to the field-assisted funneling mechanism, an additional charge collection mechanism is called the ion shunt effect [Ha85]. As the name implies, the energetic particle (ion) acts as a shunt (wire) when an ion passes through nearby junctions. The ion acts as a wire connecting the two junctions and conducts current between the junctions – enhancing the charge collected on the node.

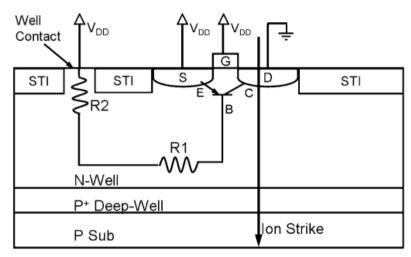

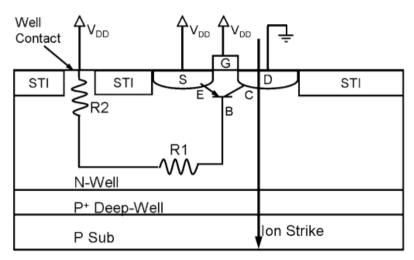

Another mechanism that can enhance charge collection from a SE strike is parasitic bipolar junction transistor (BJT) amplification [Do96] [Ke89] [Am06] [Fu85] [Wo93] [Ol05] [Ol07]. A parasitic BJT exists in both pMOS transistors and nMOS transistors between the source-well-drain regions. However, parasitic BJT amplification is usually observed in dual-well pMOS transistors because the n-well resistivity is typically higher than that of the p-well. When an ion strikes, electrons collect in the n-well and reduce the n-well potential (make it more negative). The collapsing of the well potential along with additional carriers present in the well turns on the parasitic BJT with

the drain acting as the collector, the n-well acting as the base, and the source acting as the emitter, as shown in Fig. II-7 [Am06]. In turn, charge flows from the source and is collected by the drain – leading to an increased amount of charge collection at the circuit node.

Fig. II-7. Illustration of the horizontal parasitic bipolar junction transistor in a pMOS transistor [Am06].

The final charge collection related mechanism that will be discussed is multiple-node charge collection or as it is more commonly known: charge sharing. With the decreasing of feature sizes and the increasing of transistor densities, free carriers from an ion strike may encompass multiple transistors, allowing charge to be collected through drift and diffusion by these transistors. Fig. II-8, for example, illustrates the relative range of the field-funnel (potential collapse) created by a single-ion strike in a 1 µm CMOS technology and a 90 nm CMOS technology [Da07]. The well collapse encompasses a much larger area in the 90 nm technology than in the 1 µm technology. The collapse causes the well to de-bias (lose its biased potential) and for the parasitic BJT to turn on in

multiple pMOS transistors. These pMOS transistors collect little charge from the original ion strike, but collect the majority of charge from the parasitic bipolar injecting charge from the source of each pMOS transistor. As technology scales, charge sharing has become more prevalent in each new generation of bulk CMOS technology.

Fig. II-8. Relative range of the "field funnel" in a 1  $\mu$ m and a 90 nm technology. Top figure (a) shows the "funnel" creating a potential perturbation only on a small portion of the drain. Bottom figure shows a strike with the same radius covering the source, drain and well contact [Da07].

#### Conclusion

This chapter gives an overview of the mechanisms involved in the interaction of a particle with a semiconductor. Mechanisms for charge generation and charge collection are described that are important to the creation of SETs and SEUs in ICs. The remainder of this work will be focused on factors that cause SETs and that determine the pulse width of SETs.

#### CHAPTER III

# FUNDAMENTALS OF SINGLE-EVENT TRANSIENT GENERATION AND MEASUREMENT

#### Introduction

Integrated circuit (IC) technology scaling has led to a decrease in minimum transistor-to-transistor spacing and lower operating voltages, which has led to an enhanced sensitivity to ion-induced SETs in combinational logic data paths [Ba05]. An important metric of SETs is the duration of the disturbance at the signal output of a logic gate. This response is determined by the amount of charge collected at the struck node, the rate of charge accumulation at the node, and the rate of charge removal from the node. SETs with very narrow pulse widths (i.e. short transients) tend to be filtered (attenuated) along the data path by the finite response time of subsequent logic gates, while long pulses can propagate unattenuated deep into the logic.

The remainder of this chapter will explain how understanding SET pulse width can be useful in predicting errors. It will then discuss factors that influence SET pulse widths, and the different experimental methods used to measure SET pulse widths. Finally, the influence SET target structures has on the measurement of SET pulse widths will be summarized.

#### Window of Vulnerability

As introduced in the previous chapter, SETs can be latched by storage devices and be read out as incorrect data (SEU). The pulse width of the SET is a determining factor on whether the SET is latched as an error or not by the storage device. Every storage device or latch has a "window of vulnerability". The window of vulnerability is the period of time that determines whether the SET is latched or is not latched as shown in Fig. III-1 [Bu93] [Mav02]. A latch's window of vulnerability is determined by many factors, such as the sampling window and SET shape.

The sampling window is made up of the latch's setup and hold times. For a latch to latch any signal, the signal must remain the same value for the entire duration of the sampling window. The duration of the sampling window is based on the technology node and the design of the latch, which affects the latching speed of the latch.

If the SET pulse width is longer than the latch's sampling window, the remaining width of the pulse determines the latch's window of vulnerability. Thus, the probability of latching an error is then given by the ratio of the window-of-vulnerability period to the clock period. This probability can be further simplified as the ratio of the SET pulse width to the clock period because SET pulse width is directly related to the window of vulnerability.

Figure III-1. An illustration showing how a pulse may or may not be latched by a storage [Mav02].

Fig. III-1 illustrates how the window of vulnerability determines whether the SET is latched or not. The example latch captures input data on the falling edge of the clock. In the first case, the SET is not latched because the transient occurs before the falling edge of the clock. In the second and third case, the transients are latched because they appear during a clock falling edge. Their pulse widths are wide enough to fall within the sampling time of the latch. The final case shows another non-latching SET, but this time the SET appeared after the latching event.

#### Factors that Influence SET Pulse Widths

The temporal charge collection efficiencies at a node struck by an ion determine the pulse characteristics, including the width, of the resulting voltage SET. These temporal mechanisms controlling the SET pulse width include classical drift, diffusion, and the parasitic amplification at that struck node [Ma93]. Additionally, the design of the

circuit influences the SET pulse width through factors such as the nodal capacitance, interconnect resistance, and current drive of other transistors connected to that node [Bu05].

#### Parasitic Bipolar Junction Transistor (BJT) Amplification

One factor that can significantly affect SET pulse width in sub-100 nm is parasitic bipolar amplification [Amus07]. A parasitic bipolar-junction-transistor structure exists between the source (emitter), the n-well (base), and the drain (collector) in pMOS transistors, shown in Fig. III-2. If this BJT is turned 'on', current is conducted from the MOS source to the drain causing additional charge to be collected on the node of the affected transistors. Therefore, the collected charge from the BJT turn-on and the ion strike can both contribute to the SET pulse width.

Understanding there is a relationship between the parasitic BJT and n-well contact design [Ol07], Amusan *et al.* found that by changing the vertical resistance (R2) of the n-well by varying the n-well contact placement and size, the pulse width of the SET could be affected, as seen in Fig. III-3 [Amus07]. The research in 130 nm and 90 nm bulk CMOS by [Amu07] also stated that the horizontal resistance (R1) could also affect the SET pulse width, but the horizontal resistance was determined by the doping of the n-well. N-wells that had kilo-ohm resistances were easily de-biased and took longer to regain their bias than n-wells with lower resistances.

Fig. III-2. Illustration of the horizontal parasitic BJT in a pMOS transistor [Am06].

Fig. III-3. FWHM voltage pulse widths for varying n-well contact area from 200 nm x 200 nm to 200 nm x 10 nm. The decrease in the pMOS transistor pulse width (from 1671 to 601 ps) with increased contact area is due to reduced well resistance [Amus07].

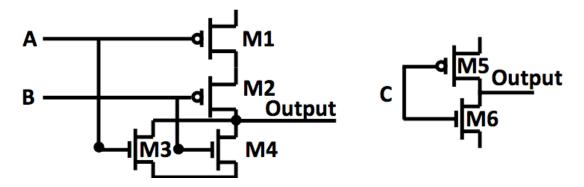

#### Circuit Design

The inherent drive currents and output loads of a circuit are also a key part in determining the pulse width of an SET. CMOS NOR and NOT gates (Fig. III-3) are used to illustrate these concepts. First, consider the drive currents (restoring current) of the transistors. For the case where both inputs are high for the NOR gate, the two nMOS transistors (M3 & M4) in parallel are on and the two pMOS transistors (M1 & M2) in series are 'off'. An ion strike to the drain of M2 will produce a smaller SET than one to the drain of M5 in the inverter with the same size transistor. M3 and M4 restore the voltage to the node as opposed to a single transistor (M6) in the inverter. The greater restoring drive in the NOR reduces the SET pulse width as compared to the inverter.

When the NOR inputs differ, one each of the pMOS transistor and nMOS transistor is 'on', while the other is 'off.' When M1 and M4 are 'off' and M2 and M3 are 'on', the restoring current is half what it is with both inputs 'high' because of the different states of the nMOS transistors. This results in an increased sensitivity of the NOR gate, producing longer SETs than in the previous case. In the opposite case, when M1 and M4 are 'on' and M2 and M3 are 'off', M2 and M3 are equally sensitive to an upset because they both are connected to the output node.

When analyzing the sensitivity of the pMOS transistors, each pMOS transistor is not as equally sensitive when 'off' as the nMOS transistors. With the nMOS transistors in parallel, they both share the 'output' node and the 'ground' node so they have the same loading. However, for the pMOS transistors only M2 is attached to the 'output' node while the other M1 is attached to 'vdd' and M2. Due to this design, M1 has an increased

loading resistance from M2 causing M1 to be less sensitive to ion strikes on its drain while it is 'off'.

Finally, when comparing the single-event sensitivity of the pMOS transistors to the nMOS transistors while 'off', the nFETs are more sensitive. The series pMOS transistors provide a weaker restoring current than the nMOS transistors in parallel because the parallelism of the nMOS transistors provide two separate restoring current paths while the series pMOS transistors provide a single restoring current path to help restore the node after an ion strike.

Fig. III-3. Schematic of NOR and NOT gates at the transistor level.

The next factor to consider in circuit sensitivity to ion strikes is output load. Fig. III-4 shows the NOR gate connected to two inverters. The two inverters add capacitance and resistance to the output of the NOR gate. If both inputs to the NOR are 'low', then the output voltage is 'high'. An ion strike to the drain of an nFET will cause a sudden drop in output voltage. Thus, a transient is formed and propagates to the two inverters. However, the additional capacitance and resistance causes the SET to be shorter because of the load on the output. The additional capacitance and resistance requires a larger

amount of drive current to make the NOR gate switch, and this new requirement causes the collected charge to have a reduced effect on the gate.

Fig. III-4. Gate level schematic of a NOR gate followed by two inverters.

At sub-100 nm, minimally sized gates, as part of a fan-out design, may not have a significant effect on SET pulse widths [Das07]. The additional capacitance is such that the charging time is short compared to the overall pulse width. However, non-minimum sized gates should provide a significant enough load that will affect SET pulse width [Ha09].

In summary, circuits with large capacitive loads and high restoring currents produce fewer and narrower SETs than circuits with small loads and low restoring currents. A NOR gate has been described showing that transistors in parallel can provide double the restoring current compared to a single transistor to a struck node. Also the sensitivity of different transistors in the NOR gate has been explained. Additionally, gates that increase the amount of resistance and capacitance at the output can reduce the number of SETs. Designers can use these ideas to harden their circuits by increasing the size of transistors in a sensitive circuit, which increases the drive strength, resistance, and

capacitance of the circuit. They can add resistors or capacitors to the outputs of circuits to decrease the sensitivity of the output to generation of SETs.

### **SET Experimental Characterization**

When developing circuit designs in a technology, it is important to know the distribution of SET pulse widths that circuits in the technology will generate in a SE environment. Designers can use the information to predict the error rates for their designs. They can also design hardening schemes that will temporally filter-out certain SET pulse widths to decrease the probability of SEUs occurring [Ea04][Ba06]. To characterize these technologies, many different methods exist for measuring SET pulse widths, but the different methods can be generalized into two categories: off-chip SET measurement and on-chip SET measurement.

Off-chip SET measurement typically involves a string of inverters and pulse laser testing. A device-under-test (DUT) can be laser tested either from the front side by single-photon absorption (SPA) or from the backside by two-photon absorption (TPA) ([Mc02], [Mc03], [St85], [Bo86]); this discussion will only focus on back-side TPA laser testing. For backside laser testing, the DUT is arranged on a platform with the laser striking perpendicular to the DUT backside. Use of the laser, allows a specific region to be hit and a characteristic SET pulse width can be observed from that particular area. Therefore, laser testing can give insight into what regions of a circuit will produce the most severe SETs.

To capture the temporal aspects of SETs, a high-speed oscilloscope that can measure pico-second SET rise and fall times is attached to the output of the DUT. The oscilloscope can be setup where it captures the transient upon detection, or the laser pulse can trigger the oscilloscope. A negative to this type of setup is that the resolution of pulse widths that can be measured is determined by the speed of the oscilloscope. Once the SET is captured, the amount of charge deposited by the laser strike can then be correlated with the captured SET pulse width.

On-chip SET measurement techniques are more varied and can be tested by a pulsed laser or can be tested by a particle accelerator. A particle accelerator can accelerate a variety of ions to high energies and create a realistic SE environment similar to what a circuit in space may experience. For testing, the DUT can be tested in vacuum or in air depending on the testing facilities used. In either case, the DUT is traditionally mounted to a platform that can rotate and tilt so the incident angle of the ion to the DUT can be varied.

To measure SET pulse widths on-chip, researchers have used temporal filtering techniques such as using multiple latches with delayed signal paths (Fig. III-5a) [Ea04]. For a signal to propagate through the temporal latch circuit (Fig. III-5a) and be measured, the signal must have a pulse width wide enough that the built-in delay of the signal path does not stop the signal from appearing at the input of the voter at the same time as the other signal paths. If the multiple inputs of the voter are the same, then the signal propagates through the circuit for measurement. Guard-gate-based techniques have also been used to measure SET pulse widths as shown in Fig. III-5b [Ba06] and operate similarly to the temporal latch technique. There are two signal paths — one with no delay

and one with a variable delay. If the signal is wide enough that the built-in delay of the delayed signal path does not stop it from arriving at the input of the guard gate at the same time as the non-delayed signal path, then the guard gate will change states. The signal will then propagate through the gate.

Fig. III-5 (a) Variable temporal latch technique and (b) guard gate based technique for characterizing the width of SET pulses [Ea04] [Ba06].

Another approach to on-chip SET measurement is the autonomous pulse-width measurement technique. Fig. III-6 shows the schematic design of the measurement circuit. This technique measures SET pulse width by latch delays [Na06]. When an SET is generated in the target structure and propagates to the measurement portion of the circuit, the SET passes through latches that switch states. Once an SET pulse has been captured, an attached Field Programmable Gate Array (FPGA) serially reads out the state of each latch in the measurement chain. Software on the FPGA then calculates the number of latches that changed state. Then the pulse width for that SET is calculated by multiplying the number of stages by latch delay.

Fig. III-6 Autonomous pulse-width measurement technique [Na06].

## **Target Structures**

This section discusses how target structures can influence the SET measurement results. A common target design is the current-drive matched inverter. The inverter is a simple design that is easily upset by an ion strike. SET pulse widths from an inverter chain can indicate the type of SETs a more complex combinational logic circuit will generate. However, for accurate SET statistics from accelerator testing, it is necessary to create inverter chains that are over 1000 inverters long. In accelerator testing, the ions cannot be precisely aimed towards sensitive parts of the circuit, so a large sensitive area needs to be designed to increase the probability that ions will strike the circuit.

Recently, Ferlet-Cavrois et al. [Fe07] and Massengill & Tuinenga [Ma08] described how transient signals can widen as they propagate through a combinational logic chain. A description of the mechanism behind the pulse broadening effect in inverter chains is given by Massengill [Ma08]. To minimize pulse broadening in target

circuits, designers are using smaller chains OR-ed together to create the cross-section needed for accurate measurement statistics [Ga10].

Additionally, specific inverter layout techniques, such as minimum spacing or separate wells, can distort SET pulse width results. Experimental data has shown how inverters with the same sizing but different layouts can produce different SET pulse width distributions [Ah09]. The mechanisms behind the differences in SET pulse widths between the inverter layouts will be discussed in Chapter V.

### Conclusion

This chapter discusses the importance of SET pulse widths and some of the factors that influence the generation of an SET. Transistors that have a parasitic BJT are prone to have longer SET pulse widths than transistors with no parasitic BJT. Circuits with high restoring currents and load capacitance are less sensitive to SET generation. Last, the layout and design of target structures can influence SET pulse width results, which can lead to misinterpreting the data.

#### CHAPTER IV

#### EFFECT OF N-WELL CONTACT AREA ON SINGLE-EVENT TRANSIENTS

#### Introduction

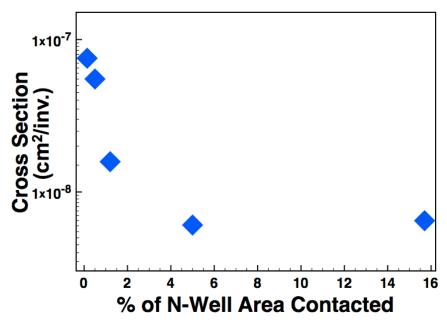

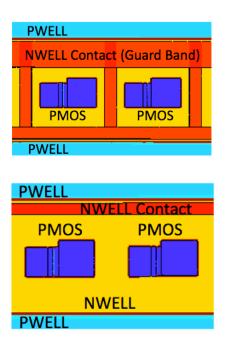

In this chapter, direct experimental evidence is presented that supports previous simulations [Am08] demonstrating the n-well contact area's effect on SETs. Using five inverter chains with a different controlled percentage of the n-well area devoted to ohmic contacts, results show that the inverter chain with minimum-sized n-well contacts spaced 30 µm apart produced the longest and the highest count of SETs. Conversely, the inverter chain with a minimum-contact-width n-well contact strip that spanned the entire n-well, produced the shortest and the lowest count of SETs.

#### Parasitic BJT's Influence on SET Pulse Widths

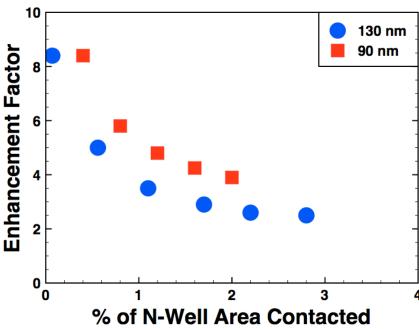

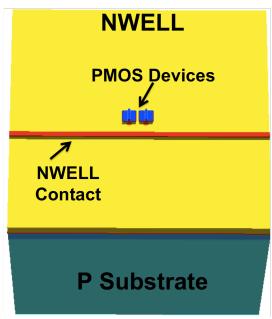

As stated in Chapter III, the n-well contact area influences the amount of charge collected by the drain due to parasitic BJT conduction. Fig. IV-1 shows this influence between n-well contact area and charge collection on a drain of a pMOS transistor by plotting the percentage of n-well area contacted versus enhancement factor [Ol07]. The enhancement factor is defined as the amount of charge collected by the drain of a pMOS transistor with the parasitic BJT enabled over the amount of charge collected by the drain with the parasitic BJT disabled.

Fig. IV-1. 3D TCAD simulations at an LET of 40 MeV-cm<sup>2</sup>/mg illustrating the effect n-well contact area has on parasitic BJT conduction [Ol07].

As the percentage of the n-well area contacted decreases in Fig. IV-1, the amount of parasitic BJT conduction increases [Ol07]. Parasitic BJT conduction increases because the n-well contact controls the vertical resistance of the n-well. As the n-well contact decreases in area, the vertical resistance increases and creates a highly resistive path for electrons to leave the n-well. This condition results in the n-well being easily de-biased by an ion strike and requiring a significant time to restore its bias.

Similar to Fig. IV-1, an inversley proportional relationship exists in Fig. IV-2 between SET pulse width and percentage of the n-well area contacted [Am07]. As the percentage of n-well area contacted decreases, parasitic BJT conduction increases and the drain collects additional charge. The additional charge collection generates a larger collection current at the drain than without parasitic BJT conduction, and the transistor

takes longer to recover. Since the time it takes for the transistor to recover determines the pulse width of the SET, any increase in recovery time results in a longer SET pulse.

Fig. IV-2. 3D TCAD simulations at an LET of 40 MeV-cm<sup>2</sup>/mg illustrating the effect n-well contact area has on SET pulse width [Am07].

Using previously published data, Fig. IV-3 also shows an inversely proportional relationship between the percentage of n-well area contacted and SET pulse width [Ga10]. The figure plots the maximum SET pulse widths measured for 130 nm, 90 nm, and 65 nm dual-well, bulk CMOS technologies. Knowing that an inverseley proportional relationship between the percentage of n-well area contacted and SET pulse width indicates the influence of parasitic BJT conduction, the data suggests parasitic BJT conduction in pMOS transistors determines the maximum SET pulse width in each technology. The data also suggests the design of the n-well contacts may explain the maximum SET pulse width trends observed in the three technology nodes. However, additional variables, such as transistor sizing [Zh04] and pulse quenching [Ah09]

mechanisms exist in those data sets and maybe influencing the SET pulse width data. As a result, those variables need to be minimzed to quantify accurately the effects of n-well contacted area on SET pulse widths.

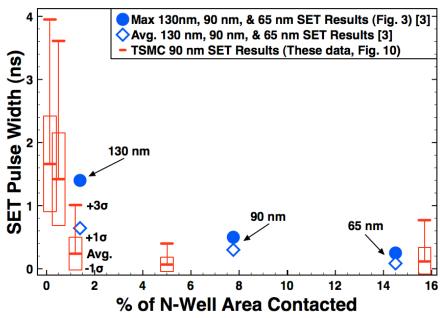

Fig. IV-3. Experimental SET pulse width measurements for 130 nm, 90nm, and 65 nm bulk CMOS technologies at an LET of 58 MeV-cm<sup>2</sup>/mg [Ga10].

# Design of a Test Circuit to Quantify the Influence the Percentage of N-Well Area Contacted has on SET Characterization

To quantify the impact the percentage of n-well area contacted has on SET pulse width, a test chip containing five inverter chains was designed and fabricated in the TSMC 90 nm dual-well, bulk CMOS process. Each inverter chain was followed by an autonomous pulse-width measurement circuit described in [Na06]. The inverters were designed to be current-matched with a pMOS transistor W/L ratio of 400 nm/100 nm and

an nMOS transistor W/L ratio of 200 nm/100 nm. These target chains were laid out in 10 rows of 100 inverters each and ORed together. So that the SETs measured are minimally affected by pulse broadening [Fe07][Fe08].

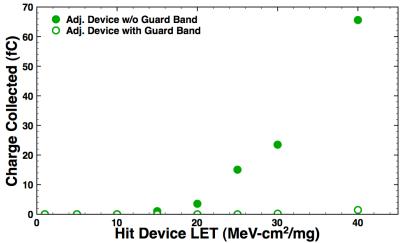

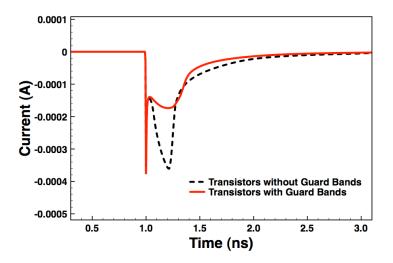

To minimize non-n-well contact area effects, most aspects of the target inverter chains were kept constant across the five different designs. Charge sharing was minimized by setting the active area spacing between the inverters at 3  $\mu$ m. Additionally, each inverter had a minimum-size, 0.26  $\mu$ m x 0.26  $\mu$ m, p-well contact and each target chain at the same sized n-well. The differentiating aspect of the designs was the amount of n-well area contacted.

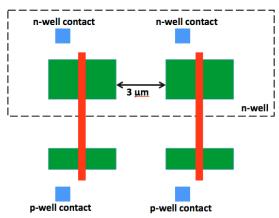

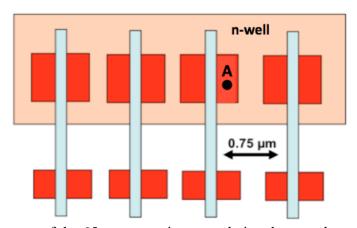

In the first target chain design shown in Fig. IV-4, the n-well was contacted according to the minimum n-well contact and maximum n-well contact spacing as defined by the process design rules. Twelve minimum sized n-well contacts of  $0.26~\mu m$  x  $0.26~\mu m$  were placed 30  $\mu m$  apart in each of the ten n-well chains dedicated to that target design. This is an n-well contact placement design technique commonly used in commercial designs to save space. Since few contacts were used in the design, the contacting scheme covered 0.14% of the n-well area.

Fig. IV-4. N-well contacting scheme that covers 0.14% of the n-well area (minimum n-well contact design rules). Twelve minimum sized n-well contacts of  $0.26~\mu m \times 0.26~\mu m$  were placed 30  $\mu m$  apart in each of the ten n-well chains dedicated to that target design.

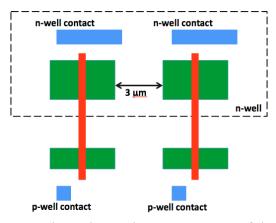

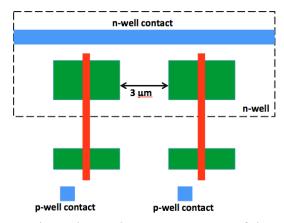

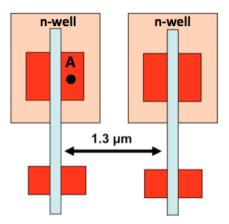

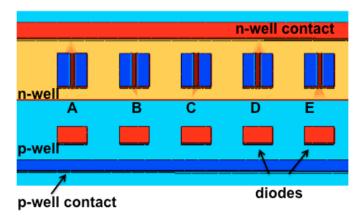

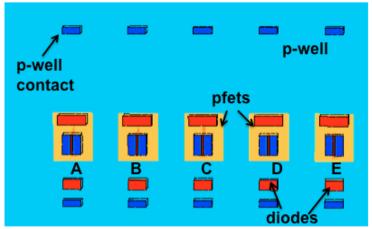

The second design, displayed in Fig. IV-5, included n-well contacts covering 0.5% of the n-well area. The same number of n-well contacts was used as the previous design, but each contact size was larger at 0.98  $\mu$ m x 0.26  $\mu$ m and spaced 29  $\mu$ m from each other. Fig. IV-6 shows the third design where each inverter had a minimum-sized n-well contact. In this design 1.2% of the n-well area was covered by contacts. The next design, shown in Fig. IV-7, included n-well contacts covering a total of 5.0% of the n-well area by placing an n-well contact of 1.13  $\mu$ m x 0.26  $\mu$ m within each inverter cell. In the final design, Fig. IV-8, a single contact that spans the entire length of the n-well was used – commonly known as a strip n-well contact. The strip contact covered 15.7% of the total n-well area.

Fig. IV-5. N-well contacting scheme that covers 0.5% of the n-well area. Twelve minimum sized n-well contacts of 0.98  $\mu$ m x 0.26  $\mu$ m were designed and spaced 29  $\mu$ m from each other.

Fig. IV-6. N-well contacting scheme that covers 1.2% of the n-well area because each inverter has a 0.26  $\mu$ m x 0.26  $\mu$ m n-well contact.

Fig. IV-7. N-well contacting scheme that covers 5.0% of the n-well area. Each inverter has its own 1.13 µm x 0.26 µm n-well contact.

Fig. IV-8. N-well contacting scheme that covers 15.7% of the n-well area because a 0.26 μm wide n-well contact spans the entire length of the n-well.

## Experimental Heavy-ion Broadbeam SET Measurements

The circuits were tested at the Lawrence Berkeley National Laboratory with the 10 MeV/nucleon ion cocktail using Ne, Ar, Cu, Kr, and Xe ions at normal incidence. For Xe the circuit was tested to an effective fluence of  $1.2 \times 10^8$  particles/cm<sup>2</sup>. Mid-energy ions of Kr and Cu were tested to effective fluences of  $5 \times 10^7$  and  $1.5 \times 10^8$  particles/cm<sup>2</sup> respectively. Last, effective fluences of  $3 \times 10^8$  and  $1.2 \times 10^9$  particles/cm<sup>2</sup> were used for for Ar and Ne.

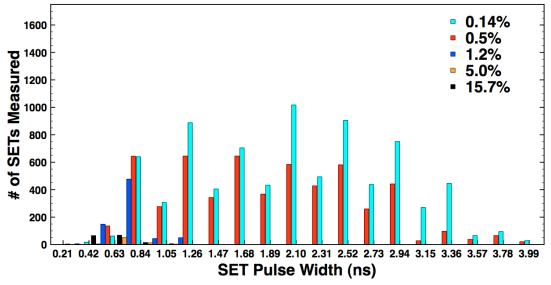

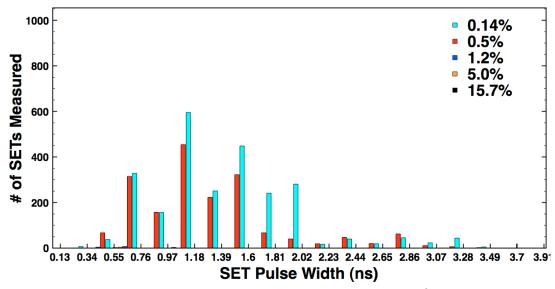

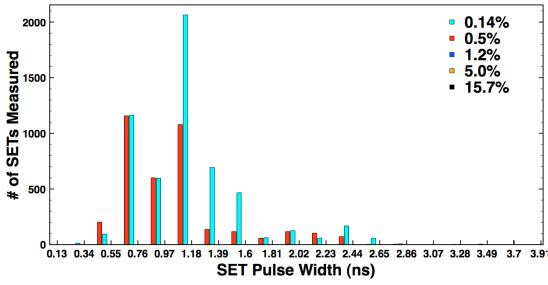

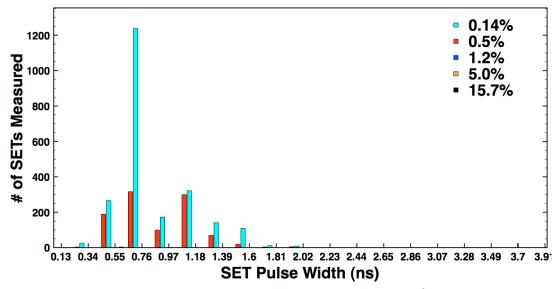

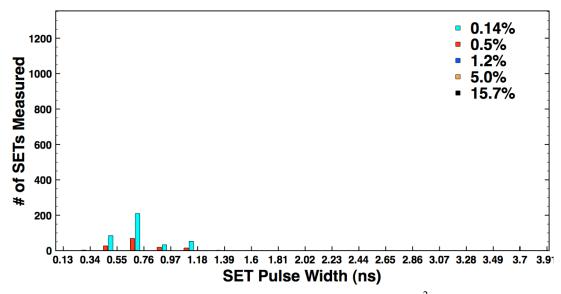

Figs. IV-9, IV-10, IV-11, IV-12, and IV-13 show the results of the circuits exposed to the different ions. Each circuit is labeled by the percentage of n-well area covered by contacts. The distributions for the lowest n-well contact coverage of 0.14% and 0.5% have the widest distributions of SET pulse widths out of the five circuits, whereas the circuits with 5.0% and 15.7% n-well contact coverage have the narrowest pulse width distributions, as seen in Fig. IV-9. In Figs. IV-10, IV-11, IV-12, IV-13, the SET distributions for 5.0% and 15.7% n-well contact coverage are not easily visible because of the significant amount of events observed for the 0.14% and 0.5% circuits.

The distribution of SET pulse widths is the result of ion strikes occurring at different distances from the sensitive area within an inverter [Fe06]. For the 0.14% and 0.5% circuits, their distributions are the widest because the low percentage of n-well area contacted results in a high vertical resistance [Ol05][Amus07]. The high vertical resistance that exists between the n-well and n-well contact (R2 in Fig. III-2) makes the n-well more susceptible to being de-biased by ion strikes compared to a low vertical resistance. The electrons that are generated in the n-well from the ion strike cannot be collected as quickly by the n-well contacts [Da07]. Unlike the 0.14% and 0.5% circuits, the 5.0% and 15.7% n-well area contacted circuits have a narrower distribution of SET pulse widths because the n-well contacting results in a lower vertical resistance [Ol05][Amus07].

Fig. IV-9. Experimental results for an LET of 58 MeV-cm<sup>2</sup>/mg showing the distribution of SET pulse widths for the five different n-well contacting schemes.

Fig. IV-10. Experimental results for an LET of 30.86 MeV-cm<sup>2</sup>/mg showing the distribution of SET pulse widths for the five different n-well contacting schemes.

Fig. IV-11. Experimental results for an LET of 21.17 MeV-cm<sup>2</sup>/mg showing the distribution of SET pulse widths for the five different n-well contacting schemes.

Fig. IV-12. Experimental results for an LET of 9.74 MeV-cm<sup>2</sup>/mg showing the distribution of SET pulse widths for the five different n-well contacting schemes.

Fig. IV-13. Experimental results for an LET of 3.49 MeV-cm<sup>2</sup>/mg showing the distribution of SET pulse widths for the five different n-well contacting schemes.

Using the measured SET pulse widths plotted in Fig. IV-9, the mean SET pulse width ( $\mu$ ) and the standard deviation ( $\sigma$ ) are calculated for each circuit, assuming a

Gaussian distribution of pulse widths. These results are plotted in Fig. IV-14. Additionally, the maximum SET pulse widths from Fig. IV-3 and average SET pulse width from [Ga10] are plotted in the same figure.

Similar to Figs. IV-1, IV-2, and IV-3, the results for TSMC 90 nm dual-well, bulk CMOS process exhibit an inverseley proportional relationship between SET pulse width and percentage of n-well area contacted. This inverseley proportional relationship between pulse width and n-well contact area is a result of the parasitic BJT amplification mechanism as observed previously by [Ol07] [Amus08]. Above 2% of n-well area contacted, the SET pulse width data saturates. Pulse width saturation is the result of the lateral resistive path (R1 in Fig. III-2) in the n-well being the dominant resistive path for charge removal instead of the vertical resistive path [Ol07]. The lateral resistance controls the duration for which the parasitic BJT remains ON and the amount of charge collected at the drain node of the hit transistor.

Further than just having similar trends to the TSMC 90 nm data, the 65 nm, 90 nm, and 130 nm data from [Ga10] plotted in Fig. IV-14 have similar magnitudes to the TSMC 90 nm data. For example, the average values for the 130 nm, 90 nm, and 65 nm [Ga10] data would fall within +1 $\sigma$  of the TSMC 90 nm data with the best example being a comparison between the 65 nm data and the TSMC 90 nm 15.7% circuits. If the 65 nm data and the 15.7% data were shifted to have the same percentage of n-well area contacted, they would overlap each other. Therefore, the similar trends and magnitudes between all data sets in Fig. IV-14 validate the original conclusion from [Ga10] that the pulse width trends observed from different bulk technologies can be explained by the percentage of the n-well area contacted.

Fig. IV-14. Comparison of TSMC 90 nm SET results to [Ga10] SET results for an LET of 58 MeV-cm<sup>2</sup>/mg.

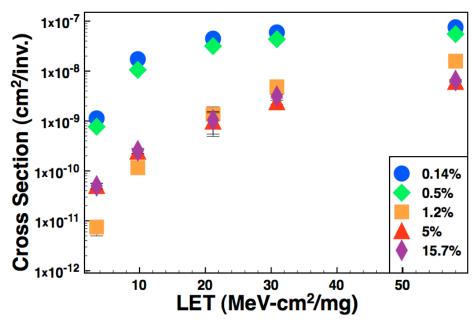

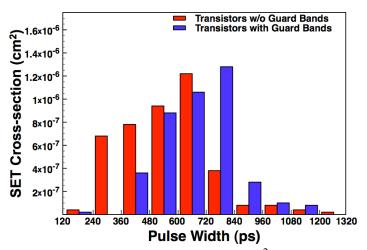

## Analysis of the Cross Section Results

Similar to the SET pulse width results where the 0.14% and 0.5% n-well area contacted circuits had the longest SET pulse widths, those two circuits also had the highest cross sections over all LETs, as seen in Fig. IV-15. The cross section calculated in Fig. IV-15 is calculated by defining an upset as any SET longer than 15 ps [Ga10]. As the plot illustrates, there is little difference in the cross sections among the 1.2%, 5%, and 15.7% n-well area contacted circuits – suggesting there is a limit to the effectiveness of n-well contact area at reducing the cross section.

Fig. IV-15. Cross section versus LET for the five different inverter chain test structures.

Further, regardless of transistor design, Fig. IV-15 shows that the percentage of n-well area contacted influences the sensitive area of the inverters. A result that contradicts the traditional theory that cross section of a logic gate is based entirely on the drain regions of the transistors. In this work, the inverters have identical drain regions, but results show vastly different cross sections; indicating there are additional factors (specifically n-well contact area) that influence the logic gate cross section.

The lower percentage of n-well area contacted allows the n-well to be de-biased more often during an ion strike than the other contacting schemes. De-biasing of the well can result in BJT turn-on and the generation of SETs in the inverter chains. Since n-well contacts also serve to dissipate deposited charge, a reduction in the n-well contact area

also increases the probability that deposited charge will be collected by sensitive junctions and not n-well contacts.

Fig. IV-16 illustrates the relationship between cross section and percentage of n-well area contacted at an LET of 58 MeV-cm<sup>2</sup>/mg. From the data, there is an obvious inversely proportional relationship between the cross section and percentage of n-well area contacted, which matches the relationships seen in Figs. IV-1, IV-2, IV-3, and IV-14. This inversely proportional relationship is a result of parasitic BJT mechanism [Ol07][Amus08][Ahl11]. Therefore, these results suggest that the parasitic BJT is a significant factor in not only determining the pulse width of SETs, but also in determining the sensitive area for a given logic gate.

Fig. IV-16. Cross section for the five TSMC 90 nm inverter chain test structures for an LET of 58 MeV-cm<sup>2</sup>/mg.

#### Conclusion