# SINGLE EVENT EFFECTS IN COMMERCIAL MICROPROCESSORS USING DYNAMIC CIRCUITRY

By

Xiaowei Zhu

# Dissertation

Submitted to the Faculty of the Graduate School of Vanderbilt University in partial fulfillment of the requirements

for the degree of

## DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

May, 2002

Nashville, Tennessee

Approved by:

Prof. Lloyd Massengill

Prof. Bharat Bhuva

Prof. Daniel Fleetwood

Prof. Ronald Schrimpf

Prof. J. Fritz Barnes

# TABLE OF CONTENTS

|       |                                                                                                                            | Page     |

|-------|----------------------------------------------------------------------------------------------------------------------------|----------|

| ACK   | NOWLEDGMENTS                                                                                                               | iii      |

| LIST  | OF TABLES                                                                                                                  | v        |

| LIST  | OF FIGURES                                                                                                                 | vi       |

| Chapt | ter                                                                                                                        |          |

| I.    | INTRODUCTION                                                                                                               | 8        |

| II.   | SOFT ERROR ISSUES IN MICROPROCESSORS                                                                                       | 12       |

|       | Single Event Basics  Dynamic Circuit Operation  Emerging SEE Issue with Technology Development and Current Research Status | 15       |

| III.  | THE ALPHA MICROPROCESSORS UNDER INVESTIGATION                                                                              | 24       |

|       | General Information  Core Combinational Logic Design  Core Latch Design  Cache Design                                      | 27<br>28 |

| IV.   | METHODOLOGY                                                                                                                | 35       |

|       | Computational Method                                                                                                       | 39       |

| V.    | RESULTS AND DISCUSSION                                                                                                     | 46       |

|       | Device Level – Q <sub>crit</sub> and Charge Collection Efficiency                                                          | 47<br>57 |

| VI    | CONCLUSION                                                                                                                 | 65       |

#### **ACKNOWLEDGMENTS**

According to Webster, "acknowledgment" means "to express thanks for". To justifiably acknowledge those individuals who have helped me to reach this major accomplishment in my life, I would need another volume attached to my final thesis.

First I would like to thank my advisor, Dr. Lloyd W. Massengill for his guidance and for being such a good teacher. I am also indebted to Dr. Ron Schrimpf and Dr. Dan Fleetwood for their constant encouragement as well as constructive and insightful comments on this dissertation. I would also like to thank Dr. Bharat Bhuva and Dr. J. Fritz Barnes for serving on my committee, and Dr. Tim Holman for his unselfish support.

I would like to thank Compaq Computer Corporation, Alpha Development, for the opportunity to work with their SER team as an intern, and for providing me with the superb environment at Shrewsbury, Massachusetts. I am deeply indebted to Dr. Norbert Seifert, who not only contributed a great deal to this work, but also continuously encouraged and supported me during and after my stay at Compaq/ADG. I would like to thank my colleagues at Compaq/ADG. Special mention is due to Vinod Ambrose, Manjunath Bhat, Jim Chung, Heinrich Fisher, Ray Hokinson, Norm Leland, Phil Lin, David Moyer, Rob Mueller, Johann Nittmann, Llanda Richardson, Wendy Qin, Yuzhen Tang, Horst Wagner, and Bjorn Zetterlund, Tina Zou.

Deep gratitude is given to Dr. Claude Cirba for his patient support and guidance toward solving many problems encountered with the computer simulations and for his invaluable friendship. I would also like to acknowledge the help and friendship of Dr. Yuanfu Zhao and Dr. Sungchul Lee.

I am grateful to my fellow graduate students in the Vanderbilt Radiation Effects and Reliability Group, who were instrumental in providing such a constructive environment. Of special mention would be Scotter Ball, Hugh Barnaby, Younes Boulghassoul, Quping Hu, Daedra Lohr, Jason Lowe, Jim Felix, Yanfeng Li, Jinhong Liu, Jie Meng, Jayanth Shreedhara, Andrew Sternberg, Kevin Warren, and Hao Xiong. I would like to thank Connie Nichols and Pitsini Monkolkachit, very special friends of mine, who make me feel at home in America.

I would like to offer special thanks to my pingpong and badminton friends who made my graduate study life at Vanderbilt a beautiful memory. Of special mention would be Philippe

Adell, Kitti Attakitmongcol, Lei Guo, Yanfeng Li, Chris Lossin, Jingchun Ma, Yuansheng Yang, Xinhauai Ye, and Tong Zou.

Finally I want to thank my family, especially my mom and my brother, for their continuous support during all the years of my study. To reach this goal in my life would not have been possible without their unconditional love.

# LIST OF TABLES

| Table                                                                       | Page |

|-----------------------------------------------------------------------------|------|

| 1: SIA Roadmap of Microprocessor technology [1]                             | 8    |

| 2: Comparison of dynamic logic and static CMOS logic                        | 17   |

| 3: Probability of an error according to arrival time of the transient pulse | 21   |

| 4: Microprocessor Features [14]                                             | 24   |

| 5: Critical charge of comparison (normalized unit)                          | 50   |

| 6: Summary of simulation results at 20 MHz for nodes shown in Figure 15     | 59   |

| 7: Nomenclature used in Figure 37 [20]                                      | 62   |

# LIST OF FIGURES

| Figure                                                                                                                                                                                         | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1: Microprocessor clock speed predicted by SIA road map of [1]                                                                                                                                 | 9    |

| 2: Single event occurs at PN junction of the semiconductor device, and is modeled as a transformation current pulse at the circuit level                                                       |      |

| 3: Soft error in memory circuits and combinational circuits                                                                                                                                    | 13   |

| 4: Concept of critical charge and window of vulnerability                                                                                                                                      | 14   |

| 5: The basic construction of a dynamic logic gate                                                                                                                                              | 15   |

| 6: Definition of setup and hold time of a latch                                                                                                                                                | 20   |

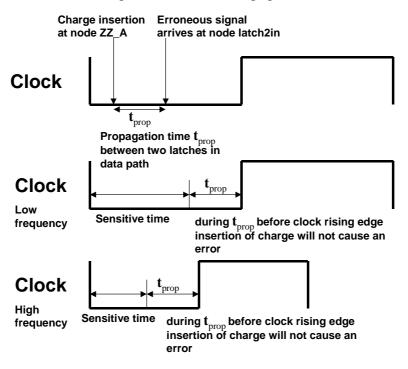

| 7: Schematic of a generic data path consisting of a inverter chain between two latches                                                                                                         | 22   |

| 8: Timing requirement for a voltage glitch occurrence at node S to be latched as a soft error                                                                                                  | 23   |

| 9: 21164 die photo[14]                                                                                                                                                                         | 25   |

| 10: 21264 die photo[14]                                                                                                                                                                        | 26   |

| 11: Dynamic inverter                                                                                                                                                                           | 28   |

| 12: 21164 Latch                                                                                                                                                                                | 29   |

| 13: 21264 Latch with no keeper                                                                                                                                                                 | 30   |

| 14: 21264 Latch with keepers                                                                                                                                                                   | 32   |

| 15: Circuit schematic of the SRAM sensing data-path                                                                                                                                            | 33   |

| 16: The circuit schematic of an SRAM cell                                                                                                                                                      | 34   |

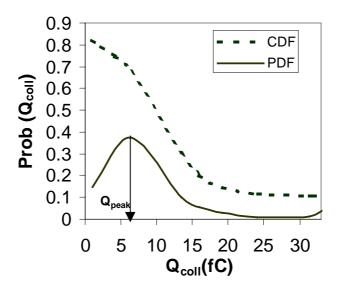

| 17: Probability density function and cumulative density function of collected charge for 5 Months alpha particles[29]                                                                          |      |

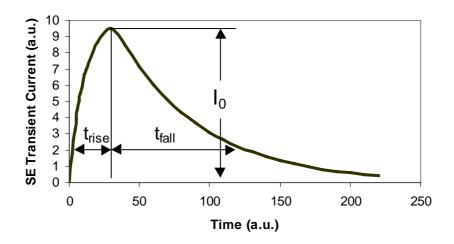

| 18: SE transient current temporal profile for circuit-level simulations                                                                                                                        | 39   |

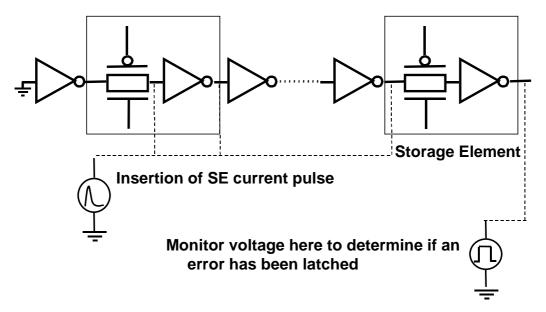

| 19: Simulation setup of evaluating the SE vulnerability of the circuit in SPICE                                                                                                                | 41   |

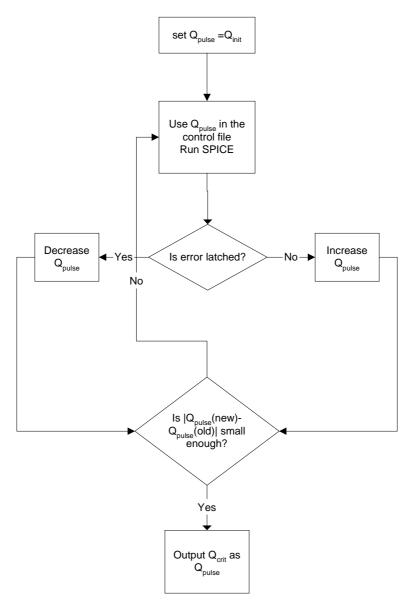

| 20: Flow chart of the simulation method to find the critical charge                                                                                                                            | 42   |

| 21: 21164 Alpha microprocessor with several memory arrays covered with epoxy (six gray rectangles in the middle of the chip) to mask the alpha particle                                        | 44   |

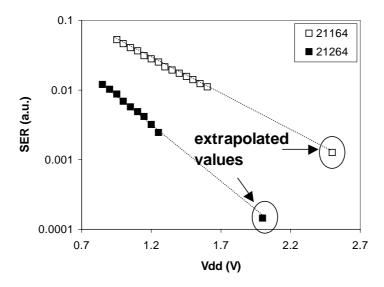

| 22: Measured SER of on-chip cache as a function of operating voltage for two different technologies. Circled values indicate the extrapolated values to the respective nominal supply voltages | 46   |

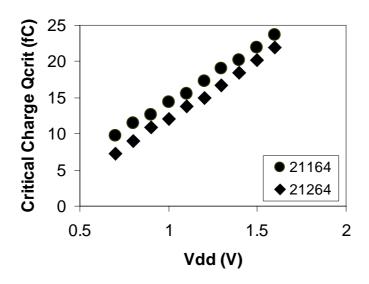

| 23: Simulated critical charge of the SRAM cell for two different technologies                                                                                                                  | 47   |

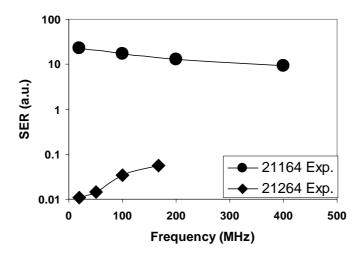

| 24: Experimental accelerated SER of core logic in two generations of Alpha microprocessors                                                                                                     | s49  |

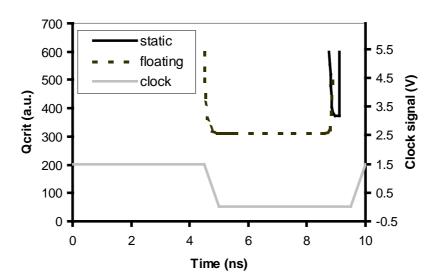

| 25: Simulated critical charges are plotted for two different nodes of the 21164 core logic data-<br>path in one clock cycle                                                | 1 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 26: The WOV decreases with increasing clock frequency, which results in a corresponding decrease in SER                                                                    | 2 |

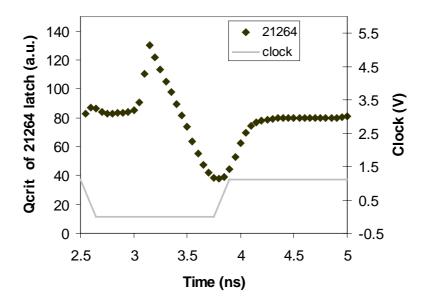

| 27: Simulated critical charge of latch designs in 21264 Alpha microprocessor core logic5                                                                                   | 3 |

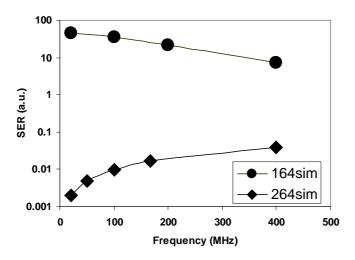

| 28: Computed failure rates are shown as a function of clock frequency for two types of latch designs                                                                       | 4 |

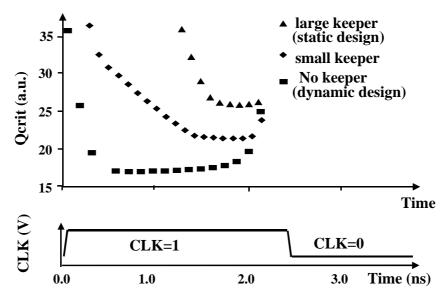

| 29: Simulated critical charge of various keeper designs                                                                                                                    | 5 |

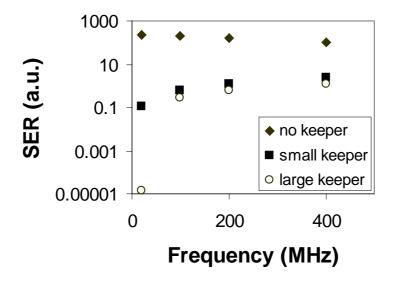

| 30: Computed failure rates are shown as a function of clock frequency for various keeper design                                                                            |   |

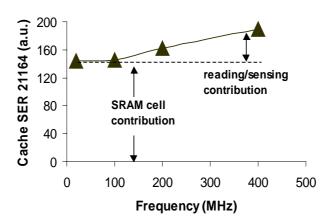

| 31: Experimental accelerated SER as a function of clock frequency for the RETENTION pattern for 21164 Alpha microprocessor                                                 |   |

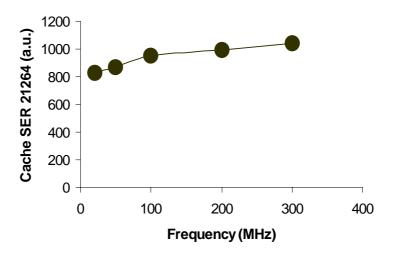

| 32: Experimental accelerated SER as a function of clock frequency for the RETENTION pattern for 21264 Alpha microprocessor                                                 |   |

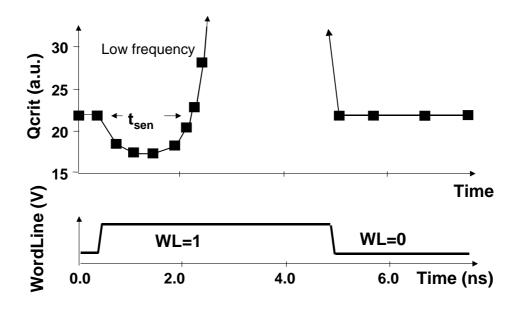

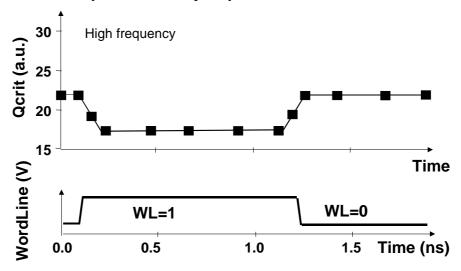

| 33: Simulated critical charge of internal node of SRAM cell under reading/sensing condition at low frequency                                                               | 0 |

| 34: Simulated critical charge of internal node of SRAM cell under reading/sensing condition at high frequency                                                              | 0 |

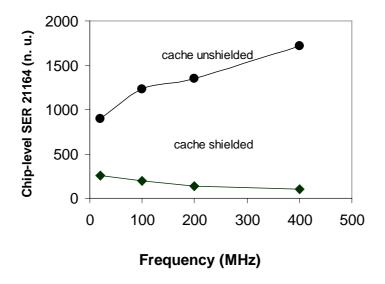

| 35: Experimental accelerated SER of the TOAST pattern run on 21164 Alpha microprocessor is shown as a function of clock frequency with and without memory arrays covered 6 |   |

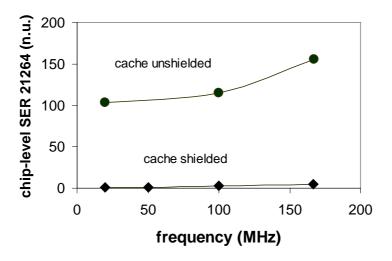

| 36: Experimental accelerated SER of the TOAST pattern run on 21264 Alpha microprocessor is shown as a function of clock frequency with and without memory arrays covered 6 |   |

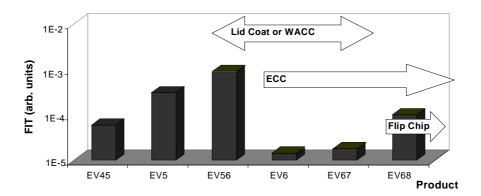

| 37: The FIT rates due to α-particle strikes are plotted for several different Alpha microprocessor generations [21]                                                        |   |

## CHAPTER I

## **INTRODUCTION**

The semiconductor industry has gone through an astounding revolution in the last few decades; the performance and integration density of microprocessors increase exponentially with time due to staggering technical advances in semiconductor fabrication process, circuit design and computer architecture. Table 1 shows the Semiconductor Industry Association roadmap [1] for microprocessor technology. As feature size continues to shrink, more transistors can be packed into the same chip area, therefore the transistor count per chip increases.

Table 1: SIA Roadmap of Microprocessor technology [1]

|                                    |       |       |       | 0     | ,     |      |

|------------------------------------|-------|-------|-------|-------|-------|------|

| Product Year                       | 1997  | 1999  | 2001  | 2003  | 2006  | 2009 |

| Technology<br>Generation           | 250nm | 180nm | 150nm | 130nm | 100nm | 70nm |

| Microprocessor<br>transistors/chip | 11M   | 21M   | 40M   | 76M   | 200M  | 520M |

| Logic<br>transistors/cm²           | 3.7M  | 6.2M  | 10M   | 18M   | 39M   | 84M  |

| NOR Cell Size (µm²)                | 0.6   | 0.3   | 0.22  | 0.15  | 0.08  | 0.04 |

| Nominal Supply<br>Voltage (V)      | 1.8   | 1.5   | 1.2   | 1.0   | 0.9   | 0.6  |

| Gate Delay Metric<br>CV/I (ps)     | 16-17 | 12-13 | 10-12 | 9-10  | 7     | 4-5  |

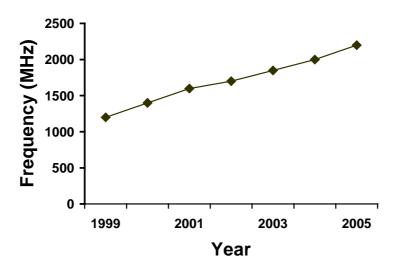

Furthermore, the decreasing gate delay gained by the technology-scaling enables the onchip clock speed to continue to increase. One way to improve the performance of a microprocessor is to increase the operating clock frequency. The demand for higher performance has resulted in clock speeds on the order of several GHz in modern high performance microprocessors, and this trend is forecast to continue in future generations, as is shown in Figure 1 [1].

Figure 1: Microprocessor clock speed predicted by SIA road map of [1]

As feature sizes and operating voltages of electronic devices are continually reduced to satisfy the demand for higher density of integration and lower power consumption, the sensitivity of systems using these devices often increases. Radiation-induced charges can corrupt the information (presence or absence of pre-determined charge at circuit nodes) stored in a circuit. Because this type of error is nonpermanent, it is called soft error. This phenomenon is also called single event, since it is a localized effect caused by a single particle. The critical charge  $Q_c$ , often approximated as the product of the node capacitance  $C_{node}$  and the operating voltage  $V_{DD}$ , has been reduced to levels such that circuits are now vulnerable to low energy, ground based ions [2]. Radiation-induced reliability issues are no longer the sole concern of space circuit and device designers. Terrestrial cosmic rays and their interaction with electrical systems are attracting more and more attention. Single event effects (SEEs) are taking a prominent position in the mainstream integrated circuit industry. Many commercial manufacturers are coming to grips with the problem as a key reliability issue.

Advancement from one microprocessor generation to the next impacts reliability at the technology/device level, circuit level, and system level; therefore, the broad objective of this work is to study the impact of the Alpha<sup>1</sup> microprocessor maturation between two generations on soft error rates (SER) at three levels. At the device level, analysis is done on the error rate per information bit to weigh the relative impact of critical charge and charge collection efficiency.

9

\_

<sup>&</sup>lt;sup>1</sup> Compaq is registered in the U.S. Patent and Trademark Office. Alpha is a trademark of Compaq Computer Corporation.

Contrary to many researchers' beliefs that SER will increase in future technologies, the results obtained in this work indicate that on the device level the SER per on-chip memory cell decreases, rather than increases. At the circuit level, the core logic SER of these two generations is compared to analyze the impact of different circuit design techniques. At the system level, SER frequency trends are studied in major microprocessor components, such as the cache and core logic. For the 21164 Alpha core logic using dynamic transmission gate latch, unexpectedly the SER decreases with the clock speed. This trend is reported for the first time in this work and is well explained by the simulation analysis. The influence of architectural decisions such as error correction codes (ECC) on the chip-level SER is also explored. Through the comparison, the dominant SER contribution from the cache over the core logic found in this work justifies the extra cost in using error correction circuitry to protect the on chip cache. This result reinforces the previous observation by Howard et al.[3]. Both the experimental and computational methods are used in this work. Accelerated soft error testing was performed by direct exposure to Am241 foils while a program was run on the Alpha microprocessors with a Schlumberger ITS9000, IX tester. The SER was computed using the results obtained from the circuit level simulations.

The bulk of this work was done at Compaq Computer Corporation Alpha Development Group (ADG) at Shrewsbury, Massachusetts, during my internship in 2001. Some of the analysis described and conclusions drawn in this dissertation are a result of collaborative research efforts with the SER team at Compaq/ADG; however, they do not necessarily reflect the assessment methodology of Compaq/ADG.

This thesis has been organized as follows. Chapter 2 introduces the basic concepts related to the single-event upset (SEU) phenomenon and the basic operation of dynamic circuits, briefly reviews the technology development. Then the emerging soft error (SE) issues in microprocessors as technology advances are discussed, and the related work previously done in this area are presented. Chapter 3 discusses two generations of the Alpha microprocessor family under investigation in this work, briefly reviewing the circuit styles used in these microprocessors and the architecture of the microprocessor from the SE perspective. Chapter 4 explains the method and techniques used to study the problem, both experimentally and computationally. The testing setup and test patterns during the test are presented in detail. In addition, the simulation technique and the single particle hit modeling method used are described, and the SER computation equation is derived and the parameters used in the equation

and their justification are given. Chapter 5 presents experimental data and simulation analysis to explain the experimental observations. The results are organized to address SEE at the device, circuit and system levels. Chapter 6 summarizes all the key findings and concludes this work.

#### CHAPTER II

#### SOFT ERROR ISSUES IN MICROPROCESSORS

This chapter contains background information about single event effects in microprocessors. As technology evolves to deliver higher performance microprocessors, dynamic circuits are gaining increasing popularity thanks to its high speed and low area cost. First, the basic concepts and terms related to SEE are introduced. Then, the basic operation of dynamic circuitry is briefly reviewed. Finally, the emerging soft error issues associated with technology development are discussed, along with the related work previously done in this area.

# Single Event Basics

Single events and soft errors in electrical systems caused by cosmic rays were first observed by Binder et al. [4] in the bipolar flip-flop circuits of a space-borne communication system in 1975. Soon after this observation in the space environment, May and Wood [5] experimentally observed soft errors in dynamic random access memory (DRAM) operating in the terrestrial environment. To evaluate the vulnerability of integrated circuits to radiation-induced soft errors or single event upsets (SEU) accurately, all sources of radiation must be accounted for. The primary sources of ionizing particles for terrestrial microelectronics include alpha particles from radioisotopic impurities in the packaging material and neutron reaction products induced by cosmic rays [6]. Although used interchangeably in the literature, in this work, single event upset means a corrupted electrical state at any storage node, while a soft error is counted only when the application run on the system misinterprets the corrupted state as valid information.

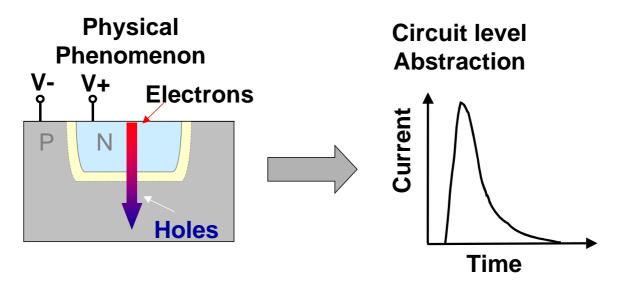

SEE occur when a single ionizing particle traverses semiconductor device material generating electron hole pairs along its track. Illustrated in Figure 2, A significant fraction of these carriers can be separated by the electric field in the depletion region and result in a transient current pulse at a circuit node [7]. If a single particle hits the memory element of the circuit and the induced current pulse magnitude and duration are sufficiently large, the feedback mechanism in the circuit memory element will cause a change in the logic state of the memory cell.

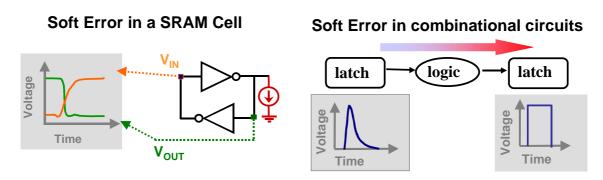

Figure 2: Single event occurs at PN junction of the semiconductor device, and is modeled as a transient current pulse at the circuit level

On the other hand, a single event occurring on combinational circuit nodes will lead to a transient voltage glitch. This voltage glitch can propagate through the logic gates and be latched into a memory element provided that the timing of the arrival and characteristics meet certain criteria. The criteria have been discussed by Baze [8] and Siehl et al. [9], and will be presented in detail later. These two error mechanisms in the circuits are depicted in Figure 3. Since the logic information loss at the circuit nodes due to single events is not permanent and can be corrected, the induced error is called a soft error (SE).

Figure 3: Soft error in memory circuits and combinational circuits

The vulnerability of a circuit is usually indicated by its critical charge ( $Q_{crit}$ ), defined as the minimum amount of single-event-induced charge needed at a sensitive node to cause a circuit upset. A more detailed discussion about the concept of critical charge has been performed by Massengill [10] and Dodd and Sexton [11]. Because the SER sensitivity of a circuit may vary at

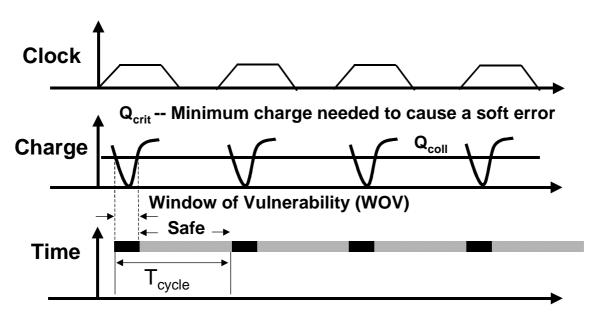

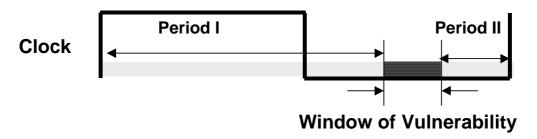

different clock phases, the critical charge of a circuit node is not necessarily constant, and may be a function of time. Another important quantity that characterizes the susceptibility of a memory cell to corruption of its logic state is the window of vulnerability (WOV), defined as the time during which a logic element is sensitive to SEU [12]. These basic concepts are best illustrated with an example shown in Figure 4.  $Q_{crit}$  for a certain circuit node can be a function of time. In the example,  $Q_{crit}(t)$  is the lowest if the single event hit occurs on this node around a clock rising edge. If the collected charge ( $Q_{coll}$ ) caused by a certain particle is higher than  $Q_{crit}(t)$ , a soft error would occur. Therefore, the period of time marked in dark color is the sensitive time window for this circuit node and this collected charge, i.e., the window of vulnerability. As indicated, the region in light-gray is "SE-safe" since the condition  $Q_{coll} < Q_{crit}(t)$  holds. The larger the window of vulnerability and the lower  $Q_{crit}$ , the higher the soft-error rate (SER). Intuitively, the relation between window of vulnerability and clock cycle duration determines the frequency dependence of SER.

Figure 4: Concept of critical charge and window of vulnerability

Since the critical charge scales with shrinking device sizes and supply voltages, the deep submicron technologies are generally more sensitive than the old technologies. In order to reduce cost and improve performance, dynamic circuits are widely used. The SE vulnerability of dynamic circuits is closely related to its unique way of operation.

# **Dynamic Circuit Operation**

Kang and Leblebici [13] provide more details on the design and issues in dynamic circuits. In this section, a brief review emphasizing issues related to SEU will be presented. Conventional static logic circuits for CMOS technologies use high and low voltages to indicate a logic state 1 or a logic state 0 at the output node. The charge and discharge of the output capacitance is generally carried out by p-channel and n-channel devices, respectively. With hole mobility being smaller than electron mobility, p-channel devices are often larger than n-channel devices. The presence of the large p-channel devices increases capacitive load at the output node of the previous gate resulting in higher power requirements and slower operating speeds.

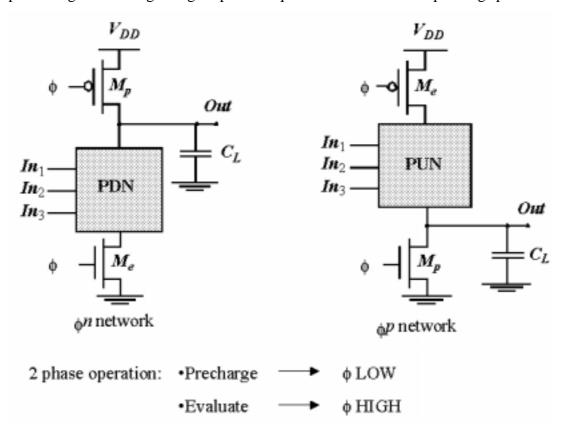

Figure 5: The basic construction of a dynamic logic gate

The basic construction of the dynamic logic circuits is plotted in Figure 5. For dynamic logic circuits, the logic gate operation is divided into two distinct phases of operation: pre-charge phase and evaluation phase. During the pre-charge phase, the output node of a logic gate is charged to a high logic voltage. During the evaluation phase, this output node voltage is either left at a logic state high or discharged to a logic state low. Since input evaluation only

necessitates a capacitance discharge, p-channel devices do not take part in logic function evaluation. Therefore, both the gate fan-in and fan-out capacitance are reduced. Moreover, in a dynamic logic circuit, a single p-type device with high current driving capability replaces the parallel combination of PMOS devices in its equivalents static counterpart. This change reduces the layout area, which results in lower inter-connect capacitance, further increasing the speed of the circuit. The single PMOS device always turns on in the pre-charge phase, and can quickly charge the output capacitance if the NMOS-network is off during evaluation. Furthermore, the switching point of the dynamic gate is set by the threshold voltage of the NMOS device. If the timing of the inputs is such that they are not asserted until after the pre-charge clock has been deasserted, there is no crossover current during the output transition. Due to these reasons dynamic logic is usually much faster than its complementary equivalents in static logic [14].

The basic construction of an N-type dynamic logic gate and a P-type dynamic logic gate are shown in Figure 5. In an N-type dynamic logic gate, the pull-down network (PDN) is stacked with a clocked NMOS transistor. On the other hand, in a P-type dynamic logic gate, the pull-up network (PUN) is stacked with a clocked PMOS transistor. The pre-charge and evaluation phases of this circuit are controlled by the clock.

# **Pre-charge**

In an N-dynamic gate, when the clock is low (CLK = 0), the output node Out is precharged to the supply voltage ( $V_{DD}$ ). During this time, the evaluation NMOS transistor  $M_e$  is off. In a P-dynamic gate, when CLK = 1, the output node Out is pre-discharged to the ground (GND). During this time, the evaluation PMOS transistor  $M_e$  is off.

### **Evaluation**

In an N-dynamic gate, when CLK = 1, the pre-charge transistor  $M_p$  is off, and the evaluation transistor  $M_e$  is turned on. The output node Out is conditionally discharged based on the PDN. In a P-dynamic gate, when CLK = 0, the pre-charge transistor  $M_p$  is off, and the evaluation transistor  $M_e$  is turned on. The output node Out is conditionally charged based on the PUN.

The logic state of output node *Out* depends on the amount of charge retained on this capacitive node. If the charge on this node is lost in the evaluation phase, there is no path to recharge the node.

A comparison of some of the important properties of dynamic logic and static CMOS logic gates is shown in Table 2.

Table 2: Comparison of dynamic logic and static CMOS logic

| Circuit Type      | Device count    | static power | Comments   |

|-------------------|-----------------|--------------|------------|

|                   | (a fan-in of N) | dissipation  |            |

| static CMOS       | 2N              | N            |            |

| Dynamic-logic N+2 |                 | N            | need clock |

Dynamic logic occupies less chip area thanks to a reduced number of transistors per logic function when compared to static CMOS; as a result, it is generally faster due to smaller parasitic capacitors. In addition, dynamic gates do not have short circuit current, and all the current through the PDN or PUN goes into charging and discharging the load capacitance. No static current path exists between  $V_{DD}$  and GND in either phase; therefore, dynamic logic only consumes dynamic power. By contrast, there is a flow of current from  $V_{DD}$  to GND when the static gates are switching states, at which time both the PMOS and NMOS transistor are ON simultaneously.

During the evaluation phase, the PDN of a dynamic inverter starts to conduct when the input signal exceeds the threshold voltage ( $V_T$ ) of the NMOS pull-down transistor. Therefore, it is reasonable to set the switching threshold ( $V_M$ ) the gate to  $V_T$ . In addition,  $V_{IH}$ , the lowest acceptable high voltage representing logic "1", and  $V_{IL}$ , the highest acceptable low voltage representing logic "0", can be also approximated by  $V_T$ . Therefore, the noise margin for logic "0" is rather low ( $=V_T$ ).

During the evaluation phase of dynamic logic circuit operation, the logic function of the output node relies on capacitive charge storage. As a result, the output node in this time period is very sensitive to single event upset (SEU). There can be no transition from '0' to '1', because the PMOS network is OFF during evaluation. Therefore, no regenerative mechanism exists during the evaluation phase.

For the above two reasons, the output node is extremely vulnerable to single events during the evaluation phase. This high degree of sensitivity to SE exhibited by dynamic circuitry make them unattractive for the space-based applications. However, cost efficiency and speed benefits of dynamic circuitry earn their popularity in the high-performance state-of-art microprocessors.

# Emerging SEE Issue with Technology Development and Current Research Status

It is generally believed that the SE susceptibility increases sharply with device downscaling for both memory and logic circuits; thus the soft error rates have become an increasingly important reliability challenge. Single event effects (SEEs) are becoming a more important reliability issue in the commercial semiconductor industry. Intel not only started testing for alpha-induced soft errors in 0.18 µm logic designs, but also is anticipating the development of a strategy for hardening to terrestrial neutron SEEs [15]. IBM started the investigation of SER issue in 1978, and went through several years of research to verify its magnitude. Nowadays, SER study has become a significant factor in IBM's efforts toward improved product reliability [7]. In addition, as the demand for higher performance in space borne systems opens the door for smaller and faster commercial chips, it is beneficial to understand the SER trend with the technology scaling. In the discussion of the coming challenges in microarchitecture, Ronen et al. [16] claim the SER susceptibility increases by 43% per generation. Karnik et al. [17] predict from their study on the SER of the static latch built in 0.18 µm CMOS technology subjected to accelerated neutron beam that the neutron-induced SER is likely to stay constant for future technologies if the supply voltage scales only by 0.8x. However, a study on several SRAM technology generations conducted by Hareland et al. indicates that SER is reducing on a per bit basis for the future technologies. However, in these studies the trend in the susceptibilities of core logic and memory cells have only been investigated separately, and the question of the overall SER of a microprocessor (which is a combination of both contributions) has not been addressed. The goal of this study is to examine the SEE in the commercial state-of-the-art microprocessors under the operational condition, and investigate the impact of scaling at the device, circuit and system levels.

There are two means to improve the performance of the microprocessors, better electrical properties and higher density. The geometric device scaling helps the circuit speed by reducing

the nodal capacitance; at the same time, the supply voltage decreases in order to keep the electrical field reasonably small to avoid the deteriorative long term device characteristics. This trend results in a reduced critical charge. On the other hand, improvements in the fabrication process give the device designers the flexibility to tailor the device structure. Usually the charge collection efficiency is also reduced with the process scaling due to less diffusion area and higher doping level. It remains an open question as to which one of these two competing effects dominates at the device level.

In order to take full advantage of the process revolution and achieve the optimal performance, microprocessor design occurs in parallel with the manufacturing process development. This is the case for the development of the Alpha microprocessor [14]. The concurrent design means the concurrent change in both the process and circuit techniques. Obviously the influence of the circuit construction and configuration on the SER can not be ignored.

Combinational circuits are the basic building blocks of all digital systems. The same logic function can be implemented in various ways according to the performance or cost consideration for the system. The fact that combinational circuits contain non-arrayed logic block with different vulnerabilities to ion-induced perturbation complicates the analysis, since the regularity and vulnerability assumptions on which the analysis of memory circuits are based do not apply.

Digital ICs can be divided into two types of circuit blocks: latches (registers) and combinational blocks. Latches incorporate feedback paths to store data; combinational blocks achieve the logic function of the input data. The manifestation of a single ion strike at the circuit level is a transient voltage pulse. Due to the memory-less feature of combinational blocks, the "hit" nodes always return to their original voltage after a certain time. If the next stage is also a combinational block, the erroneous transient voltage, instead of being stored in a latch, may propagate to the next stage, until either latched into a register or attenuated.

In order for a transient pulse to be latched as an error in a register, three conditions have to be met, as proposed by Kaul et al. [18]. First, there must exist a sensitive path from the hit node to a register for this pulse to propagate. For example, consider a NAND gate. In NAND logic, logic '0' is the determining force, i.e., as long as one of the inputs of NAND logic is '0', the output will be logic '1' regardless of the state of other inputs. Therefore, a sensitive path exists for an input to the output only when all other inputs are '1' for NAND logic.

Second, the pulse must have sufficient amplitude and width when it arrives at a register if it does make its way there. The sensitive path from the 'hit' node to the register acts as a filter: it filters out the weak and narrow transient pulses, and allows the strong and wide transient pulses to pass. Intuitively, the pulse shape arriving at the register depends on the original pulse shape, the length of the sensitive path, and the temporal characteristics of the sensitive path.

Third, a pulse has to arrive at the right time to be latched into the register. As the circuits are usually synchronized by a clock signal, the SE transient pulse has to arrive in the 'sensitive time' or 'vulnerable window' to cause an error in the register. The term 'sensitive time' and 'vulnerable window' are interchangeable and are tightly related to the 'set-up and hold time' of the register.

Analysis of the first condition can be done in SPICE in a straightforward manner, while analysis of the second and third conditions is more involved. The general guidelines can be found the work on attenuation of single event induced pulses in CMOS combinational logic by Base and Buchner [8]. A transient voltage pulse caused by a single particle with amplitude less than the switching threshold voltage of the logic gate cannot propagate to the next stage. A pulse with sufficient amplitude has to last long enough to propagate through the gate. If the width of the pulse is greater than the logic transition time, the pulse will propagate through the gate without attenuation. If the width of the pulse is smaller than half the transition time, it will terminate. The pulses with width in the range between these two values will propagate with attenuation.

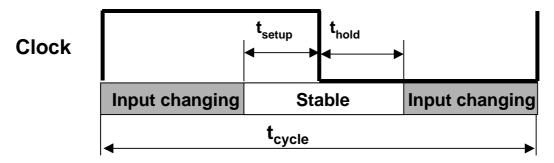

If changes on the input violate either setup or hold time, correct latch operation is not guarenteed

Figure 6: Definition of setup and hold time of a latch

The speed of combinational circuits and the distance from the hit node to the register are important parameters for the SE vulnerability analysis of the combinational circuit. The slower

the gate switches, the more stages an error signal has to propagate through to reach a register, and the lesser the possibility for the erroneous signal to lead to an upset.

Each synchronized input has a setup and hold time specification with respect to clock input. Illustrated in Figure 6, setup time is the amount of time the synchronous input has to be stable before the active edge of the clock signal. Hold time is defined [13] as the amount of time the synchronous input has to be stable after the arrival of the active edge of the clock signal.

In order for an SE induced transient voltage pulse to be latched into an edge-triggered register, it not only has to arrive at the right time (around the active clock edge), but also it has to be above the switching threshold voltage of the latch during the setup time and hold time of the latch. The probability that the transient pulse arrives at a time so as to cause an error is shown in Table 3, as proposed by Holland et al. [19].

Table 3: Probability of an error according to arrival time of the transient pulse

| Temporal condition                             | Probability of an error                         |

|------------------------------------------------|-------------------------------------------------|

| For transient pulse width <t<sub>clock</t<sub> | $\frac{t_{set} + t_{pw} + t_{hold}}{t_{clock}}$ |

| For transient pulse width >=t <sub>clock</sub> | 1.0                                             |

In Table 3,  $t_{pw}$  is the pulse width of the upset, and  $t_{set}$  and  $t_{hold}$  are the setup and hold time of the register, and  $t_{clock}$  is the period of clock signal for the register. These parameters are illustrated in Figure 6.

Analogous to the sensitive volume in a device, the time period from the beginning of the setup time to the end of the hold time of a register is called 'sensitive time' or 'vulnerable window', because only during this time the erroneous signal has a probability of being latched.

The above analyses suggest that frequency is an important parameter in the SE vulnerability analysis of the circuits, since it is impossible to compare the SE vulnerability of different circuit design styles without specifying their operating frequency. Therefore, the frequency dependence of SER is an issue on both the circuit level and system level.

In static SEU testing of memories such as SRAM's, a test pattern is written into the entire memory beforehand, and serves as a reference for determining the number of SEU's after irradiation with ions of predetermined fluence and linear energy transfer (LET). The upsets found from this kind of static measurement are not affected by clock frequency and thus are

called asynchronous [12] due to their relative insensitivity to the event's timing with respect to the microprocessor system clock [12]. On the other hand, the soft error rate (SER) of combinational logic is dependent on cycle time and consequently referred to as synchronous [18].

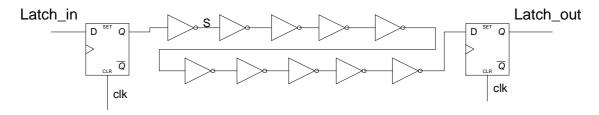

Figure 7: Schematic of a generic data path consisting of a inverter chain between two latches

For example, assuming a single particle hitting the circuit node S in the data path shown in Figure 7, the voltage glitch caused by the single event has to have sufficient amplitude and width in order to propagate through the inverter chain. In addition, in order for an error to be latched in the second latch, the voltage glitch has to arrive at a definite time prior to the clock edge and persist long enough to meet the setup and hold time requirement of the latch. Figure 8 illustrates the timing requirement for a voltage glitch at node S to be latched at the second latch as an error. Usually the single-event-induced transient voltage waveforms have a short rise time of about 50 ps and a fall time of several hundreds of ps. If an ion strikes node S during time period I, the transient voltage pulse seen at the input of the second latch will have decayed by the time of clock transition. On the other hand, if an ion strikes node S during time period II, the clock will have already transitioned when the transient voltage pulse arrives at the second latch after propagating through the inverter chain. In this example, the window of vulnerability of node S is defined with respect to the clock cycle. Therefore, we will expect SER arising from ion strikes at node S to be proportional to the clock speed of the circuit [12].

Buchner et al. have performed substantial work in studying the frequency dependency of logic circuits. They conclude that 1) the soft error rate is independent of the frequency in latch circuits when the setup and hold time is much less than clock period; 2) the soft error rate increases linearly with the operating clock frequency in the combinational circuits; 3) Soft errors in latch circuits dominate in present day technologies, but the errors in the combinational circuits will dominate in future technologies [12]. The purpose of the SER frequency dependence in this

work is two-folds. First, the dynamic latches used in the Alpha microprocessors are quite different from the static latch studied by Buchner et al. Second, as circuit operating frequency approaches GHz, the duration of the transient voltage pulse caused by a SE is comparable to the clock period. It will be advantageous to revisit these early conclusions.

Figure 8: Timing requirement for a voltage glitch occurrence at node S to be latched as a soft error

The above analysis indicates that the overall SER trend with technology generations is complicated by the device and circuit level considerations. The final FIT (failure in time: 1 FIT equals 1 soft error in 10<sup>9</sup> hours of operation) rates of the system are further influenced by the architectural and packaging decisions, and depends strongly on the environment. ECC for the cache was introduced into the Alpha microprocessor in its third generation version, the 21264 chips. For both the 21164 and 21264 Alpha microprocessors, a lid coat or a wirebond attached chip capacitor (WACC) was placed in between the die and the package. The flip chip packaging technology is used in the 21264 Alpha microprocessors built in 0.18 mm CMOS technology. Flip chip microelectronic assembly is the direct electrical connection of face-down (hence, "flipped") electronic components onto substrates, circuit boards, or carriers, by means of conductive bumps on the chip bond pads. Since the flux of the alpha particle increases due to the lead present in the bumps, one would expect a negative impact from the flip chip on the overall chip level SER.

This chapter provides the background information about the SER issues related to the modern commercial microprocessors using dynamic circuits. In the next chapter, the specific dynamic design used in the Alpha microprocessors under the investigation will be discussed.

## **CHAPTER III**

## THE ALPHA MICROPROCESSORS UNDER INVESTIGATION

# **General Information**

DIGITAL Equipment Corporation introduced the Alpha 21064 in 1992, the highest performance microprocessor in the industry at that time. Since then Alpha microprocessors have achieved industry-leading performance through process advancements, architectural improvements, and aggressive circuit design techniques [14][20]. The clock frequencies of Alpha microprocessors increased from 150 MHz to more than 1 GHz over four generations from the early 1990's to the present. In addition, Alpha microprocessor design has had reliability as a primary concern. The key parameters for the two generations of Alpha microprocessors under this investigation are listed in Table 4.

**Table 4: Microprocessor Features [14]**

|                             | 21164     | 21264     |

|-----------------------------|-----------|-----------|

| Transistor count (million)  | 9.3       | 15.2      |

| Die size (mm <sup>2</sup> ) | 18.1×16.5 | 16.7×18.8 |

| Process Technology          | 0.35 μm   | 0.25 μm   |

| Power supply (V)            | 2.5       | 2.0       |

| Power dissipation (W)       | 50        | 72        |

| Target Design frequency     | 300       | 600       |

| Typical gate delay/cycle    | 14        | 12        |

| On-chip cache               | 8KB L1-I  | 64KB L1-I |

|                             | 8KB L1-D  | 64KB L1-D |

|                             | 96KB L2   |           |

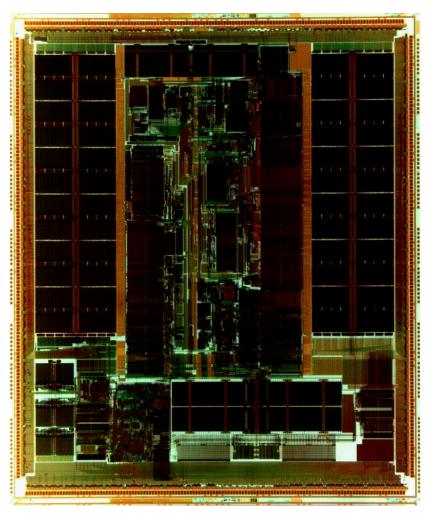

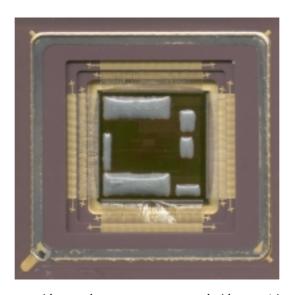

Figure 9: 21164 die photo[14]

The 21164, shown in Figure 9, is the second generation of Alpha architecture. It was designed to operate at 300 MHz in a 0.5  $\mu$ m n-well CMOS process using a 3.3 V supply, and it dissipates 50 W. The number of gate delays per cycle was reduced from 16 in the first generation to 14 to provide an additional 10% reduction in cycle time beyond process scaling. The die is roughly 3.0 cm<sup>2</sup> and contains a total of 9.3 million transistors. The non-cache transistor count is tripled from the previous generation design to 2.5 million. Although originally designed to operate at 300 MHz, migration of this design to a 0.35  $\mu$ m process has allowed the operating frequency to be increased to 600 MHz.

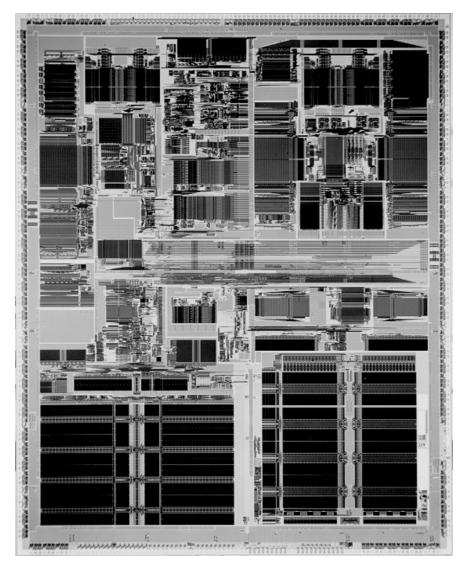

Figure 10: 21264 die photo[14]

The 21264, shown in Figure 10, is the third-generation Alpha microprocessor. It is fabricated in a 0.25 µm n-well CMOS process, and is targeted to operate at 600 MHz. The number of gate delays per cycle has been further reduced to 12, again providing an additional 10% reduction in cycle time relative to the previous design. A nominal supply voltage of 2.2 V is used to limit power dissipation to an estimated 72 W, but the design and process can operate reliably up to 2.5 V. The die is 3.1 cm², and contains 15.2 million transistors. The non-cache transistor count is more than double that of the 21164.

As process technology advances, better electrical properties and higher device densities, gained from the process scaling, improve the performance of the microprocessors via two means. First, the speed of the circuit is directly related to the time to charge and discharge the nodal

capacitance, which was reduced by shrinking transistor size and interconnects. Second, geometric scaling enables more circuitry to occupy the same die area, thus offering the designer flexibility to enhance the performance.

In order to achieve higher performance than offered by the above-mentioned process scaling in each generation, full-custom circuit design methodologies have been used universally by the Alpha microprocessor design teams. Fewer than 10% of the circuits were designed using automatic synthesis approaches. Therefore, a wide range of circuit styles including both the conventional complementary static CMOS logic and dynamic logic can be found in these microprocessors [14]. As a result, it is important to identify the circuit type that dominates the SE response of the core logic.

# Core Combinational Logic Design

In the core logic of the Alpha microprocessors a wide range of circuit styles have been implemented including conventional complementary CMOS logic, and single- and dual-rail dynamic logic [21]. Dynamic circuits are one of the most commonly used circuit styles due to the advantages discussed earlier; however, dynamic circuits are very sensitive to noise, and require very careful design and extensive verification to ensure functionality.

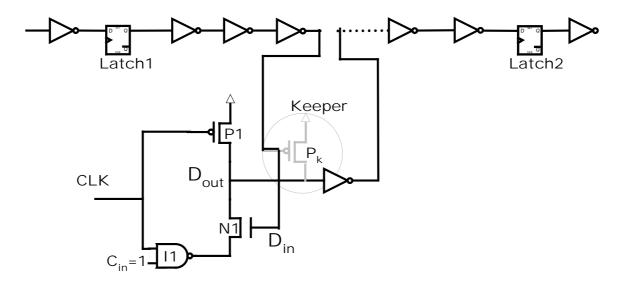

Figure 11 shows a simple data path consisting of an inverter chain between two latches. The data path itself was not a part of the Alpha microprocessor design, but the circuit elements such as inverters and latches are extracted from the actual implementation to represent the general circuit structure in the core logic. All inverters in the chain are static except one. Controlled by the clock signal CLK, transistors P1 and N1 form a dynamic inverter between the nodes D<sub>in</sub> and D<sub>out</sub>. This conditional dynamic inverter is commonly used in both generations of the Alpha microprocessor.

Figure 11: Dynamic inverter

At clock low phase, the output node of the dynamic inverter  $D_{out}$  is pre-charged to the logic state high by P1. The evaluation of this dynamic inverter, however, is activated only when the logic value of  $C_{in}$  is "1" at clock high phase. Under this condition, the output of the NAND gate I1 supplies a virtual ground to the NMOS device N1.

If  $D_{in}$  is low during the evaluation phase, both P1 and N1 are off, and  $D_{out}$  remains precharged to logic high value. However,  $D_{out}$  is, in this condition, very vulnerable to noise, because it can easily lose its logic high value from charge leakage. A weak pull-up device  $P_k$ , also known as a keeper device, drawn in gray in Figure 11, provides a feedback mechanism from  $D_{out}$  to  $D_{in}$ , efficiently preventing charge leakage. Whenever the voltage on  $D_{out}$  drops,  $P_k$  is turned on, and restores the charge on  $D_{out}$ .

## Core Latch Design

Latches not only constitute an important implementation issue in the microprocessor circuit design strategy, but also have direct impact on the SER contribution from core logic, since all the single-events originated from combinational circuits have to be latched into a memory element to be observed. Because latch design is closely related to clocking strategy and has great influence on performance, high speed has been the primary goal of the latch design in each generation of the Alpha microprocessor. The high clock frequencies and small number of gate delays available per cycle on Alpha implementations have made low-latency latch design essential.

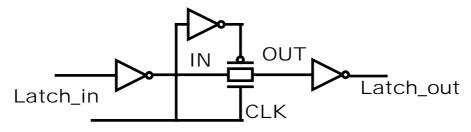

The Alpha 21164 uses the dynamic CMOS transmission gate latch family shown in Figure 12. This is also a level-sensitive latch that is transparent when CLK is high. When CLK goes low, the data are capacitively stored on node OUT and blocked by the pass gate. Because the charge retained on the node capacitance leaks away with time, this latch also requires a minimum operating frequency. The capability of embedding logic functions directly in the latch helps reduce the number of gate delays per cycle. For this transmission gate latch, the first inverter can simply be converted into a logic gate to incorporate logic. This latch requires true and complementary clock signals, one of which is generated locally. Because CLK is not in the input stack, the resulting low fan-in and clock load is an important performance advantage for the transmission gate latch. In addition, the delay and edge rate of the local clock signal are under good control because the inverter that generates the local clock for each latch type is custom designed. However, this inverter delays the clocking of the latch by one gate delay after the global clock transitions. Therefore, when the preceding latch opens with the global clock transition and when the succeeding latch remains closed due to that one gate delay, the input of the preceding latch may race through. In order to minimize the possibility of data race-through, the utilization of these latches comes with one design constraint: at least one minimum logic delay element is required between all latches [14].

Figure 12: 21164 Latch

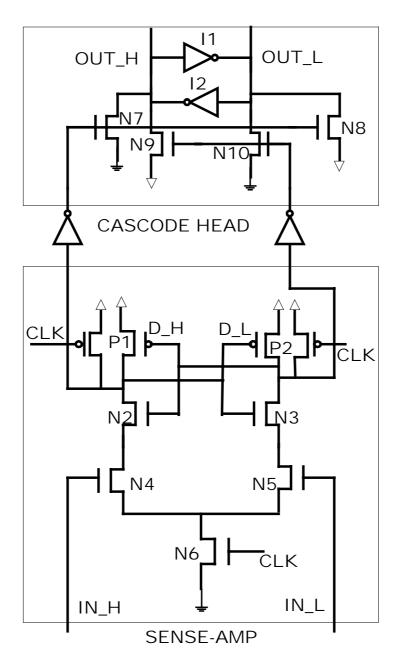

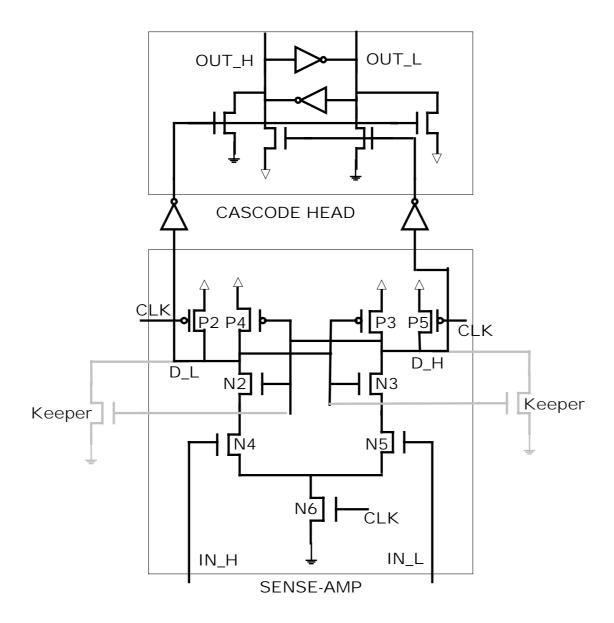

Variations of the edge-triggered latch (or flip-flop) are used as the primary storage element of the third generation Alpha microprocessor; one version is shown in Figure 13. This CMOS differential sense amplifier latch consists of two stages: a sense amplifier and a cascode header. It is static for pre-charged inputs, or can be made static by the addition of weak pull-down devices within the latch. When the nodes D\_H and D\_L are pre-charged to a high state during the low clock phase, the NMOS push-pull pairs in the cascode header are off. Therefore, the sense amplifier and cascode header are de-coupled at this phase, and the state of the latch is maintained by the cross-coupled inverters. The evaluation phase starts on the rising edge of the

clock cycle. As CLK rises, the input data are sampled at IN\_H and IN\_L. As a result, the NFET stack gated by the higher input voltage discharges. Based on the input values IN\_H and IN\_L, either D\_H or D\_L will transition low. Therefore, one of the NMOS push-pull pairs is activated and new content is written into the cascode header.

Figure 13: 21264 Latch with no keeper

Once the cross-coupled NFETs and PFETs lock the latch into the evaluated state, further changes on the inputs will not affect the latch content. Therefore, the hold time of this type of

latch depends on the speed at which the amplifier responds to a voltage difference at its inputs, and can be arbitrarily reduced by increasing the driving ability of the NMOS device N6. However, reversion of the input values at this moment will leave D\_H and D\_L no path to ground. There are two ways to solve this problem. The first one is to use the pre-charged inputs; since any change on the inputs will be preceded by the pre-charged high values, no reversion of the inputs will occur. The second solution is to add two weak pull-down devices, i.e., keepers, to the latch at D\_H and D\_L, as shown in Figure 14. Because the keepers provide paths from D\_H and D\_L to ground, at no time are D\_H and D\_L floating.

The amplifier-based latch exhibits excellent properties of low latency and arbitrarily small hold time. However, it suffers from relatively high power dissipation due to its complementary dual-rail operation. Regardless of the previous state of the flip-flop, one or the other of the complementary nodes of its first two stages will always switch twice per cycle. Moreover, the amplifier-based latch needs both the data and its complements as inputs. Consequently, it is difficult to incorporate logic within the flip-flop to reduce its latching overhead [22].

Figure 14: 21264 Latch with keepers

# Cache Design

A large portion of the silicon area of the microprocessor is occupied by regular memory arrays. More than half of the transistors in today's high-performance microprocessors are devoted to cache memories, and this ratio is expected to increase in the future [23]. Therefore, the SER sensitivity of the cache directly impacts the overall chip-level SER.

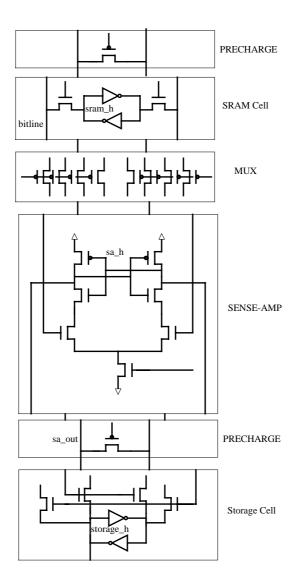

Figure 15: Circuit schematic of the SRAM sensing data-path

The Alpha 21164 includes an 8-kB instruction cache and an 8-kB data cache. A second-level 96-kB cache was present to reduce the overhead of accessing the memory. In the next generation, the Alpha 21264, the size of the instruction and data caches was increased from 8 to 64 kB, thus eliminating the need for the second level cache [14].

Figure 15 illustrates the cache read path extracted from the real design. It includes all the key components in the cache design, SRAM cell, pre-charge and charge balance circuitry, sense amplifier and storage cell. The function and operation of these components will be discussed briefly.

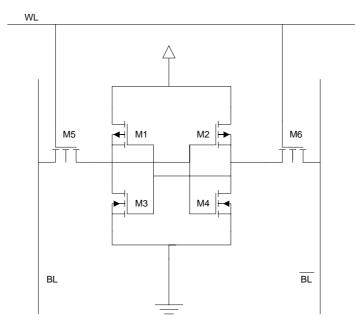

The cache memory is organized in units of words where each word is 64 bits wide. One word at a time is selected for reading or writing. The SRAM cell in Figure 15 represents a bit of the selected word. The selection is indicated by the assertion of word line signal WL, which turns on the pass transistors M5 and M6, as shown in Figure 16. After M5 and M6 are on, the information stored in the SRAM cell will transfer to two bit lines BL and BL. Since the bit lines are shared by many cells in one column, they are pre-charged before the assertion of the word line signal. The voltage swing on the bit lines is substantially lower than the supply voltage; therefore, the function of the sense amplifier is to restore the full rail-to-rail amplitude. After amplification, the information goes to a storage cell for further use. The control signals on this cache read path, such as enabling the word line and the sense amplifier, are generated internally by the peripheral self-timing control circuitry. Therefore, no external timing signals are needed.

Figure 16: The circuit schematic of an SRAM cell

## **CHAPTER IV**

#### **METHODOLOGY**

# Computational Method

The goal of the computational modeling is to predict the soft error rates accurately at the chip level by simulating the interaction of a radiation environment with the microelectronic integrated circuits. Since single events are random phenomena, there is a certain probability  $prob(Q_I)$  associated with the collection of the charge  $Q_I$  by the circuit node per single particle hit. For memory cells under static SEU testing, the cell component of the soft error rate is given by [24][25]

$$SER_{SRAM} = \Phi_{\alpha} A_{SRAM} \int_{Ocrit}^{\infty} prob(Q_I) dQ_I$$

(4-1)

where  $\Phi_{\alpha}$  is the particle flux,  $A_{SRAM}$  is the sensitive area of the SRAM cell, and  $Q_{crit}$  is the critical charge of the SRAM cell. The lower boundary for the integration is  $Q_{crit}$  since errors can only be observed when  $Q_{I}$  is larger than  $Q_{crit}$ .

The critical charge  $Q_{crit}$  of an SRAM cell is related to the supply voltage  $V_{DD}$ , and the following relationship has been proposed by one group [26]

$$Q_{crit} = C_{node}V_{DD} + I_{DP}T_F \tag{4-2}$$

where  $C_{node}$  is the total capacitance of the node,  $I_{DP}$  is the maximum drain conduction current of the PMOS transistor,  $T_F$  is the flipping time and defines the irreversibility point after which the feedback mechanism of the SRAM will take over to continue the cell flipping process.

The SER of a SRAM cell can be obtained as a function of the critical charge by measuring the SER at various supply voltages. In an alpha-particle environment, the SER of SRAM cells is found empirically to be exponentially dependent on the supply voltage [18][27]. In fact, the second term  $I_{DP}T_F$  in Equation (4-2) is found to be negligible, and the critical charge is, in fact, linearly proportional to the supply voltage [26]. Therefore, we have

$$SER_{SRAM}(Q_{crit}) = Be^{-CQ_{crit}}$$

(4-3)

where B and C are deduced from fitting to experimental SER vs. V<sub>DD</sub> data.

Equating the right side of Equations (4-1) and (4-3) and carrying out the derivative on both sides, we have

$$BCe^{-CQ_{crit}} = \Phi_{\alpha} A_{SRAM} \operatorname{prob}(Q_{crit})$$

(4-4)

Rearranging the terms, we obtain

$$prob(Q_{crit}) = \frac{BCe^{-CQ_{crit}}}{\Phi_{\alpha}A_{SRAM}}$$

(4-5)

At the SRAM cell circuit node the probability to collect charge  $Q_{coll}$  per alpha particle, therefore, can be expressed as

$$prob(Q_{coll}) = \frac{BCe^{-CQ_{coll}}}{\Phi_{\alpha}A_{SRAM}}$$

(4-6)

The probability of collecting a certain amount of charge is an exponential function of the collected charge. Therefore, the chance to collect a smaller amount of charge is much larger. In Ref. [27][28] it is shown that this exponential relation will no longer hold at very low  $Q_{crit}/V_{DD}$  values. Instead, the SER saturates in this range. One possible explanation is as follows. Illustrated in Figure 17, the probability density function of the collected charge of 5 MeV alpha particles peaks at 6 fC [28]. The SER as a function of  $Q_{crit}$  is proportional to the integral of this probability density function, i.e., the cumulative density function. The values of collected charge with the highest probability due to low energy alpha particles are rather low compared to the  $Q_{crit}$  of the circuits studied in this work. Therefore, no deviation from the exponential dependence was observed down to the smallest  $V_{DD}$  values investigated in our study. The saturation effect observed in Ref. [27] [28] occurs when  $Q_{crit}$  of the circuit is less than the  $Q_{peak}$  indicated in Figure 17. Further, the exponential dependence of the SER as a function of supply voltage is an empirical observation and only valid for alpha particles; it is not true in the case of neutrons. Because of the higher charge deposition rates associated with high-energy neutron events, the neutron induced SER is less voltage dependent [28].

Since the charge collection process is fairly independent of the cell type, the charge collection probability function derived from 6T SRAM SER data should be applicable to all other cells/data-paths for a given process [18]. It has to be noted that the charge collection varies slightly with the geometrical shape of the collection area [24]. The 6T SRAM cell is found to have the highest soft error susceptibility among all storage cells on the chip; therefore, by using the charge collection probability density function derived from experimental data of 6T SRAM and applying it to all circuit nodes on the same chip, one overestimates the charge collection probability for those circuit nodes other than those in the 6T SRAM cells.

Figure 17: Probability density function and cumulative density function of collected charge for 5 MeV alpha particles[28]

Defining the observed SER as the average over all upsets for all collected charges  $Q_i$ , at all injection times  $t_{inj}$ , and for all nodes n, the SER of any circuit can be expressed as

$$SER = \phi_{\alpha} \sum_{n}^{nodes} A_{n} \sum_{i}^{Q} \sum_{j=t_{inj}}^{T_{cycle}} upset_{n,i,j} prob(n, Q_{i}, t_{inj})$$

$$(4-7)$$

where  $\phi_{\alpha}$  denotes the  $\alpha$ -particle flux,  $A_n$  the node area,  $T_{cycle}$  the cycle time,  $prob(n,Q_i,t_{inj})$  the probability that charge  $Q_i$  is collected when the single hit occurs at node n at the time  $t_{inj}$  per alpha particle, and  $upset_{n,i,j}$  equals 1 if and only if the circuit is upset by a SE hit at node n with collected charge  $Q_i$  at time  $t_{inj}$  [29].

Since the node at which the single hit occurs, when the single hit occurs, and the amount of charge collected by this single hit are independent of each other, the probability is the product of these three terms

$$prob(n, Q_i, t_{ini}) = prob(n)prob(Q_i)prob(t_{ini})$$

$$(4-8)$$

It is assumed the alpha particle flux is uniformly distributed in space and time, therefore,

$$prob(n) = \frac{A_n}{A_{total}} \tag{4-9}$$

$$prob(t_{inj}) = \frac{1}{T_{cycle}} \Delta t \tag{4-10}$$

The error rate is then given by

$$SER = \Phi_{\alpha} \sum_{n}^{nodes} A_{n} \left[ \sum_{i}^{Q} prob(Q_{i,n}) \left( \sum_{j=t_{i,i}}^{T_{cycle}} \frac{1}{T_{cycle}} upset_{n,i,j} \Delta t \right) \Delta Q \right]$$

$$(4-11)$$

Defining

$$\Delta \tau_{n,i} = \sum_{j=t_{inj}}^{T_{cycle}} upset_{j,i,n} \Delta t$$

(4-12)

Equation (4-11) becomes

$$SER = \frac{\Phi_{\alpha}}{T_{cycle}} \sum_{n}^{nodes} A_{n} \sum_{i}^{Q} \Delta \tau_{n,i} \ prob(Q_{i,n}) \Delta Q \tag{4-15}$$

where  $\Delta \tau$  equals the so-called "window of vulnerability" (WOV) [12] [29]. It denotes the time during which a circuit is sensitive to SEU.

The overall chip-level soft error rate for a microprocessor is the sum of the contribution from the cache and the core logic, and can be vastly simplified and expressed as

$$SER_{chip} = \delta^{cache} SER_{cache} + \delta^{core} SER_{core}$$

(4-16)

where  $\delta^{cache}$  and  $\delta^{core}$  are the derating factors of the cache and core contributions. When the cache is protected, either by hardware means such as shielding from the alpha particle source, or through software means, for example, by activating the ECC protection, the derating factor  $\delta^{cache}$  becomes zero. Therefore, the SER measured under this condition is purely the contribution from the core logic. The chip-level SER depends on the program that is run on the microprocessor. The derating factors denote the fraction of soft errors that will actually be noticed by the system. When a test pattern/real program is run, the instruction cache and data cache are partially filled with instruction and data, respectively. The upsets occur in the unused portion of the cache will not be observed, so  $\delta^{cache}$  is not one in the case when the cache is not protected. As for the core logic, if an upset of a logic state in the floating point unit occurs, it might not lead to a noticeable error when the application compares two integer numbers at the time of the upset. Even if the upset occurs at circuit nodes that are being used by the program, the erroneous information may still be blocked by the succeeding logic during the following clock cycle [30]. The derating factors depend on the architecture of the chip as well as on the

application, and can be determined from VHDL-level simulations, as done in [30]. However, in this work the derating factor of the core logic is assumed to be one for simplicity. Therefore, the SER computed in this work accounts for errors that might be undetected by the user, thus is overestimated.

### Simulation Setup

The interaction of the single particles with the IC can be modeled at many levels. In this work, the random bombardment of the circuit by an alpha particle is modeled as a transient current pulse at the circuit level. Plotted in Figure 18, in all spice-level simulations particle strikes were modeled with a double exponential, time-dependent transient current waveform to account for funneling and diffusion charge collection. It can be expressed as [10]

$$I(t) = I_0 (1 - e^{-\frac{t}{t_{rise}}}); (t < t_{peak})$$

$$I(t) = I_0 (1 - e^{-\frac{t_{peak}}{t_{rise}}}) e^{-\frac{t - t_{peak}}{t_{fall}}}; (t > t_{peak})$$

where  $t_{rise}$  is the rise time of the pulse, which is on the order of tens of ps,  $t_{fall}$  is the fall time, and is on the order of a few hundreds ps;  $t_{peak}$  is the time when the current pulse reach its peak value  $I_0$ . These parameters are illustrated in Figure 18.

Figure 18: SE transient current temporal profile for circuit-level simulations

The total deposited charge at the circuit node by this current pulse is

$$Q_{I} = I_{0}[t_{peak} + t_{fall} - t_{rise} - (t_{fall} - t_{rise})e^{-\frac{t_{peak}}{t_{rise}}}]$$

(4-18)

Typical parameters are a rise time on the order of several ps and a fall time on the order of tens to hundreds of ps [10].  $t_{rise}$  and  $t_{fall}$  used in the simulations are process dependent parameters and are obtained from foundry data. Since these are Compaq/Digital proprietary information, the actual number is not given here [31]. In both technologies studied in this work  $t_{fall}$  is much larger than  $t_{rise}$ , therefore, the charge delivered by the current pulse  $Q_I$  can be approximated by  $I_0 \times t_{fall}$ .

DEC SPICE, the Compaq proprietary circuit simulator, was used for all simulations. The model equations and parameters were developed and calibrated to the experiments at Compaq/Digital for the corresponding Digital processes (CMOS6 and/or CMOS728). Since these models are Compaq/Digital proprietary information, they are not discussed in this dissertation.

Due to its large size, evaluating the SER vulnerability of each circuit node in the cache memory using SPICE simulation is not feasible. However, because of the regularity of the cache memory, modeling of SER contributed from the cache can be simplified. The read path illustrated in Figure 15 is used to study the SE sensitivity of the cache memory. Since it includes all the key components in the cache design, the relative SE vulnerability and its frequency dependence can be derived from the simulation study. In contrast, modeling of the core logic part of the microprocessor is not an easy task due to the wide circuit varieties. The first step is to identify the most sensitive circuit type; it is also important have a count of the number of this type of circuit present in the chip in order to have an estimate of the SER of the core logic. This is done by using the simple data path shown in Figure 7 to find the most sensitive circuit elements in the core logic part of the microprocessor. To represent the worst case scenario, the inverter chain in Figure 7 consists of inverters with minimum device size. For each generation of the Alpha microprocessor design, there is a standard latch library from which variation of the latches and several sizes of the same latch design are available at the designers' choice. The latch in Figure 7 was replaced by the latch shown in Figure 12, Figure 13 and Figure 14 to represent the 21164 and the 21264 Alpha microprocessor core logic circuitry, respectively. All latches from the standard library are evaluated for their SE vulnerability.

The reason that the inverter with minimum device size represents the most sensitive combinational circuit element lies in equation (4-15). There are three important factors that determine the contribution of a certain circuit node to the SER. The first one is the diffusion area of

the node. The second one is the window of vulnerability, which depends on the circuit configuration. Since we assume a uniform distribution of the alpha flux in both space and time, the SER contribution is linearly dependent on the diffusion area and the window of vulnerability associated with the node. The third and dominant factor is the critical charge, because the probability of the collected charge depends exponentially on the amount of the collected charge in the case of alpha particle hits. To first order, the critical charge is linearly proportional to the node capacitance. The node capacitance is the sum of gate capacitance (of other inputs connected to this node), diffusion capacitance (of the drain regions connected to this node) and routing capacitance (of connections between this node and other inputs) [32]. Not only is the fan-out capacitance equal to one gate capacitance of the minimum inverter, but the routing capacitance is also reduced to the minimum.

Figure 19: Simulation setup of evaluating the SE vulnerability of the circuit in SPICE

Following the computational method described above, the simulations are set up to calculate the soft error rates according to the equation (4-13). The simulation of a single event hit at the circuit level using SPICE is illustrated in Figure 19. For each data-path, the SE susceptibility of each circuit node is evaluated. As a benchmark, the clock signal controlling the data-path is divided into 1000 intervals. For simulations at low frequencies, a finer temporal mesh is used. The transient SE current pulse is inserted at each interval, and the error is detected at the storage element at the end of the data-path. The critical charge of the node at each time interval is found

iteratively by changing the charge  $Q_i$  contained in the transient SE current pulse. The flow chart of the simulation method to find the critical charge is illustrated in Figure 20.

Figure 20: Flow chart of the simulation method to find the critical charge

# **Experimental Details**

Alpha particles emitted from the trace radioactive material used for device fabrication has been a primary terrestrial radiation source and received a lot of attention over the years. Americium 241 is a preferred alpha particle source to simulate alpha emission from lead-based

solder compounds, because the alpha particles emission from Americium has an energy range similar to those alphas resulting from the decay of Uranium and Thorium, the two major radioactive contamination elements in the device material. Another reason to use accelerate alpha particle testing to assess the SER susceptibility of the microprocessor is availability of the alpha particle source at the lab [33]. Therefore, Americium 241 foils were used for the experimental study of this work. Please note that all the results presented in this work are under the alpha particle environment.

Americium 241 decays to Np 237 via a 5 MeV alpha particle with a half-life of 433 years [34]. The range of the 5 MeV alpha particle is about 5 cm in air [35]. The material holding the Americium absorbs some of the energy from decays occurring deeper within the material so there is a large spread of energies and ranges of the alpha particles that reached the chip. The dimension of the foil is 1.25 inch by 1.25 inch, the same size as the lid of the chip. Therefore, during the test the lid of a wire-bonded Alpha microprocessor is replaced with a radioactive Am 241 foil.

The alpha-particle induced failure rates were measured using a Schlumberger ITS9000 tester, which is a system for testing high performance microprocessors and high-end logic devices. The expected outputs (vectors) are stored in the memory of the computer that controls the testing. Therefore, a mismatch of the logic value on the output pins of the chip can be readily detected while the program is run on the chip. The background rate was determined for all products when the  $\alpha$ -particle source was removed and was in all cases zero. In order to address experimentally the relative susceptibilities of the cache and core logic circuits to SEU, the die were covered partially with either epoxy or paper to block alpha particles from reaching the covered part (see Figure 21). The difference in SER with and without epoxy is a measure of the susceptibility of those areas to  $\alpha$ -particle induced failures.

The SER measurement acceleration can be obtained using an Alpha particle source of high flux since SER is linearly proportional to the particle flux. However, in this work the acceleration factor provided by the Am 241 foil was not sufficient to study the core logic SER with a cost-efficient use of the tester. Further SER test acceleration was achieved by reducing the supply voltage during the SER measurement. However, reducing the supply voltage is equivalent to reducing the critical charge of the chip; therefore, the acceleration factor is exponentially dependent on the  $V_{\rm DD}$  reduction since in the  $V_{\rm DD}$  range in the work, the SER increases

exponentially with decreasing  $V_{DD}$ . For both generations, a low-frequency (20MHz)  $V_{DD}$  scan was first performed. However, reducing  $V_{DD}$  also limits the maximum operational frequency of the microprocessor. Therefore, a tradeoff between the  $V_{DD}$  and operating frequency range has to be made. The supply voltage during the frequency scan measurement is 1.5 V for the 21164 Alpha microprocessor, and 1.1 V for the 21264 Alpha microprocessor. The SER at the nominal operating supply voltage can be back calculated, as will be shown in the result section.

Figure 21: 21164 Alpha microprocessor with several memory arrays covered with epoxy (six gray rectangles in the middle of the chip) to mask the alpha particle