# Single-Event Upset Technology Scaling Trends of Unhardened and Hardened Flip-Flops in Bulk CMOS

By

Nelson J. Gaspard III

### Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

## DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

May, 2017

Nashville, Tennessee

# Approved:

Bharat L. Bhuva Ph.D.

W. Timothy Holman Ph.D.

Lloyd W. Massengill Ph.D.

T. Daniel Loveless Ph.D.

Robert A. Reed Ph.D.

Shi-Jie Wen Ph.D.

#### ACKNOWLEDGEMENTS

First, I would like to acknowledge my advisor Bharat Bhuva for guiding me through this endeavor, keeping my morale up during the tough times, trusting in my skills to, and giving me a great opportunity by allowing me to do this work. Also, I thank Tim Holman, Lloyd Massengill, Daniel Loveless, Robert A. Reed, and Shi-Jie Wen for the invaluable technical advice, understanding, and support. Without funding from DTRA, NRO, TSMC, and Cisco, this project would not have been able to continue and grow to size it is now. Jeff Kauppila, Andrew Sternberg, and Tim Haeffner have provided technical support that made this work possible. Lastly, all of the faculty and staff have been very instrumental in my growth during graduate school.

The next people I would like to thank are students who I met at Vanderbilt University. Mike King, Pierre Malliard, Nadia Rezzak, Nick Atkinson, Geoff Bennett, Daniel Limbrick, Srikanth Jagannathan, Jon Ahlbin, Nick Hooten, Paula Chen, Charlie Arutt, Issak Samsel, Jeff Mahharey, Rachel Quinn, Thiago Assis, Nihaar Mahatme, and Stephanie Weeden-Wright, I am happy to had the opportunity to collaborate with you and share my time outside of the office with you.

Finally, I would like to thank my family for all of their support and understanding throughout this process. Their love and encouragement has been vital to keeping motivated in throughout my graduate school career.

# TABLE OF CONTENTS

|                                                                           | Page    |

|---------------------------------------------------------------------------|---------|

| ACKNOWLEDGEMENTS                                                          | ii      |

| LIST OF FIGURES                                                           | v       |

| LIST OF TABLES                                                            | ix      |

| CHAPTER                                                                   |         |

| I. INTRODUCTION                                                           | 1       |

| Overview                                                                  | 1       |

| Background                                                                |         |

| Single-Event Transients                                                   |         |

| Single-Event Upsets in SRAMs                                              |         |

| Flip-Flop SEU                                                             |         |

| Space and Terrestrial Environments                                        |         |

| Dissertation Overview                                                     |         |

| Dissertation Overview                                                     |         |

| II. MOSFET SIMULATION MODELS                                              | 26      |

| Overview                                                                  | 26      |

| 3D TCAD MOSFET models                                                     | 26      |

|                                                                           |         |

| III. COMPARISON OF NORMAL INCIDENCE HEAVY-ION DFF and                     | HARD-FF |

| SEU CROSS SECTIONS AND MECHANISMS                                         | 32      |

|                                                                           |         |

| Overview                                                                  | 32      |

| DFF and Hard-FF TCAD Simulation Setup                                     | 32      |

| Transistor Drive Current                                                  |         |

| Well Doping Concentration                                                 |         |

| Well Depth                                                                |         |

| Well Width                                                                |         |

| Transistor Spacing from N-well/P-well Boundary                            |         |

| Well Contact Spacing                                                      |         |

| Normal Incidence Heavy-Ion Experimental Results of Flip-Flops in 40-nm, 2 |         |

| 20-nm                                                                     |         |

| Summary of DFF Heavy-Ion Experiments vs. Simulations                      |         |

| Simulation of Hard-FF Normal Incidence Heavy-Ion SEU Cross Sections       |         |

| Traditional Hard-FF Normal Incidence Heavy-Ion SEU Cross Sections         |         |

| Comparison of Normal Incidence Heavy-Ion DFF and Traditional Hard-FF F    |         |

| Summary                                                                   |         |

| IV. COMPARISON OF ANGLED INCIDENCE HEAVY-ION DFF AND HAP |      |

|----------------------------------------------------------|------|

| SEU CROSS SECTIONS                                       | 48   |

| Overview                                                 | 48   |

| Angled DFF Heavy Ion Experimental Results                |      |

| Angled Hard-FF Heavy Ion Experimental Results            |      |

| Comparison of DFF and Hard-FF Angled SEU Cross Sections  |      |

| Summary                                                  |      |

| V. NEUTRON AND HIGH ENERGY PROTON DFF and HARD-FF C      | ROSS |

| SECTIONS                                                 |      |

| Overmiery                                                | 50   |

| OverviewBackground                                       |      |

| Experimental Setup                                       |      |

| Hardened Flip-Flop and SRAM MCU Experimental Data        |      |

| Conclusion                                               |      |

| Conclusion                                               | 33   |

| VI. DISCUSSION                                           | 60   |

| VII. FUTURE WORK                                         | 68   |

| VIII. SUMMARY                                            | 69   |

| APPENDIX                                                 | 70   |

| REFERENCES                                               | 72   |

# LIST OF FIGURES

| Figure Page                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Schematic of a simple latch.                                                                                                                                                                                                                    |

| 2. Schematic of a DICE latch, a type of redundant storage node latch                                                                                                                                                                               |

| 3. Inverter SE cross section vs. the ratio of SET pulse width to measurement latch circuit delay for an ion with LET of 60 MeV-cm <sup>2</sup> /mg at three technology nodes from [10] 4                                                           |

| 4. Illustration of charge sharing among pFETs in an inverter chain from [18]                                                                                                                                                                       |

| 5. SET cross section vs. pulse width for inverter strings with and without guard bands in 130-nm bulk CMOS. The inverter strings without guards have a higher probability to share charge and reduce SET pulse widths from [18]                    |

| 6. Illustration of inverter chain targets implemented in 90-nm bulk CMOS from [18] a) shows the inverter chains where the sensitive inverters are not surround by transistors. b) shows the inverter chains that are surrounded by dummy inverters |

| 7. Illustration of parasitic bipolar of a pFET and resistances that affect bipolar activation from [20]                                                                                                                                            |

| 8. SRAM $Q_{crit}$ vs. technology feature size from [25]. $Q_{pu} + Q_{pd}$ is the critical charge produced by the transistor drive currents and make up a significant portion of the total $Q_{crit}$ .                                           |

| 9. Normalized SER for SRAM cells vs. technology feature size for various works from [2]                                                                                                                                                            |

| 10. Flip-flop neutron (n-SER) and alpha (a-SER) for three technology nodes from [2] 11                                                                                                                                                             |

| 11. Calculated SER values vs. technology node compiled in [2]                                                                                                                                                                                      |

| 12. 90-nm heavy-ion SE cross section vs. LET from [5]                                                                                                                                                                                              |

| 13. Example of charge sharing upsetting a latch. Charge collected at the pFET and nFET can cause a SEU.                                                                                                                                            |

| 14. Example of charge sharing preventing an upset in a simple latch                                                                                                                                                                                |

| 15. DICE schematic introduced by Calin et al. [4]                                                                                                                                                                                                  |

| 16. Schematic of a DICE latch (a) and Quatro latch (b) from [51]                                                                                                                                                                                   |

| 17. Heavy-ion cross section vs. LET at normal incidence for DFF, DICE, and Quatro in a 40-nm bulk process from [8]                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18. Schematic of the SEUT latch from [53]                                                                                                                                                                                                                                                                                                                                                                                                                |

| 19. Neutron experimental results in 90-nm bulk for DFF (L1) and SEUT with different threshold voltage implants (L2-4) from [53]                                                                                                                                                                                                                                                                                                                          |

| 20. Schematic of SEILA latch after [54]                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21. Schematic of the BISER design from [52]                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22. Schematic of the BCDMR design from [54]                                                                                                                                                                                                                                                                                                                                                                                                              |

| 23. LEAP principle for an inverter with transistor alignment. (a) Reduced charge collection when a particle hits both NMOS and PMOS drain nodes of an inverter simultaneously. (b) Transistor alignment to reduce charge collection in the horizontal direction [57]                                                                                                                                                                                     |

| 24. Integral energy loss spectrum at geosynchronous orbit from [62]                                                                                                                                                                                                                                                                                                                                                                                      |

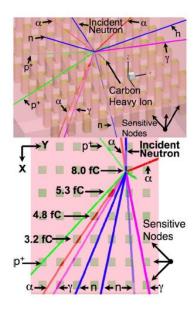

| 25. MRED generated nuclear event. The shaded volumes represent the sensitive nodes of the memory device. The incident neutron enters and induces a nuclear event. The shower of secondary products includes alpha particles, protons, neutrons, gamma rays, and a carbon heavy ion $(n + Si \rightarrow C + 3n + 2p + 3\alpha)$ . In the top-down view on bottom, the generated charges for sensitive nodes with more than 1 fC are labeled from [67] 23 |

| 26. Relative frequency of secondaries produced from neutron-silicon collisions versus energy at sea level in New York City from [68]                                                                                                                                                                                                                                                                                                                     |

| 27. Density of electron-hole pairs generated in silicon [68]                                                                                                                                                                                                                                                                                                                                                                                             |

| 28. Neutron secondary particle distances in Si vs. energy [68]                                                                                                                                                                                                                                                                                                                                                                                           |

| 29. Current versus voltage sweeps for a nFET with L=80nm and W=280nm                                                                                                                                                                                                                                                                                                                                                                                     |

| 30. nFET 3D TCAD structure. A) overhead view of nFET and wells. B) Side view of nFET showing the P-well, P+ buried layer, and P-substrate. C) Close-up view of nFET.                                                                                                                                                                                                                                                                                     |

| 31. 1D cut-line showing the doping concentration versus depths at various locations of the nFET structure                                                                                                                                                                                                                                                                                                                                                |

| 32. Current versus voltage sweeps for a pFET with L=80nm and W=280nm                                                                                                                                                                                                                                                                                                                                                                                     |

| pFET showing the N-well, P+ buried layer, and P-substrate. C) Close-up view of pFET.                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34. 1D cut-line showing the doping concentration versus depths at various locations of the pFET structure                                                                    |

| 35. Illustration of the 3D TCAD simulation setup to strike a single nFET in a latch 33                                                                                       |

| 36. Illustration of a nFET being simulated in the physical portion of the simulation and the pFET widths are varied to emulate decreasing FET drive currents with scaling 34 |

| 37. 3D TCAD simulations results showing the greatest extent from the drain an ion strike with a LET of 58 MeV-cm2/mg will cause an SEU in the latch vs. transistor width 35  |

| 38. Greatest extent that can cause an SEU in a latch vs. well doping                                                                                                         |

| 39. Greatest extent that can cause an SEU in a latch vs. well depth                                                                                                          |

| 40. Greatest extent that can cause an SEU in a latch vs. well width                                                                                                          |

| 41. Greatest extent that can cause an SEU in a latch vs. spacing to n-well/p-well boundary                                                                                   |

| 42. Greatest extent that can cause an SEU in a latch vs. spacing between contacts                                                                                            |

| 43. Schematic of the latch used to create the master/slave flip-flop on the three test chips.                                                                                |

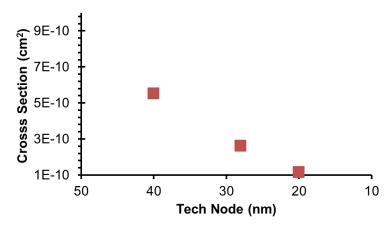

| 44. Alpha SEU cross section per FF vs. technology feature size for a DFF                                                                                                     |

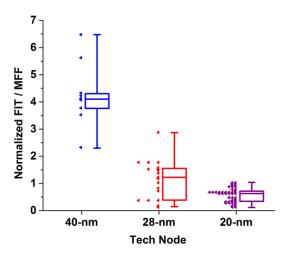

| 45. Normalized Alpha SEU cross sections of various flip-flops across three technologies.                                                                                     |

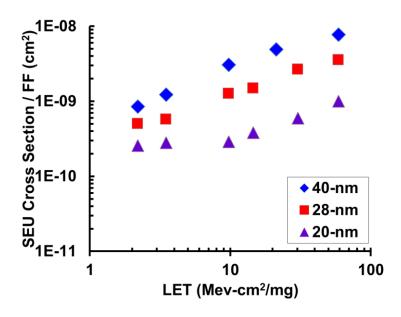

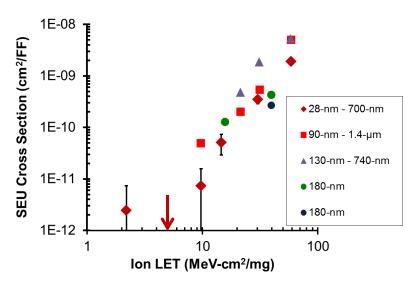

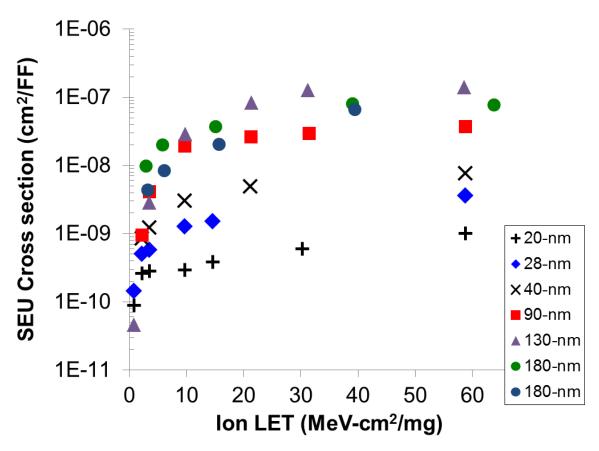

| 46. Heavy-ion SEU cross section vs. LET for the DFF                                                                                                                          |

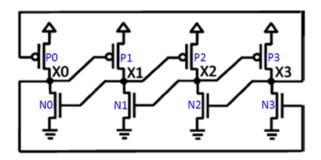

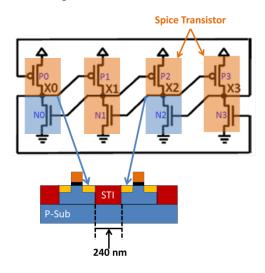

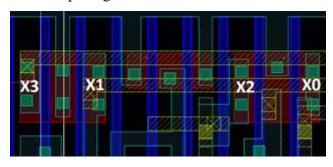

| 47. Illustration of 2D TCAD setup for a hard-FF. The X0 and X2 nFETs and implemented in the 2D model and the other transistors are implemented in spice 45                   |

| 48. SEU Cross section vs. LET for hard-FF designs. The technology feature size is given on the left in the legend and the node spacing is given on the right                 |

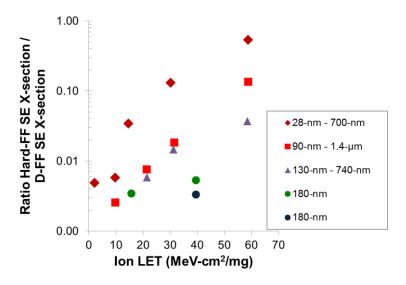

| 49. Ratio of hard-FF SEU cross section to DFF SEU cross section for each technology node vs. LET                                                                             |

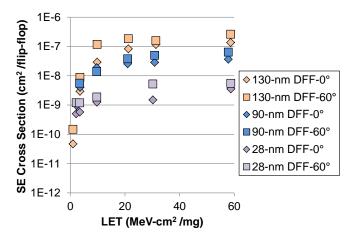

| 50. DFF SE cross section vs. LET for normal incidence and 60°. Error bars for 28-nm results with 95% confidence intervals smaller than symbols                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

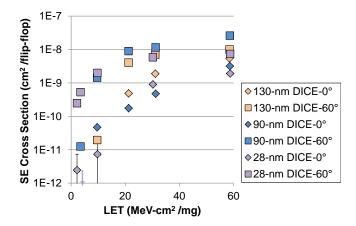

| 51. Hardened flip-flop SE cross section vs. LET for normal incidence and 60°. Error bars for 28-nm results with 95% confidence intervals shown                  |

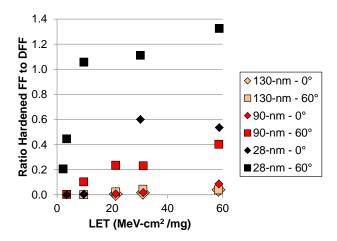

| 52. Ratio of hardened flip-flop (FF) cross section to DFF cross section vs. LET at normal incidence and 60°                                                     |

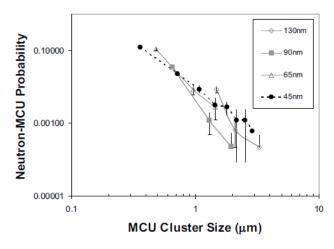

| 53. SRAM neutron MCU probability (ration of MCUs to single-cell upsets) versus cell cluster size along the bit line for various bulk CMOS technology nodes [40] |

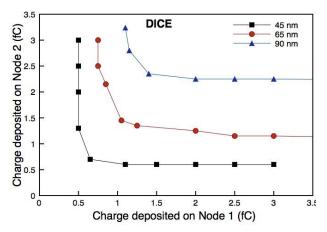

| 54. SMHOO plot showing minimum charge collected at two storage nodes in a DICE flip-flop to cause as upset for various technologies [48]                        |

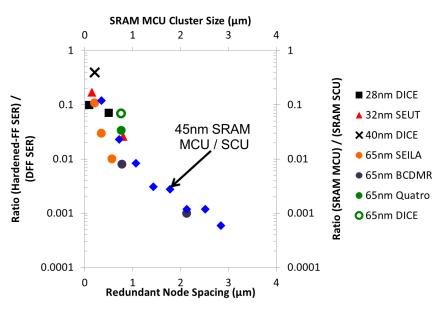

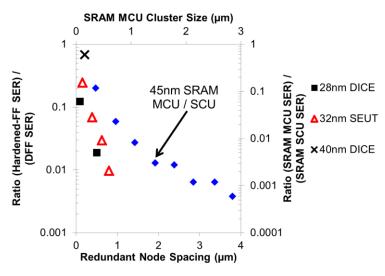

| 55. Ratio of hardened FF neutron SER to DFF SER neutron data from various designs overlaid onto 45-nm SRAM neutron MCU cluster size data                        |

| 56. 28-nm layout of pFETs and corresponding storage nodes. Red is active and vertical dark blue is poly                                                         |

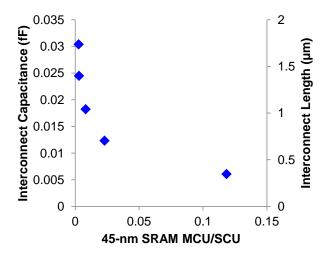

| 57. Interconnect capacitance and interconnect routing length between storage nodes versus 45-nm SRAM MCU/SCU. Interconnect capacitance values [69]              |

| 58. Ratio of hardened FF proton SER to DFF SER overlaid onto 45-nm SRAM neutron MCU data                                                                        |

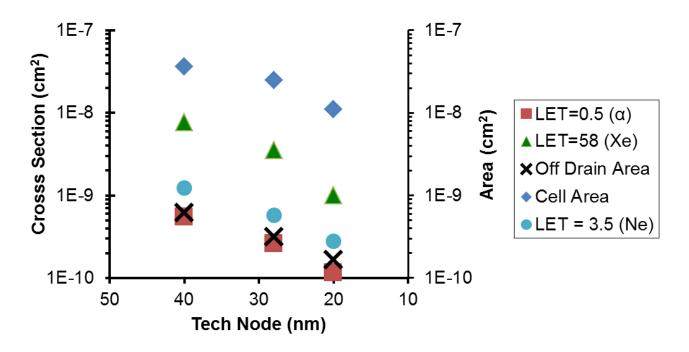

| 59. SEU Cross Section, Drain Area, and Cell Area vs. Technology Node                                                                                            |

| 60. SEU Cross section vs. LET for DFFs from 180-nm to 20-nm                                                                                                     |

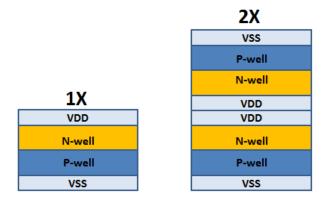

| 61. 1X and 2X height cell illustration                                                                                                                          |

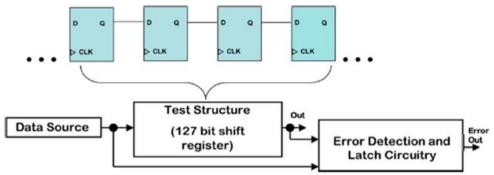

| 62. Illustration of the shift register design used in the test chips [70]                                                                                       |

# LIST OF TABLES

| Table                                                                              | Page |

|------------------------------------------------------------------------------------|------|

| 1. Number of Sensitive Node Pairs in DICE and Quatro from [8]                      | 16   |

| 2. Neutron experiment SER at 65-nm bulk from [50]                                  | 16   |

| 3. Simulations parameters kept constant when changing the transistor width         | 34   |

| 4. Common simulations parameters while peak well doping concentration was changed. | 37   |

| 5. Common simulations parameters while well depth was changed                      | 38   |

| 6. Common simulations parameters while well width was changed                      | 39   |

| 7. Common simulations parameters while n-well/p-well boundary spacing was changed. | 40   |

| 8. Common simulations parameters while spacing between well contacts was changed.  | 41   |

| 9. Ion Species and LET Values TEsted at LBNL                                       | 43   |

| 10. Technology Node Summary of number of flip-flops and die                        | 70   |

#### **CHAPTER I**

### INTRODUCTION

#### **Section 1.1 Overview**

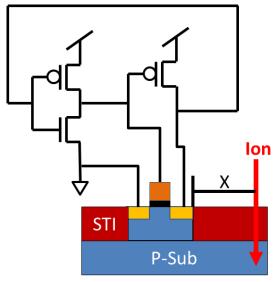

A single event (SE) is caused by an ionizing particle that travels through silicon producing electron-hole pairs in an integrated circuit (IC). If the SE ion strike deposits charge near a transistor, the deposited charge may be collected by drift-diffusion processes, and potentially change the voltage of the circuit node associated with that transistor leading to single-event upsets (SEU) in memory storage elements or single-event transients (SET) in combinational logic that may be latched into memory [1]. For the advanced technologies, all environments, space as well as terrestrial, are vulnerable to single-event effects. Thus, designers must find methods to detect and mitigate these errors to ensure system integrity.

One area of focus for single-event effects (SEE) in ICs is flip-flop SEU error rates. Flip-flops are generally used as temporary data storage between operations in computer processing units (CPU) and in pipeline processor architectures. A SEU in a CPU's flip-flops can affect many operations resulting in errors at the output of the chip. When a semiconductor region in a flip-flop collects charge from a SE strike, an SET is produced in the flip-flop's latch circuit. If the SET is longer than the feedback loop delay of the latch, the data state of the latch is changed, resulting in an upset. The minimum amount of charge that must be collected to result in an SEU is called the critical charge (Q<sub>crit</sub>). Typically, higher flip-flop Q<sub>crit</sub> leads to increased SEU robustness for a design.

A flip-flop's Q<sub>crit</sub> decreases if node capacitance, transistor drive current, or supply voltage decreases [2]. As CMOS technology feature sizes scale to smaller dimensions, transistor drive strength, node capacitance, and supply voltage decrease resulting in lower flip-flop Q<sub>crit</sub>. As technology scaling continues, smaller amounts of charge are needed to cause upsets reducing the SEU robustness of flip-flops compared to older technologies. Such increased vulnerability has lead designers to find ways to either increase Q<sub>crit</sub> through process changes or implement different flip-flop topologies to increase SEU robustness.

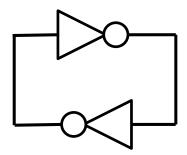

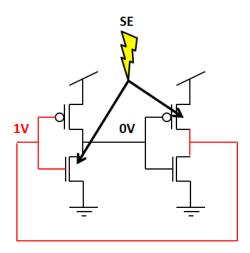

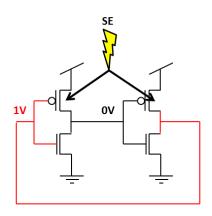

In the search for new SEU tolerant flip-flop topologies, designers harden flipflops either through temporal [3] or storage-node redundancy [4] schemes. Temporal redundancy schemes employ multiple sampling of data at various times which requires multiple clocks and/or resistor-capacitance (RC) delays within the latch. Due to the speed penalties and complex clocking circuitry needed for temporal designs, redundant storagenode designs are favored among designers. For storage-node redundant designs, additional circuit is added to a flip-flop to increase the number of storage nodes. A latch in a flip-flop has only two data storage nodes, as shown in Figure 1, and is susceptible to SEUs even when charge is collected at any one of the circuit nodes. Figure 2 shows a dual interlocked cell (DICE) latch as an example of a redundant storage node latch that implements four storage nodes and will not upset from charge collection on a single node [4]. Of course, redundant storage node designs come at the cost of increased number of transistors, layout area, power, and lower operating speed of the design. As technologies scale, redundant node flip-flops have been shown to become more vulnerable to multiple node charge collection and designers have begun looking for alternatives to improve IC soft error rates (SER) [5]–[9].

Figure 1. Schematic of a simple latch.

The goal of this work is to use experimental and simulation results for older technologies from literature and compare them to data from 40-nm and 20-nm technology nodes to establish SE trends in flip-flop designs. This work begins with a literary survey of various SE phenomena that cause flip-flop SEUs in hardened and unhardened designs. Then, background is given for different types of sources for SEEs and their relationship to SEUs in hardened and unhardened flip-flops. The remaining sections are divided between unhardened and hardened flip-flop sections to examine the trends separately.

Figure 2. Schematic of a DICE latch, a type of redundant storage node latch

Technology computer aided design (TCAD) simulations are used to examine various effects that can change the SEU cross section of a latch in a D flip-flop (DFF) with respect to various parameters that change as technology features sizes decrease. Experimental results for DFF designs show that the experimental SEU cross section decreases with technology scaling across the LET spectrum, which indicates that effects that will decrease a DFFs SEU cross section will dominate over the other effects that would cause the cross section to increase.

Hardened redundant storage node design experimental results show that the SEU cross section remains similar as technologies scale. TCAD simulations show that a combination of factors related to well potential modulation (WPM) activating the parasitic bipolar structure of pFETs is the dominating factor in determining the over SEU cross section.

### **Section 1.2 Background**

## Section 1.2.A. Single-Event Transients

When an ionizing particle deposits charge near an off transistor, a portion of the deposited charge may be collected by the transistor's source and drain junctions. If enough charge is collected to overcome the charge stored at the associated circuit node capacitance and the restoring current of the complementary transistors connected to the off-state transistor, the node voltage will be temporarily changed resulting in a single-event transient (SET). With sufficient amounts of collected charge, the SET amplitude can swing from rail-to-rail. The SET pulse width is proportional to the amount of charge collected by the off-state transistor, the circuit node capacitance, and restoring current transistor drive strength [10]–[14].

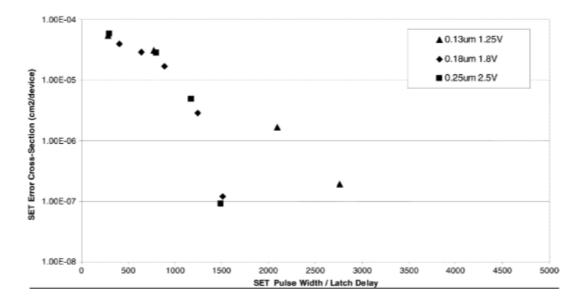

Technology feature size scaling, in part, aims to reduce node capacitance, transistor currents, and supply voltages to reduce power requirements and increase operating speeds. Reducing these three factors increases the likelihood of an ionizing particle to induce a rail-to-rail voltage transient. Benedetto et al., showed experimentally that as technologies scale, SET pulse widths and cross sections will increase with technology scaling and due to decreasing supply voltages in inverter strings [10]. Gadlage et al. showed that pulse broadening caused by long inverter chains and dissimilarities in well contacting in target inverter chains are affecting experimental data potentially skewing measured pulse widths to be longer than originally generated by SEs [15]. After taking into account factors affecting experimental results, SET pulse widths appear to decrease when scaling from 90-nm to 65-nm in bulk CMOS. Thus, there are conflicting results and the other works in this section provide insight as to how this may occur.

Figure 3. Inverter SE cross section vs. the ratio of SET pulse width to measurement latch circuit delay for an ion with LET of 60 MeV-cm<sup>2</sup>/mg at three technology nodes from [10].

As technologies feature sizes decrease, transistor area and pitch decreases leading to higher transistor densities and more circuitry that can be implemented on an IC. This decrease in transistor pitch has greatly increased the probability that a single ionizing particle can deposit charge in the vicinity of multiple transistors and affect multiple

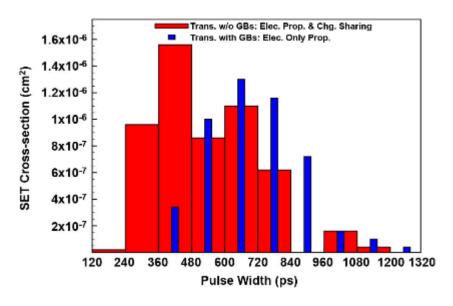

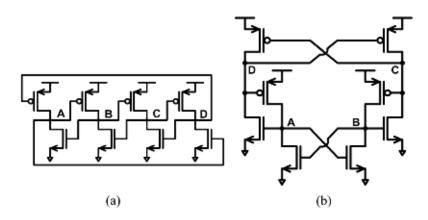

circuit nodes, commonly called charge sharing or multiple node charge collection, illustrated in Figure 4 [16]. Charge sharing has been demonstrated in multiple experiments to reduce SET pulse widths and cross sections in inverter strings [17]–[20]. Ahlbin et al. showed experimentally that when the effects of charge sharing are increased by not implementing guard bands (additional well contacts) in inverter strings, the SET pulse widths decrease compared to inverters with less charge sharing due to additional guard bands at 130-nm technology node, shown in Figure 5 [19]. Another mechanism, called pulse quenching, occurs in inverter strings when multiple logic gates electrically connected collect charge due to a single ion hit. Here the SET generated by the node that initially collects the SE deposited charge produces a SET and the charge collected by other electrically related logic gates in the path of the SET transient reduce the pulse width of the original SET pulse. As the probability of charge sharing, and subsequently pulse quenching, increases with scaling, circuit design methodologies may be developed that reduce overall SET pulse width to improve radiation hardening of flip-flops.

Figure 4. Illustration of charge sharing among pFETs in an inverter chain from [18]

Figure 5. SET cross section vs. pulse width for inverter strings with and without guard bands in 130-nm bulk CMOS. The inverter strings without guards have a higher probability to share charge and reduce SET pulse widths from [18]

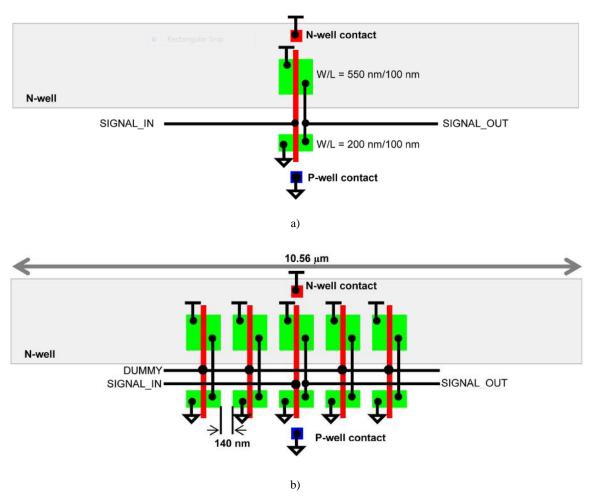

There is another effect that reduces SET cross sections due to increases in charge sharing and increased transistor densities due to scaling. Atkinson et al. showed experimentally that increased transistor densities can reduce SET cross sections of inverter chains [20]. The presence of dummy transistors placed around the inverter chain targets, illustrated in Figure 6, compared to isolated inverters can reduce the SET cross section by up to 70% in a 90-nm bulk CMOS process. The dummy inverters are able to collect charge from SE strikes far from the sensitive inverters and preventing a SET. Even though the presence of other transistors near the sensitive inverters may not reduce the SET pulse widths, increasing the presence of non-sensitive transistors near sensitive transistors can reduce the number of SETs. A higher probability of non-sensitive transistors reducing SET cross sections occurs as transistor densities increase with technology scaling.

It is important to note that SETs can cause SEUs in flip-flops in two ways: by occurring within the latch or propagating from logic circuits and being latched into the flip-flop at a clock edge. This work focuses on SETs that occur within the flip-flop creating an SEU. If the SET is longer than the feedback loop delay of the flip-flop's latch, an SEU will occur. With scaling, SET transients can become longer and have a higher probability of becoming an SEU, but increased probability of SET pulse quenching and

higher density of non-sensitive transistors in a flip-flop's latch may help to reduce the chance of SEUs occurring. In this report we explore how these mechanisms manifest into SEU cross sections as a function of technologies currently in use by the semiconductor industry.

Figure 6. Illustration of inverter chain targets implemented in 90-nm bulk CMOS from [18] a) shows the inverter chains where the sensitive inverters are not surround by transistors. b) shows the inverter chains that are surrounded by dummy inverters.

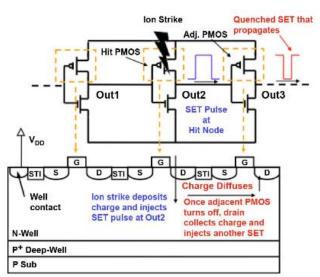

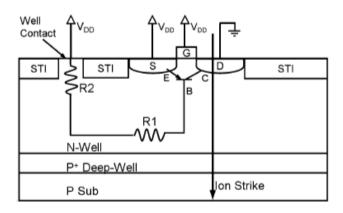

The parasitic bipolar structure of MOSFETs have been shown to turn ON by SET inducing ion strikes as illustrated in Figure 7 [21]–[24]. A SE strike deposits charge that is collected by transistor and well-contacts. As well-contacts collect charge, a potential drop is formed from the strike location to the well-contacts. The longer the charge remains in the well, the longer the well potential is modulated causing the parasitic bipolar to turn ON for a longer time. The parasitic bipolar transistor injects current from the source into the drain increasing SET pulse widths. Ahlbin et al showed

experimentally that SET pulse widths can reach up to 4 ns if well-contacts are spaced 30 µm apart in inverter chains; but if strip contacts are used along the wells, SET pulse widths are limited to a maximum with of 600 ps [23]. Thus, proper well-contacting is important in reducing SET pulse widths.

Figure 7. Illustration of parasitic bipolar of a pFET and resistances that affect bipolar activation from [20]

# Section 1.2.B. Single-Event Upsets in SRAMs

Due to the similarities of some latches used in flip-flop designs and Static Random Access Memory (SRAM) cells, it is important to survey the SEEs and technology scaling effects in SRAMs. Both SRAM cells and latches (unhardened designs) are generally composed of cross coupled pair of logic gates (usually inverters) resulting in only two data storages nodes. If sufficient charge is deposited on one of the two storage nodes, an SET is generated. If the SET pulse width is longer that the feedback loop delay of the design, it will result in an SEU. Typically, the Q<sub>crit</sub> for a latch is 10X to 100X higher than an SRAM cell at a given technology node [2]. The remainder of this section focuses on SEE trends vs. scaling seen in SRAM cells.

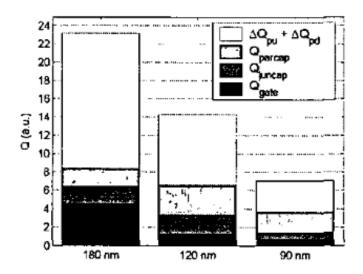

One metric used to judge SRAM sensitivity vs. technology scaling is Q<sub>crit</sub> [2], [25]–[32]. Knowing the critical charge and the sensitive charge collection region of an SRAM cell, designers can estimate the single-event error-rate of a design. Technology scaling has been shown to reduce the Q<sub>crit</sub> of SRAM cells, shown in Figure 8 [2], [31].

Figure 8. SRAM Q<sub>crit</sub> vs. technology feature size from [25]. Q<sub>pu</sub> + Q<sub>pd</sub> is the critical charge produced by the transistor drive currents and make up a significant portion of the total Q<sub>crit</sub>.

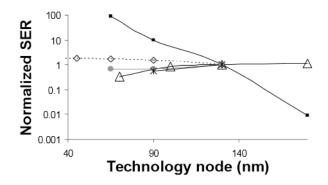

SRAM neutron and alpha SER has been reported to increase or decrease with technology scaling and is mostly dependent on process parameters or circuit design. Seifert et al. showed SRAM neutron and alpha error rates decrease for feature sizes below 180-nm for various processes [2]. Other works show the SRAM alpha SER continues to increase until 65-nm and may continue decrease, but the neutron SER continually decreases below 180-nm [33], [34]. This shows there is some process and/or circuit affects in the technology scaling trends of SRAMs. Seifert et al. predictions shows at some point below 180-nm, the Q<sub>crit</sub> of SRAM cells becomes very small that cells are easily upset and the soft error rate (SER) ultimately becomes a function of the SRAM cell area.

Figure 9. Normalized SER for SRAM cells vs. technology feature size for various works from [2].

Another consequence of smaller transistor areas that come with feature size scaling is the decreased distance between SRAM cells, resulting in an increased probability for charge sharing between multiple SRAM cells and the subsequent increase in multiple cell upsets [2], [25], [28], [35]–[39]. Multiple cell upsets (MCUs) in SRAM arrays can potentially defeat error-correcting code schemes leading to corruption of data. Gasiot et al. showed that SRAM MCUs have been attributed to well-potential modulation (sometimes called well-potential collapse) and is a major contributor to SRAM SER at 65-nm [39]. Seifert et al. has shown that MCUs can span up to 3 µm below 90-nm [40].

A way to study charge sharing effects on SRAM cell upset rates is by characterizing the difference between dual- and triple-well processes. Chatterjee et al. showed experimentally that SRAM implemented in triple-well can have lower SE single cell upsets (SCU) and multiple cell upsets (MCU) at LET values above 24 MeV-cm<sup>2</sup>/mg [37]. For higher LET ion strikes, the amount of deposited charge results in longer perturbation of well-potential, allowing SRAM cells to upset twice (resulting in no upset). Thus, triple-well process enhances the charge sharing in the nFETs preventing SCUs and MCUs in the SRAMs compared to the dual well process at LET values above 25 MeV-cm<sup>2</sup>/mg. For LET value below 24 MeV-cm<sup>2</sup>/mg, the triple-well option perform worse than the dual-well option for both SCU and MCU due to lower probability of

charge sharing preventing upsets. Thus, charge sharing in SRAM cells can be an important mechanism in preventing SEUs at high LET values.

# Section 1.2.C. Flip-flop SEU

There are many different ways to create unhardened flip-flops, but they are similar in that they use a feedback loop similar to an SRAM cell in the master/slave latches. Some flip-flop latches are almost identical to an SRAM cell. Thus, the mechanisms that cause SEUs in SRAM cells are similar for flip-flops. The technology scaling effects on flip-flops SE cross sections and SER have been studied in literature, but not as comprehensively as SRAM cells. This section looks at the literature studies of flip-flops, both unhardened and hardened.

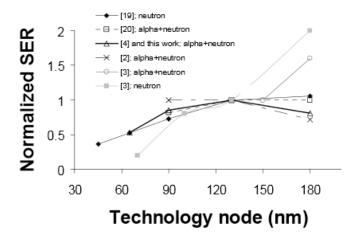

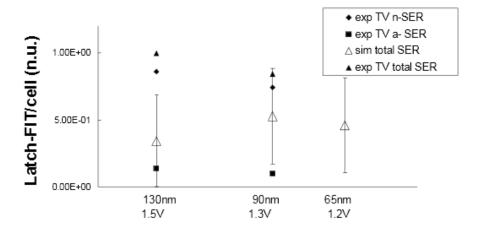

Technology scaling trends have been reported for alpha and neutron experiments in flip-flops [2], [31], [38], [39], [41]–[43]. Seifert et al. showed experimentally that flip-flop alpha and neutron SER decreases for processes below 130-nm, shown in Figure 10 [2]. In the same paper, data compiled from different works is compared for flip-flops across technology nodes, but show some disagreement, shown in Figure 11. These results show that the flip-flop alpha and neutron SER will at best decrease or remain the same as technology scaling progresses.

Figure 10. Flip-flop neutron (n-SER) and alpha (a-SER) for three technology nodes from [2].

Figure 11. Calculated SER values vs. technology node compiled in [2].

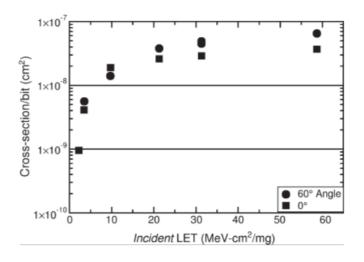

Heavy-ion experiments for unhardened flip-flops have been conducted for various technology nodes, though they have never been directly compared [5], [8], [44]–[47]. In Figure 12, 90-nm bulk heavy-ion results for a range of LET values show the classical flip-flop cross section curve [5]. One thing that is common in all these works is that hardened flip-flop SE cross sections robustness is decreasing compared to unhardened flip-flops.

Figure 12. 90-nm heavy-ion SE cross section vs. LET from [5].

Amusan et al. showed that charge sharing can cause SEUs to occur in hardened flip-flops [5]. Figure 13 shows an example of how charge sharing can cause an upset in a simple latch; if charge is collected at an off pFET and an off nFET in the latch, an upset will occur. The charge required at both the nodes to cause an upset is lower than the

charge required for a single node upset. It has been shown that the amount of charge to upset a flip-flop by charge sharing decreases with technology scaling [48]. Since the probability for charge sharing increases with scaling, the probability of an upset due to charge sharing also increases with technology scaling.

Figure 13. Example of charge sharing upsetting a latch. Charge collected at the pFET and nFET can cause a SEU.

Charge sharing has also been shown to prevent SEUs in unhardened flip-flops [47], [49]. Figure 14 shows an example of how charge sharing between the two pFETs in a latch can prevent an SEU. Kauppila et al. showed that charge sharing can reverse the original upset by collecting charge on the complimentary storage node [49]. Seifert et al. showed that if the distance is reduced between unhardened flip-flop storage nodes, charge sharing has a greater chance to reduce SE cross section of a design [47]. Thus, there are competing mechanisms in unhardened flip-flops that may increase or decrease the flip-flops SE cross section depending on layout and other factors as technology feature sizes become smaller.

Figure 14. Example of charge sharing preventing an upset in a simple latch.

To improve the SE robustness of registers, flip-flop designs with redundant storage nodes, such as DICE, were developed [4]. The schematic for a DICE latch introduced by Calin et al. is shown in Figure 15. The transistors of the DICE latch are connected in such a way that charge collection on a single node will not result in an upset and the flip-flop will recover from all voltage perturbations caused by an incident ion. Amusan et al. have showed that for hardened flip-flops, such as DICE, SE robustness is very sensitive to the spacing between storage nodes of transistors [5], [46], [50]. This is mainly due to the charge sharing between two (or more) storage nodes of DICE-like designs. Charge-sharing renders these flip-flops vulnerable to single events. Because of this vulnerability, designers have looked for other redundant storage node designs to improve the SE reliability of flip-flops in bulk CMOS. These designs include Quatro [51], built-in soft error resilience (BISER) [52], SEU tolerant (SEUT) [53], Bistable Cross-coupled Dual-Modular Redundancy (BCDMR) [54], soft error immune latch (SEILA) [55], [56], and Layout Design through Error-Aware Transistor Positioning (LEAP) DICE [57], [58].

Figure 15. DICE schematic introduced by Calin et al. [4]

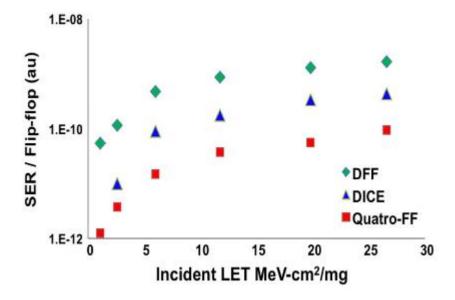

The Quatro latch created by Rennie et al. is similar to DICE, but with a small change in the schematic topology [54]. The Quarto schematic topology has two fewer sensitive node pairs per latch compared to a DICE-like topology [8], [54], shown in TABLE I. The fewer sensitive node pairs of the Quatro latch has been shown to produce a lower SE cross section in heavy-ion experiments in a 40-nm bulk process, shown in Figure 17. For neutron experiments, the Quatro latch performs better than a DICE-like latch as shown in TABLE II. Thus, by altering a DICE-like topology and reducing the number of sensitive node pairs it is possible to reduce the flip-flop cross section.

Figure 16. Schematic of a DICE latch (a) and Quatro latch (b) from [51]

TABLE I. Number of Sensitive Node Pairs in DICE and Quatro from [8]

| Latch  | # of sensitive node pairs for data at nodes A and<br>C = logic 0 and nodes B and D = logic 1 |                                        |           |  |  |

|--------|----------------------------------------------------------------------------------------------|----------------------------------------|-----------|--|--|

|        | NMOS-<br>NMOS                                                                                | PMOS-PMOS                              | NMOS-PMOS |  |  |

| DICE   | 1                                                                                            | 1                                      | 12        |  |  |

| Quatro | 1 (N <sub>B</sub> and N <sub>D</sub> )                                                       | 1 (P <sub>A</sub> and P <sub>C</sub> ) | 10        |  |  |

Figure 17. Heavy-ion cross section vs. LET at normal incidence for DFF, DICE, and Quatro in a 40-nm bulk process from [8]

TABLE II. Neutron experiment SER at 65-nm bulk from [50]

|        | area<br>(um²) | V <sub>DD</sub> (V) | time<br>(hr) | errors | cross-<br>section<br>(10 <sup>-10</sup><br>cm <sup>2</sup> ) | cross-<br>section<br>bound<br>(10 <sup>-10</sup><br>cm <sup>2</sup> ) | SER<br>(FIT/<br>Mbit) | SER<br>bound<br>(FIT/<br>Mbit) |

|--------|---------------|---------------------|--------------|--------|--------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------|--------------------------------|

|        |               | 1.0                 | 2.1          | 2      | 1.27                                                         | 1.91                                                                  | 338.8                 | 508.2                          |

| DFF    | 9.9           | 0.9                 | 5.4          | 7      | 1.74                                                         | 1.99                                                                  | 465.0                 | 531.4                          |

|        |               | 0.8                 | 16.2         | 28     | 2.34                                                         | 2.43                                                                  | 625.1                 | 647.4                          |

|        |               | 1.0                 | 2.1          | 0      | 0.00                                                         | 0.64                                                                  | 0.00                  | 169.4                          |

| Quatro | 11.7          | 0.9                 | 5.4          | 1      | 0.25                                                         | 0.50                                                                  | 66.4                  | 132.9                          |

|        |               | 0.8                 | 16.2         | 0      | 0.00                                                         | 0.08                                                                  | 0.00                  | 22.3                           |

|        |               | 1.0                 | 2.1          | 0      | 0.00                                                         | 0.64                                                                  | 0.00                  | 169.4                          |

| DICE   | 15.0          | 0.9                 | 5.4          | 2      | 0.50                                                         | 0.75                                                                  | 132.9                 | 199.3                          |

|        |               | 0.8                 | 16.2         | 1      | 0.08                                                         | 0.17                                                                  | 22.3                  | 44.7                           |

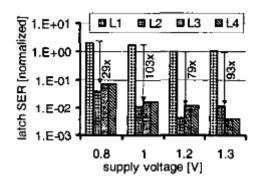

The SEUT design is similar to a DICE design, but uses a different clocking method to write the data to the latch and reduce power consumption, shown in Figure 18

[56]. Neutron experiments show that the SEUT has 30X smaller SER than an unhardened flip-flop, as shown in Figure 19.

Figure 18. Schematic of the SEUT latch from [53]

Figure 19. Neutron experimental results in 90-nm bulk for DFF (L1) and SEUT with different threshold voltage implants (L2-4) from [53]

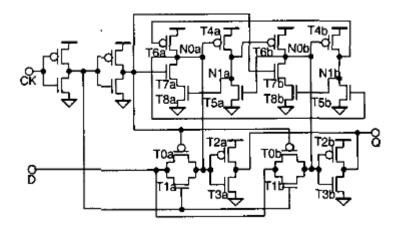

SEILA latch is similar to the DICE design in that it also uses cross coupled multiple storage nodes and does not upset from charge collected on a single node [58], [59]. This method uses a C-element in place of one of the nFET-pFET pairs, shown in Figure 20. The C-element acts as a low pass filter (LPF) helping to block small transients from upsetting the latch, but this is only effective for small amount of charge and the author predicts this will not be useful for the space environment [62]. Neutron experiments show the SEILA latch can obtain ~50X reduction in SER compared to a standard DFF [58].

Figure 20. Schematic of SEILA latch after [54]

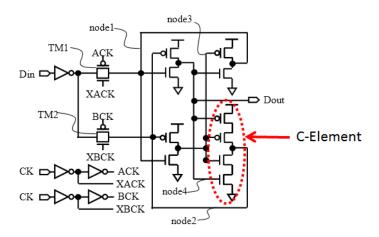

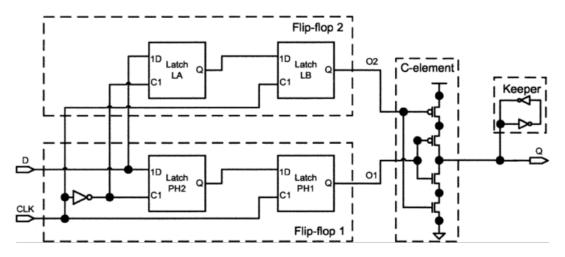

The BISER flip-flop design uses a slightly different approach from DICE by using a form of triple mode redundancy (TMR) to harden the flip-flop [55]. The BISER design uses two parallel flip-flops connected to a C-element, shown in Figure 21. When uncorrupted data is stored in both the two flip-flops, the C-element writes the correct data to the keeper latch. Due to the presence of the C-element, the keeper latch will retain the previously written correct value even if one of the flip-flop values is changed by a single event. If only the keeper latch is stuck by an ion, the data will be overwritten in the keeper latch by the two flip-flops controlling the C-element. If any combination of two of flip-flops or keeper circuit has erroneous data, an SEU will occur in the BISER design. Neutron experimental results for a BISER design show a 10X reduction in SER compared to the conventional DFF [57].

Figure 21. Schematic of the BISER design from [52]

The BCDMR design is similar to the BISER design, but with a small change to reduce the chance of SETs generated in the latches from creating an SEU at a clock edge [57]. The BCDMR design implements C-elements at the output of the master and slave stages, shown in Figure 22. Neutron experiments show that the BCDMR designs has a ~100X lower SER than the BISER at clock frequency of 300 MHz [57].

Figure 22. Schematic of the BCDMR design from [54]

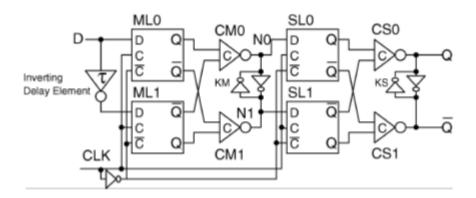

The LEAP DICE uses a DICE schematic topology but places transistors in the layout to use charge sharing to prevent SEUs [60], [61]. The LEAP principle can be applied to any circuit by increasing the charge sharing between the nFETs and pFETs that drive a circuit node. When this is done, the resulting SET becomes smaller, as shown in Figure 23. In 180-nm bulk CMOS process, the LEAP DICE had ~2000X lower SER than a standard DFF and 5X lower SER than a standard DICE FF when exposed to neutrons [61].

Figure 23. LEAP principle for an inverter with transistor alignment. (a) Reduced charge collection when a particle hits both NMOS and PMOS drain nodes of an inverter simultaneously. (b) Transistor alignment to reduce charge collection in the horizontal direction [57]

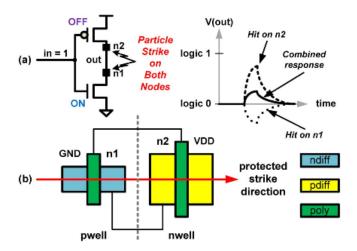

Many works have shown that multiple node charge collection from a single ion strike (charge sharing) can upset a DICE-like latch [4], [5], [8], [49], [52], [53], [63], [64]. Calin et al. showed in a 1.2 μm bulk epi process that a DICE latch can be upset in laser experiments with a upset laser energy threshold of 16.1 pJ (author estimates the LET is ~ 48 MeV-cm²/mg) [63]. By increasing the distance between sensitive node pairs in the layout, it is possible to reduce the SE cross section of a DICE-like design [5], [49], [53]. Baze et al. showed in heavy-ion experiments that a DICE-like flip-flop design with 5-μm spacing between nodes is still susceptible to angular ion strikes.

Amusan et al. showed that charge sharing causing upsets in flip-flops mostly occurs between transistors in the same well (pFET-to-pFET or nFET-to-nFET) [24], [52]. Charge sharing occurs due to drift and diffusion of carriers deposited by an ion strike and well potential modulation activating the parasitic bipolar of the MOSFET structure. The use of guard bands and separate wells helps to reduce same well charge sharing. Charge sharing across the n-well/p-well boundary is less efficient than charge sharing in the same well, thus pFET-nFET charge sharing is less of a concern than pFET-pFET or nFET-nFET charge sharing [52].

All of these studies show that there are many different ways to harden a flip-flop design. However, all of these designs are susceptible to charge sharing and well-potential modulation effects. Charge sharing and well potential modulations may improve or worsen the overall single event error rate based on the design, layout, incident particle

type, deposited charge, etc. All of these factors must be considered before choosing a design for a given environment.

### Section 1.2.D. Space and Terrestrial Environments

Different types of radiation are encountered in the space and terrestrial environments. The particles in both of these environments may either cause nuclear reactions in semiconductor materials producing secondary ionizing particles or deposit energy directly through Rutherford scattering. In either case, the end result of interest is the creation of electron-hole pairs in the semiconductor material. Since the deposited energy, and the resultant number of electron-hole pairs, is dependent on the incident particle type, it is important for the designer to understand how the charge is deposited.

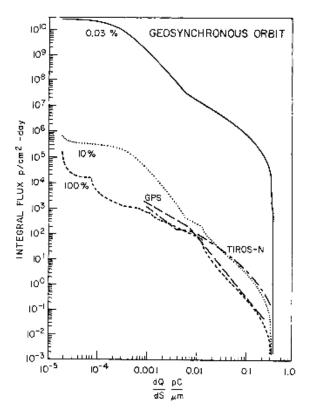

In space, one set of radiation particles of concern are heavy ionizing particles, such as iron [65]. Figure 24 shows the integral flux of the heavy-ion LET spectrum at geosynchronous orbit. There is a wide range of ionizing particles of varying LET. The higher the LET of the particle, the more charge it can deposit and the more circuit nodes that can be affected by charge sharing [66].

Figure 24. Integral energy loss spectrum at geosynchronous orbit from [62]

Protons are another radiation particle of concern in space [66]. Protons can interact with the semiconductor materials present on an IC and produce secondary ionizing particles. These secondary ionizing particles are ejected at angles within the IC and able to deposit charge near multiple transistors. At proton energies <2 MeV, direct ionization caused by protons can become a reliability issue [67]. The peak LET of low energy protons is 0.5 MeV-cm²/mg and a result, only deep-sub-micron technology node designs are vulnerable to low energy protons.

Similarly, in the terrestrial environment, neutrons are able to cause secondary particles by interacting with the nucleus of IC materials. These neutrons are produced from radiation interactions with the earth's atmosphere, and the neutron flux decreases with decreasing altitude. Again, the generated neutron secondary ions can deposit charge over a large area causing charge sharing among multiple circuit nodes [37], [46], [68], [69].

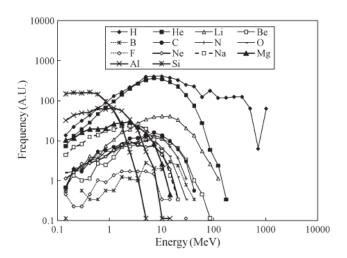

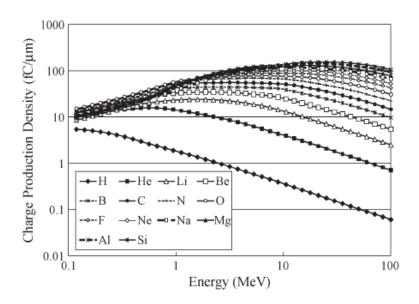

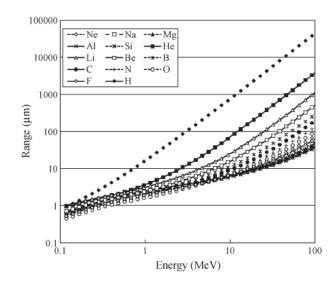

Each time a neutron or proton interacts with the nucleus of an atom (referred to as an inelastic collision), secondary particles may unpredictably be ejected in all directions, illustrated in Figure 25 [70]. Many different particles, energies, and LET values can result from a neutron event with a silicon atom, shown in Figure 26 and Figure 27 [71]. Combining these results with the distances seen in Figure 28, it is easy to see that these generated secondary particles can deposit charge across a large area.

Figure 25. MRED generated nuclear event. The shaded volumes represent the sensitive nodes of the memory device. The incident neutron enters and induces a nuclear event. The shower of secondary products includes alpha particles, protons, neutrons, gamma rays, and a carbon heavy ion  $(n + Si \rightarrow C + 3n + 2p + 3\alpha)$ . In the top-down view on bottom, the generated charges for sensitive nodes with more than 1 fC are labeled from [67]

Figure 26. Relative frequency of secondaries produced from neutron-silicon collisions versus energy at sea level in New York City from [68]

Figure 27. Density of electron-hole pairs generated in silicon [68]

Figure 28. Neutron secondary particle distances in Si vs. energy [68]

Impurities in IC packaging and the silicon wafer itself can create alpha particles and are a concern for terrestrial applications [46]. These alpha particles can travel up 100 µm in silicon and have been shown to create multiple cell upsets in SRAM cells even though they have a very low LET [25].

All these results show a need for evaluating the trends for conventional and hardened flip-flop designs at advanced technology nodes. The availability of such trends will allow designers to anticipate error rates for their latest designs without having to get

actual experimental data. Since experimental data is available only after the technology has been in use, designers often do not have any knowledge of SER values for their designs until after they are fabricated. Analysis presented in this work will allow designers to assess the vulnerability of their designs to a first degree without requiring any experimental data. Since different flip-flops designs will have different response to single events, this thesis uses multiple non-hardened and hardened designs to evaluate the SER trends for technology scaling.

#### **Section 1.3 Dissertation Overview**

As mentioned in the introduction, this works aims to characterize the SEU cross sections of both DFFs and hardened FF designs experimentally and with TCAD simulations.

Chapter 2 covers the basic 90nm bulk CMOS TCAD structure and associated compact models used for simulations.

Chapter 3 focuses on the mechanisms that affect the SEU cross section of DFF designs across a broad LET spectrum and shows where future work may need to look to find the determining factor.

In Chapter 4, the experimental and TCAD simulation SEU cross section response of hardened FF designs are examined.

Chapter 5 DFF and hardened FF SEU cross sections are compared to show both trends as technology scaling continues.

#### **CHAPTER II**

#### MOSFET SIMULATION MODELS

### Section 2.1 Overview

This chapter covers the basic MOSET models used in later 3D TCAD simulations. The MOSFET models are based on the IBM 9SF 90nm bulk CMOS technology node. The information presented here is thoroughly covered in [59], but are briefly repeated here for the reader.

#### **Section 2.2 3D TCAD MOSFET models**

Previously calibrated full 3D TCAD device models were used as baseline structures for all simulations. Calibration details are thoroughly covered in [59]. The well structure and STI depth are based on 130nm technology node, as these are expected to be similar. Model creation and heavy ion simulation are performed with Synopsys Sentaurus tools, specifically the models are built with Structure Editor and Mesh then bias and heavy ions simulations are performed by SDevice [60]. Simulations were performed on the ACCRE computing cluster at Vanderbilt University [61]. This section covers then current characteristics of the models and detailed structures of the transistors and wells.

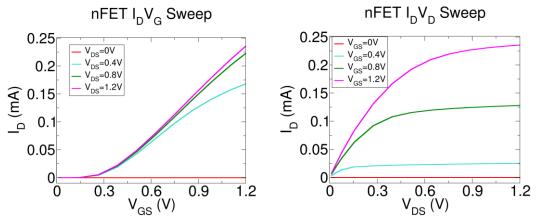

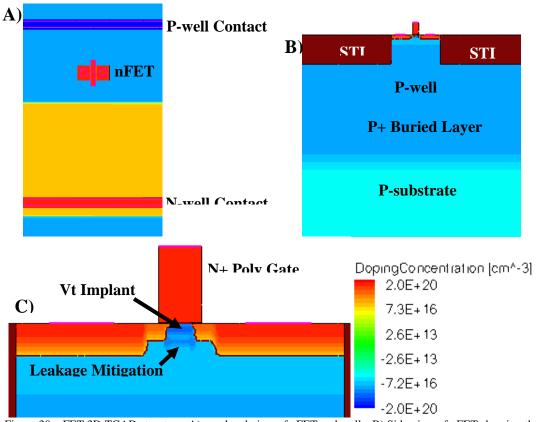

The nFET size used in all simulations has an actual channel length of 80nm and width of 280nm. The current versus voltage curves are shown in Figure 29. In Figure 30, the basic nFET, p-well, p+ buried layer, and p-substrate are shown. All doping implants are created using Gaussian profiles shown in Figure 31.

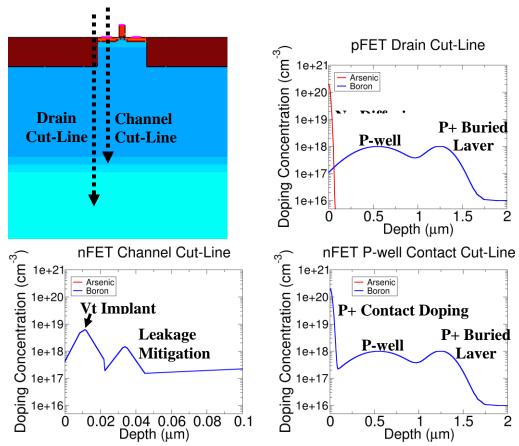

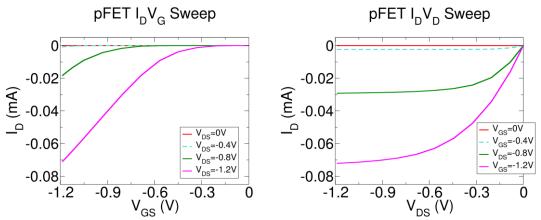

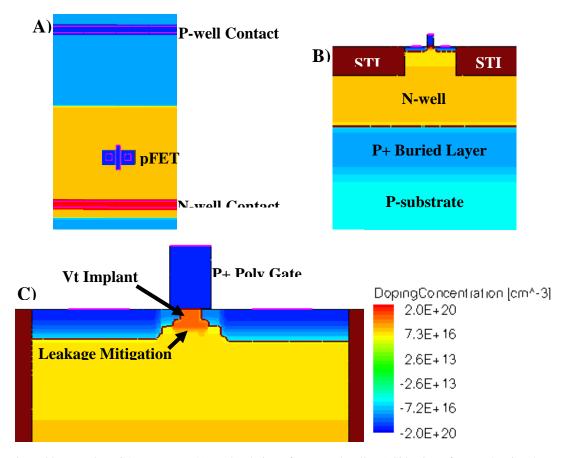

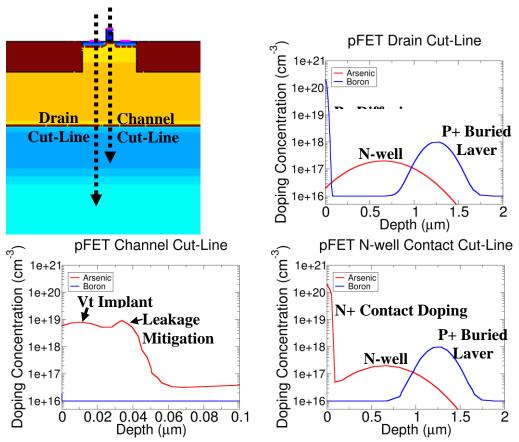

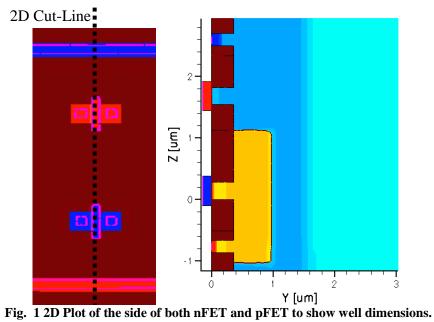

The actual length used in pFET simulations is 80nm. Two pFET widths are used, 280nm and 840nm. Current versus voltage sweeps are for a pFET with 280nm width are shown in Figure 32. The basic pFET, n-well, p+ buried layer, and p-substrate are displayed in Figure 33. Gaussian doping profiles versus depth are contained in Figure 34.

Figure 29. Current versus voltage sweeps for a nFET with L=80nm and W=280nm.

Figure 30. nFET 3D TCAD structure. A) overhead view of nFET and wells. B) Side view of nFET showing the P-well, P+ buried layer, and P-substrate. C) Close-up view of nFET.

Figure 31. 1D cut-line showing the doping concentration versus depths at various locations of the nFET structure.

Figure 32. Current versus voltage sweeps for a pFET with L=80nm and W=280nm.

Figure 33. pFET 3D TCAD structure. A) overhead view of pFET and wells. B) Side view of pFET showing the Nwell, P+ buried layer, and P-substrate. C) Close-up view of pFET.

Figure 34. 1D cut-line showing the doping concentration versus depths at various locations of the pFET structure.

### **CHAPTER III**

## COMPARISON OF NORMAL INCIDENCE HEAVY-ION DFF and HARD-FF SEU CROSS SECTIONS AND MECHANISMS

### Section 3.1 Overview

In section 1.2, it was shown that different models predict different trends for DFF SEU cross sections as technologies scale. This chapter begins by exploring mechanisms that can change the SEU cross section of DFFs through TCAD simulations by varying common parameters that would change when technologies scale by applying them to the 90-nm TCAD models described in chapter 2. In these simulations, the extent from the vulnerable FET in a latch is analyzed versus changing technology process parameters in the well. Then, DFF and Hard-FF normal incidence heavy-ion experimental results are compared.

The process parameters that vary with process that are analyzed include: maximum transistor drive current, well doping, well depth, well width, well contact spacing, and upset reversal. These are all parameters that can have a major impact on the SET response of a circuit. Also, all these parameters can influence the effects of other parameters on SEU cross sections.

The chapter ends by comparing experimental results for DFF designs to narrow down which mechanisms may be dominating the SEU cross section response for various LET values.

### **Section 3.2 DFF and Hard-FF TCAD Simulation Setup**

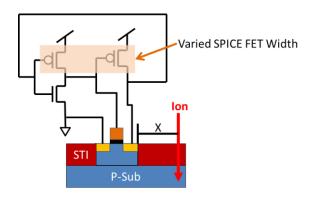

The 90-nm 3D TCAD models described in chapter are used for the following simulations. Mixed-mode simulations will be used where 1 or 2 FETs from the latch will be simulated in the physical portion of the simulation, while the remaining FETs in the latch will be simulated in SPICE. Multiple ion strikes with increasing distance from the edge of the drain for the vulnerable FET are simulated to find the greatest extent an ion strike will cause an upset for changes to a given process parameter, shown in Figure 35. Unless otherwise stated, all ion strikes have an LET 58 MeV-cm<sup>2</sup>/mg (0.58 pC/µm). The process parameter will be varied in a way to mimic changes that would occur as technology feature sizes become smaller.

For simulations utilizing a single FET in the physical portion of the simulation of the latch, a 3D model is used. When 2 or more FETs are simulated in the physical portion of the simulation, 2D models are used to reduce simulation time and overcome any convergence issues. It is important to note that using the 2D simulations may enhance any charge sharing that may occur in the physical simulation, but will not affect the results as only 2D simulations will be not be compared to 3D simulations.

Figure 35. Illustration of the 3D TCAD simulation setup to strike a single nFET in a latch.

# **Section 3.3 Transistor Drive Current**

One goal of technology is to reduce power consumption by decreasing transistor drive currents. By decreasing the transistor drive currents, the amount of charge needed to cause an upset becomes much smaller thus potentially increasing the SEU cross section of a FF [2].

To examine this effect in 3D TCAD simulations, the width of the transistors opposite of the transistor being struck in the physical simulation had the widths shrunk to mimic decreasing transistor current strengths with scaling. If the nFET is in the physical portion of the mixed-mode simulation, the pFETs in the latch that are in the circuit simulation portion had their widths changed, as illustrated in Figure 36. Table 3 shows the parameters that are kept constant in the simulation while the transistor width is changed.

Figure 36. Illustration of a nFET being simulated in the physical portion of the simulation and the pFET widths are varied to emulate decreasing FET drive currents with scaling.

Table 3. Simulations parameters kept constant when changing the transistor width.

| Sim Parameters                    |       |

|-----------------------------------|-------|

| P-well doping (cm <sup>-3</sup> ) | 1E+18 |

| N-well doping (cm <sup>-3</sup> ) | 5E+17 |

| Well Depth (um)                   | 0.7   |

| STI Depth (um)                    | 0.33  |

| Well Contact                      | Strip |

| Buried P+                         | Yes   |

| $W_P = W_N$                       |       |

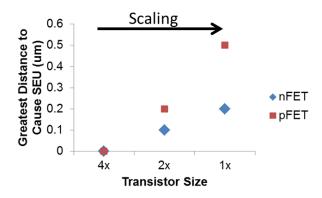

The simulation results are shown in Figure 37. As expected, as the transistor width decreases (transistor current decreases with scaling) the extent at which an ion strike can cause an SEU in the latch increases. There is a difference in the rate of increase of extent of SEU distance versus FET width is different for nFETs and pFETs. The nFET increase in extent of SEU distance increases linearly with decrease in transistor current, but the pFET increase is almost quadratic. The difference in the nFET and pFET trends is due to the WPM activating the pFET bipolar. As shown in [62], the WPM effect is negligible for strikes in p-wells compared to n-wells. In addition, these results indicate that the voltage at which the well potential must drop to cause an SEU in a latch will change based on the driving current of the restoring transistors connected to the vulnerable FETs. This is important because the WPM will play major role in the SEU cross section response for vulnerable pFETs compared to nFETs as technologies scale for dual well technologies.

Figure 37. 3D TCAD simulations results showing the greatest extent from the drain an ion strike with a LET of 58 MeV-cm2/mg will cause an SEU in the latch vs. transistor width.

## **Section 3.4 Well Doping Concentration**

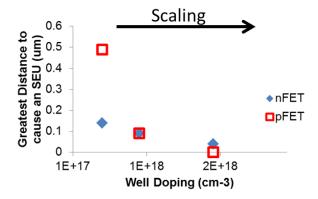

Another parameter that changes as technologies scale is well doping concentration which helps reduce latchup and substrate noise issues. The well doping concentration is increased to improve the latchup immunity and substrate noise as technology feature sizes become smaller. As shown in [62] the well doping can be a major parameter determining the WPM response during an SE and decreases with higher well doping concentrations.

The 3D TCAD simulation used to explore this effect focused on changing the peak well doping concentration while forcing the doping concentration at depth to remain the same so transistor and well junction parameters remain unaffected.

Table 4 shows the parameters that were held constant when the peak well doping concentration was varied.

As the well doping concentration increases, the greatest distance from the center of the drain region from which an ion strike can cause an SEU decreases as shown in Figure 38. Strike distance from the drain in the n-well show a much larger decrease with increasing doping than the p-well; this follows the same trend as the decreasing WPM extent seen in [62]. Well doping concentration increases can decrease the SEU cross section of a DFF by decreasing WPM effects in the n-well by decreasing the well resistance to the well contacts.

Table 4. Common simulations parameters while peak well doping concentration was changed.

| Sim Paramters   |       |

|-----------------|-------|

| Well Depth (um) | 0.7   |

| STI Depth (um)  | 0.33  |

| Well Contact    | Strip |

| Buried P+       | Yes   |

| $W_P = 2*W_N$   |       |

Figure 38. Greatest extent that can cause an SEU in a latch vs. well doping.

## Section 3.5 Well Depth

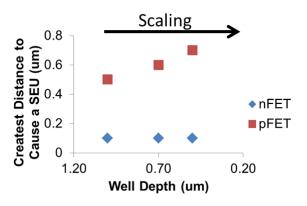

To reduce latchup effects as technology feature sizes become smaller, well depths are decreased to reduce the gain of the n-well/p-well junction [62]. Decreasing the well depth reduces the area of the n-well/p-well junction reducing the current gain of the latchup structure. This will affect the WPM of the well by changing the resistance from ion strikes to well contacts and changing the bipolar response of multiple transistors.

In Figure 39, the nFET shows no change in SEU distance vs. well depth, but there is a change in the pFET distance; this is again due to the pFETs being located in a constrained n-well, unlike the nFETs in the p-well and p-substrate. Table 5 shows the parameters that remained constant while changing the well depth. Thus, as technologies scale, the well depth will decrease causing a wider WPM area in constrained n-wells and potentially increasing the SEU cross section of a DFF.

Figure 39. Greatest extent that can cause an SEU in a latch vs. well depth.

Table 5. Common simulations parameters while well depth was changed.

| Sim Parameters                    |       |

|-----------------------------------|-------|

| P-well doping (cm <sup>-3</sup> ) | 1E+18 |

| N-well doping (cm <sup>-3</sup> ) | 5E+17 |

| STI Depth (um)                    | 0.33  |

| Well Contact                      | Strip |

| Buried P+                         | Yes   |

| $W_P = 2*W_N$                     |       |

### **Section 3.6 Well Width**

Ever improving ion implantation methods and reducing transistors sizes allows designers to reduce well sizes as technology feature sizes decrease. Changing the well width impacts the resistance from an ion strike to well contacts and affects the WPM response, which in turn affects the bipolar response of transistors.

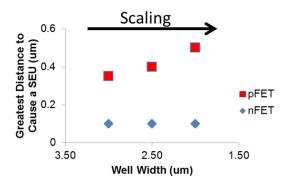

In Figure 40, the nFET response to changing the p-well width does not affect the SEU response of the DFF, but the pFET response does show sensitivity to shrinking the well width. Table 6 shows the parameters that remained constant while the well width was changed. Again, decreasing the well conductivity to the well contacts causes an increase in the WPM area and increases the DFF cross section for constrained well structures. As technologies scale, shrinking the well width can cause a DFF SEU cross section to increase.

Figure 40. Greatest extent that can cause an SEU in a latch vs. well width.

Table 6. Common simulations parameters while well width was changed.

| Sim Parameters                    |       |

|-----------------------------------|-------|

| P-well doping (cm <sup>-3</sup> ) | 1E+18 |

| N-well doping (cm <sup>-3</sup> ) | 5E+17 |

| STI Depth (um)                    | 0.33  |

| Well Contact                      | Strip |

| Buried P+                         | Yes   |

| $W_P = 2*W_N$                     |       |

## Section 3.7 Transistor Spacing from N-well/P-well Boundary

As technologies scale, it is possible for designers to decrease spacing between transistors and the n-well/-well boundary. Decreasing the distance between a transistor from the n-well/p-well boundary can reduce the amount of minority carrier current collected by a transistor [63].

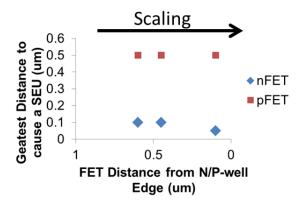

In Figure 41, the pFET shows no change in the extent an SEU with decreasing distance to the n-well and p-well boundary, but the nFET simulations show a small decreasing trend in the extent to cause an SEU with decreasing distance between the n-well/p-well boundary. Table 7. Common simulations parameters while n-well/p-well boundary spacing was changed. Again, the WPM response plays a role in determining the SEU response of pFETs; the distance of a pFET will not have a significant change to the WPM response of an ion strike near the pFET and will collect the same amount of charge because the WPM response is not changed because the resistance to the well contacts remains the same. As technologies scale, the distance between nFETs and the n-well/p-well boundary will decrease and lead to small decreases in the SEU cross section of DFFs.

Figure 41. Greatest extent that can cause an SEU in a latch vs. spacing to n-well/p-well boundary.

Table 7. Common simulations parameters while n-well/p-well boundary spacing was changed.

| Sim Parameters                    |       |

|-----------------------------------|-------|

| P-well doping (cm <sup>-3</sup> ) | 1E+18 |

| N-well doping (cm <sup>-3</sup> ) | 5E+17 |

| STI Depth (um)                    | 0.33  |

| Well Contact                      | Strip |

| Buried P+                         | Yes   |

| $W_P = 2*W_N$                     |       |

# **Section 3.8 Well Contact Spacing**

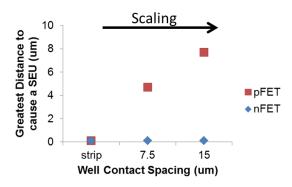

As technologies feature sizes decrease, spacing between well contacts can increase (or maximum distance from a well contact to a transistor can increase). This allows for higher transistor densities. To mitigate latchup issues, designers can chose to increase well contact density [62]. Changes to well contact spacing have a major impact on the WPM of a constrained well due to an ion strike.

In Figure 42, the nFET SEU response shows no sensitivity to the well contact spacing, but the pFET response shows a major change in the SEU response due to WPM. The nFETs are not affected by WPM because of the p-well being connected to the p-substrate, but the n-well in constrained and changing the well contact spacing can easily change the resistance to an ion strike from the well contact affecting the restoring current to and WPM response. As technologies scale, the well contact spacing can increase causing the well resistivity from ion strike location to increase and potentially increase a DFF SEU cross section.

Figure 42. Greatest extent that can cause an SEU in a latch vs. spacing between contacts.

Table 8. Common simulations parameters while spacing between well contacts was changed.

| P-well doping (cm <sup>-3</sup> ) | 1E+18 |

|-----------------------------------|-------|

| N-well doping (cm <sup>-3</sup> ) | 5E+17 |

| Well Depth (um)                   | 0.7   |

| STI Depth (um)                    | 0.33  |

| Buried P+                         | Yes   |

| $W_P = 2*W_N$                     |       |

# Section 3.9 Normal Incidence Heavy-Ion Experimental Results of Flip-Flops in 40-nm, 28-nm, and 20-nm

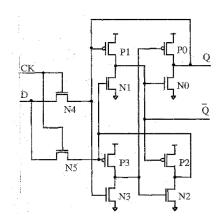

To compare the effects of technology on a scaled flip-flop design, experiments were conducted on the 40-nm, 28-nm, and 20-nm test chips. Tests were conducted at nominal supply voltages (0.9 V for 40-nm, 0.85 V for 28-nm, and 0.9 V for 20-nm) at a clock frequency of 10 MHz and a constant data input stream of either all ones or all zeroes. The same relative transistor placement was used in all three test chips, but the design is shrunk with respect to technology parameters, for example transistor pitch, gate length, and transistor width are decreased. The schematic of the standard latch used in all three test chips to make a master-slave flip-flop is shown in Figure 43.

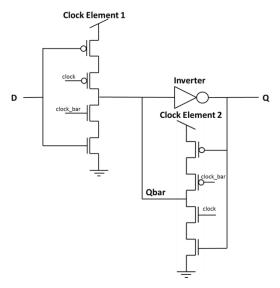

Figure 43. Schematic of the latch used to create the master/slave flip-flop on the three test chips.