# ON THE IMPACT OF DEVICE ORIENTATION ON THE MULTIPLE CELL UPSET RADIATION RESPONSE IN NANOSCALE INTEGRATED CIRCUITS

By

Alan Douglas Tipton

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

#### DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

December, 2008

Nashville, Tennessee

Approved:

Professor Ronald D. Schrimpf

Professor Lloyd W. Massengill

Professor Robert A. Reed

Professor Robert A. Weller

Professor Kalman Varga

For Mom and Daddy — you made this possible.

#### ACKNOWLEDGEMENTS

To days of inspiration, playing hookey, making something out of nothing, the need to express, to communicate.

-Jonathan Larson, Rent

This work would not have been possible with out the support of others. Therefore, I would like to acknowledge the contributions of those who made this possible.

To begin I would like to thank my advisor and committee chair Prof. Ronald Schrimpf for his guidance since my days as an undergraduate. I would like to thank Profs. Robert Reed and Robert Weller for their support and counsel on all my work. Thank you to my committee Prof. Lloyd Massengill, Prof. Robert Reed, Prof. Ronald Schrimpf, Prof. Norman Tolk, and Prof. Robert Weller.

Many thanks are due to Texas Instruments, especially Rob Baumann and Xiaowei Zhu who provided the devices for this work. Also, thanks to NASA/GSFC, especially Michael Xapsos, for their support in testing the hardware. I would like to acknowledge Ken LaBell of NASA/GSCF and Lew Cohn of the Defense Threat Reduction Agency for their sponsorship of this work.

For their help when I needed it, thanks to Christina Howe, Jonny Pellish, and Patrick Fleming; you are not just great colleagues, but you are also great friends. To Prof. Marcus Mendenhall, Kevin Warren, and Dennis Ball thanks for your assistance. Thanks to the faculty and students of the Radiation Effects and Reliability group. For the love and support of my family, thank you Mom, Daddy, Jess, and Chrissy. Thanks also to the Roderic Murray whose encouragements were so beneficial.

Thanks to you all.

Alan Tipton Nashville, TN November 11, 2008

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS | iii  |

|------------------|------|

| LIST OF TABLES   | vii  |

| LIST OF FIGURES  | viii |

## Chapter

| I.   | INTRODUCTION                   |

|------|--------------------------------|

|      | The Integrated Circuit         |

|      | Radiation Effects              |

|      | The Multiple Cell Upset        |

|      | Summary of this Work           |

| II.  | BACKGROUND                     |

|      | Single Event Effects (SEEs)    |

|      | Sources of SEEs                |

|      | Types of SEEs                  |

|      | SEE Mechanisms                 |

|      | SEE – SRAM upset               |

|      | The Multiple Cell Upset        |

|      | Heavy Ion Induced MCU          |

|      | Nucleon Induced MCU            |

|      |                                |

|      | Summary                        |

| III. | MULTIPLE CELL UPSET ANALYSIS   |

|      | Single Event Upset             |

|      | 0 1                            |

|      |                                |

|      | Probability of MCU             |

|      | MCU Dimension Analysis         |

|      | Summary                        |

| IV.  | NEUTRON MCU RADIATION RESPONSE |

|      | Experimental                   |

|      | Single Event Upset Response    |

|      | Multiple Cell Upset Response   |

|      | $\frac{1}{1}$                  |

|       | Probability of MCU                                                                                                                                     | 31<br>31                                                                         |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| V.    | HEAVY ION MCU RADIATION RESPONSE                                                                                                                       | 34                                                                               |

|       | Experimental       Single Event Upset Response         Multiple Cell Upset Response       Probability of MCU         MCU Dimension       MCU Dimension | 34<br>35<br>37<br>39<br>42<br>44<br>48                                           |

| VI.   | MODELING MCU                                                                                                                                           | 56                                                                               |

| VII.  | Monte-Carlo Simulation                                                                                                                                 | 57<br>59<br>61<br>62<br>64<br>64<br>74<br>80<br>81<br>81<br>82<br>83<br>83<br>85 |

| VIII. | CONCLUSIONS                                                                                                                                            | 88                                                                               |

| Appe  | ndix                                                                                                                                                   |                                                                                  |

| A.    | HEAVY ION DIMENSION PLOTS                                                                                                                              | 91                                                                               |

| B.    | MRED CODE                                                                                                                                              | .00                                                                              |

| REFE  | RENCES                                                                                                                                                 | .09                                                                              |

## LIST OF TABLES

| Table |                                                                                                                              | Pa | age |

|-------|------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 1.    | Average size of MCU clusters from neutron irradiation                                                                        | •  | 31  |

| 2.    | LET for experimental ions at the surface of the die and the estimated LET at the silicon surface for each angle of incidence |    | 37  |

## LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

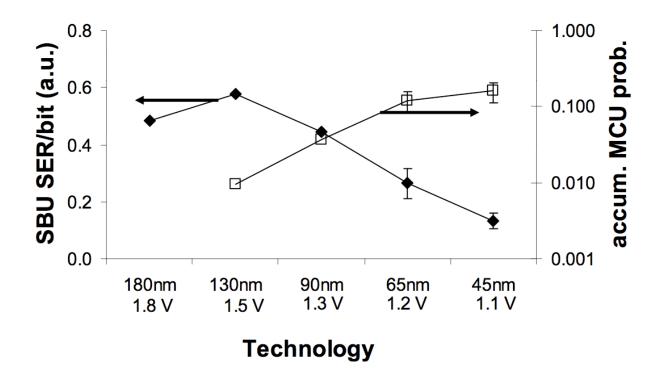

| 1.     | The neutron–induced bit soft error rate for Intel's 180 nm–45 nm tech-<br>nology nodes decreases with each new generation. The probability<br>of MCU increases with each new generation because higher device<br>densities places sensitive nodes closer together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

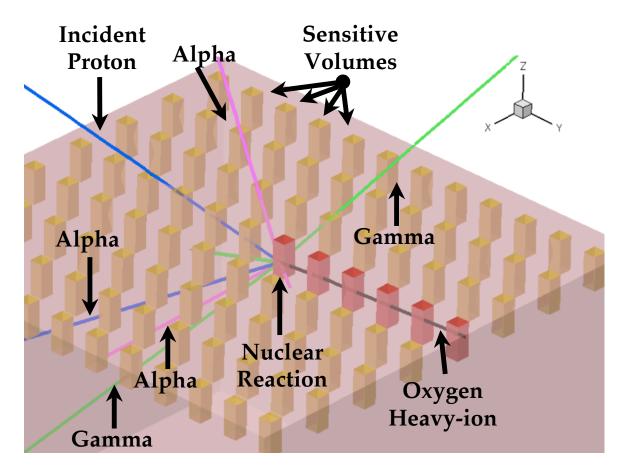

| 2.     | A TCAD representation of an MRED generated nuclear event for a 63 MeV proton incident at a grazing angle in silicon with the sensitive volumes shown by the shaded boxes. The overlayers have been omitted. The secondary products from the reaction are a 14 MeV oxygen ion, a proton, gamma rays, and alpha particles. The oxygen heavy ion transverses six sensitive volumes of SRAM cells.                                                                                                                                                                                                                                                                                                                                    |      |

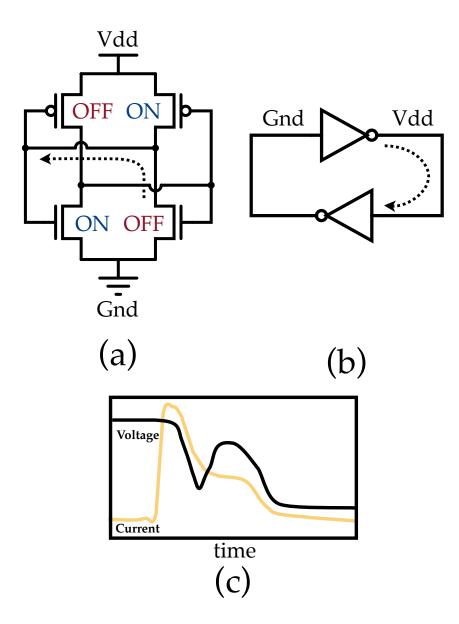

| 3.     | (a) A circuit schematic diagram of an SRAM formed by two cross-<br>coupled inverters. The ON and OFF state devices are labeled for one<br>possible state of the SRAM. The feedback path of a strike to the drain<br>of the OFF n–MOSFET device is shown by the dotted line. (b) The<br>logic diagram of the circuit shows the feedback path of a transient<br>strike indicated by the dotted line. (c) The current and voltage tran-<br>sients at the node of the OFF n–MOSFET are illustrated. The initial<br>current pulse drops the voltage at the node. The ON p–MOSFET at-<br>tempts to restore the state of the node. The feedback of the initial<br>strike and the additional collected charge eventually result in an SEU |      |

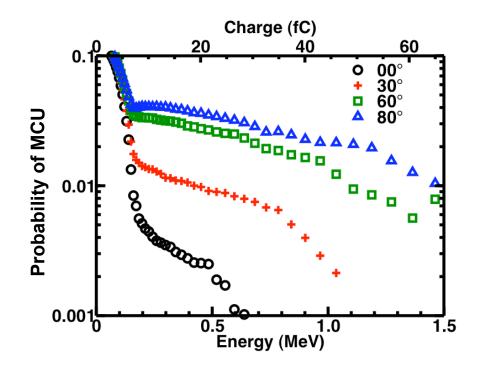

| 4.     | The probability of MCU from 63 MeV protons increases with the angle of proton incidence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

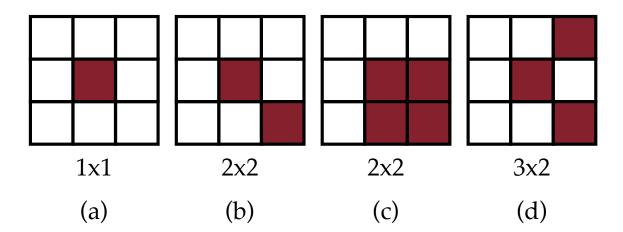

| 5.     | (a) MCU dimension is illustrated for SCU events. All SCU events are $1 \times 1$ events. (b) and (c) MCU events with dimension $2 \times 2$ are illustrated for two different event types. While their dimensions are the same, (b) is a 2-bit event and (c) is a 4-bit event. (d) A $3 \times 2$ 3-bit upset is illustrated                                                                                                                                                                                                                                                                                                                                                                                                      |      |

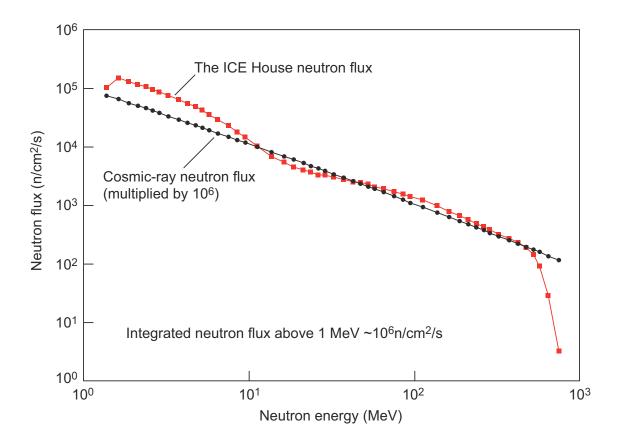

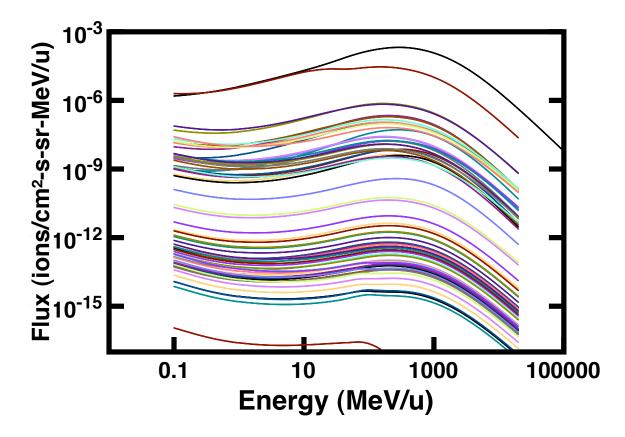

| 6.     | Ground–level neutron flux scaled by a factor of 10 <sup>6</sup> and the ICE<br>House neutron flux at WNR. The ICE House beam closely tracks the<br>ground–level flux out to approximately 600 MeV and then rapidly<br>falls off for higher energies [82]                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

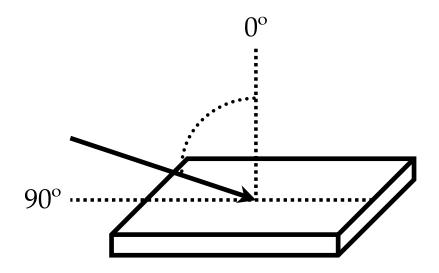

| 7.  | The device orientation is illustrated for neutrons incident on the device. The arrow indicates the direction of incidence as measured from normally incident $0^{\circ}$ neutrons. At the largest grazing angle, $90^{\circ}$ , the test board is rotated so that neutrons are not directly incident on the device surface. Rather, they are incident on the edge of the test board.                                                              | 28 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

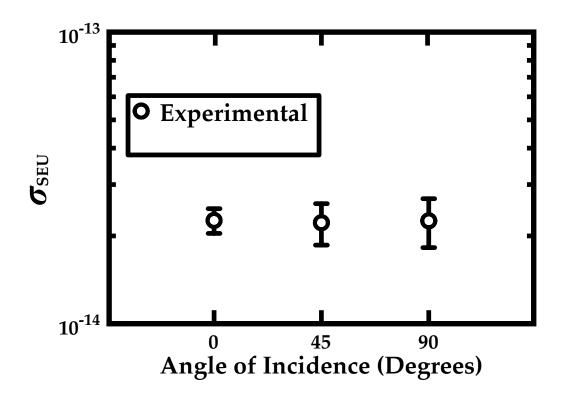

| 8.  | The experimental SEU cross section $\sigma_{SEU}$ is plotted for the three different rotation angles. The SEU response varies little with the orientation of the device. The error bars represent the counting statistics and the error associated with the beam fluence.                                                                                                                                                                         | 29 |

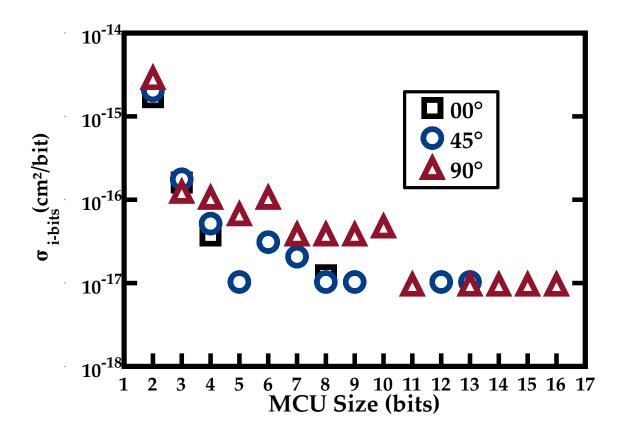

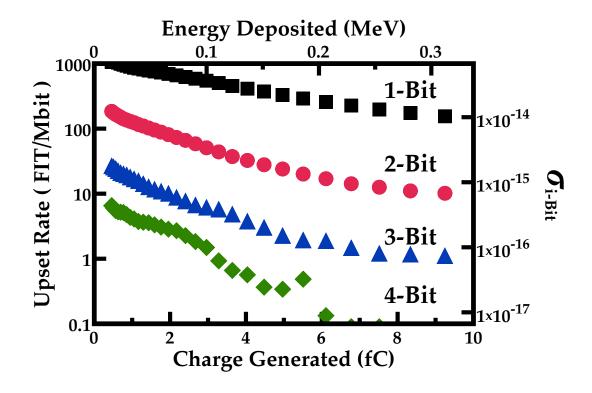

| 9.  | The $\sigma_{i-\text{bits}}$ is shown for MCU events larger than two-bits. The greatest number of MCU events and largest sized MCU events are seen at the largest angle of incidence, 90°. The average MCU size for MCUs greater than two bits is 3.4, 5.2, and 6.4 for 0°, 45°, and 90°, respectively.                                                                                                                                           | 30 |

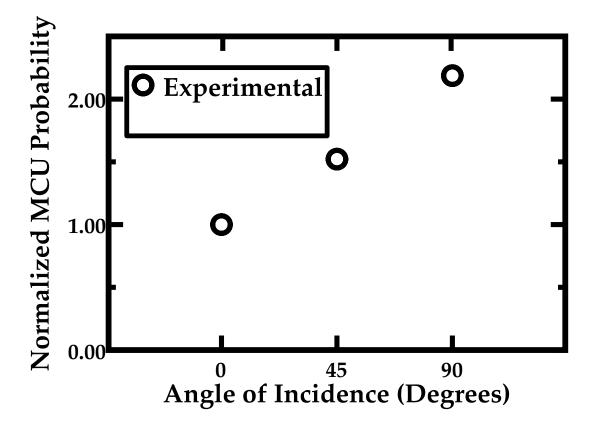

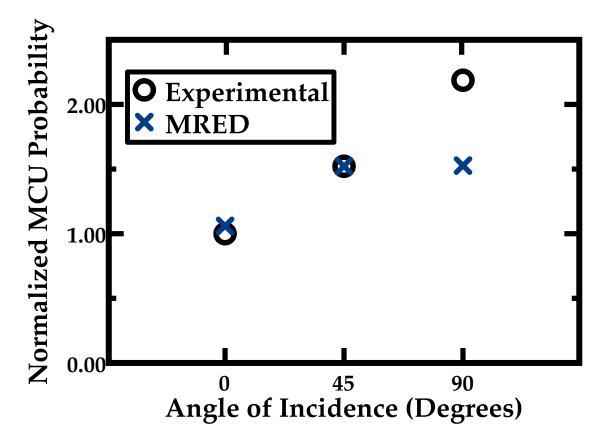

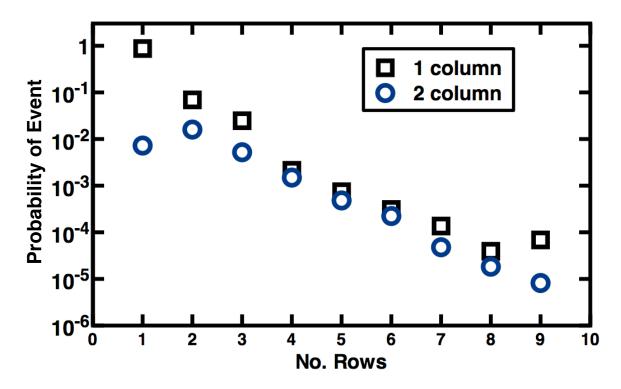

| 10. | The probability of MCU is shown for the three angles of irradia-<br>tion normalized to neutrons at normal incidence. The probability<br>increases at grazing angles with the highest probability seen at the<br>largest grazing angle, 90°. In contrast to the $\sigma_{\text{SEU}}$ , the probability of<br>MCU depends on the orientation of the device with respect to the<br>beam.                                                            | 32 |

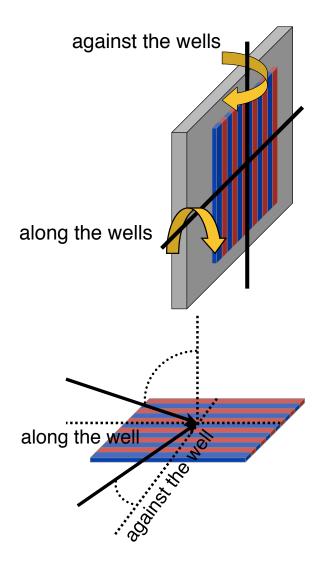

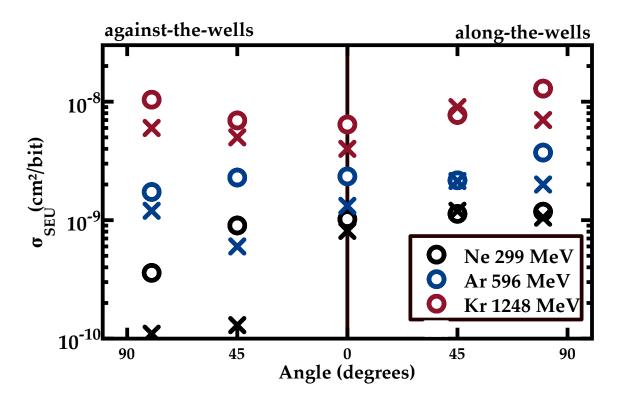

| 11. | (top) The test board was rotated about the x-axis and y-axis. The alternating blue and red columns represent the n- and p-wells of the die. The two die orientations are defined from the wells. Rotation in the direction of the wells is called "along-the-wells" rotation while rotation in the perpendicular direction are called "against-the-wells" rotation. (bottom) The trajectories of incident ions is shown for the two orientations. | 36 |

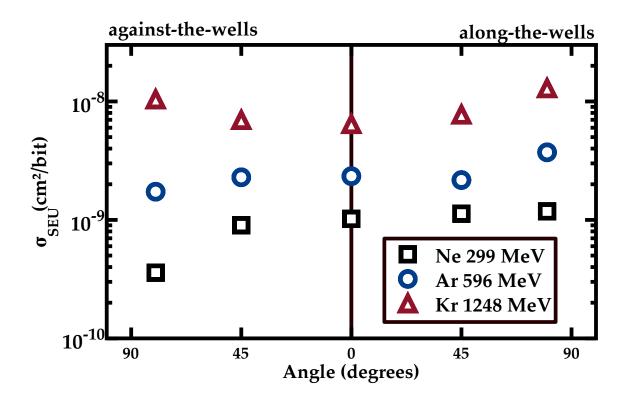

| 12. | The single event upset cross section, $\sigma_{SEU}$ , increases with LET and varies little with the orientation of the device. Cross sections are plotted for both device orientations. LET values are taken at the top of the device.                                                                                                                                                                                                           | 38 |

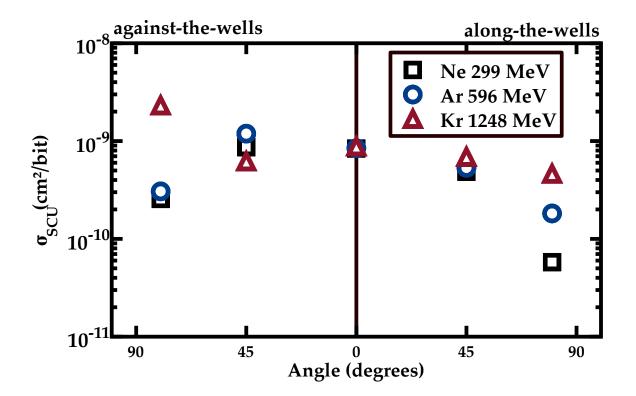

| 13. | The single–cell upset cross section, $\sigma_{SCU}$ , is plotted for both device orientations. In contrast to the SEU response, $\sigma_{SCU}$ varies for each orientation. Reduced cross sections are observed at large angles of incidence because heavy ions at these angles have higher probabilities of MCU (see Fig. 15).                                                                                                                   | 39 |

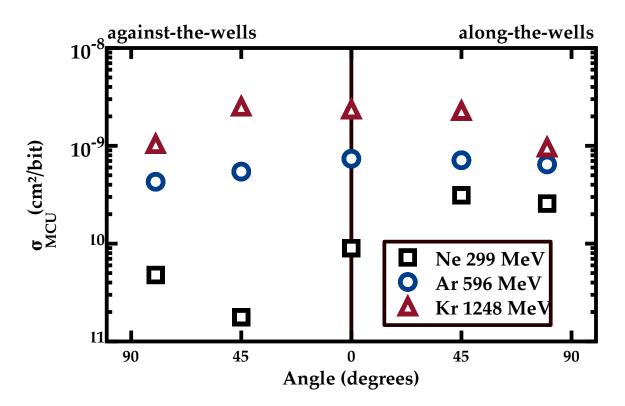

| 14. | The multiple–cell upset cross section, $\sigma_{MCU}$ , is plotted for both device orientations. The MCU response for the lightly ionizing <sup>20</sup> Ne exhibits variation for different device orientations. The shorter cell pitch in the along the wells directions increases $\sigma_{MCU}$ .                                                                                                                                             | 41 |

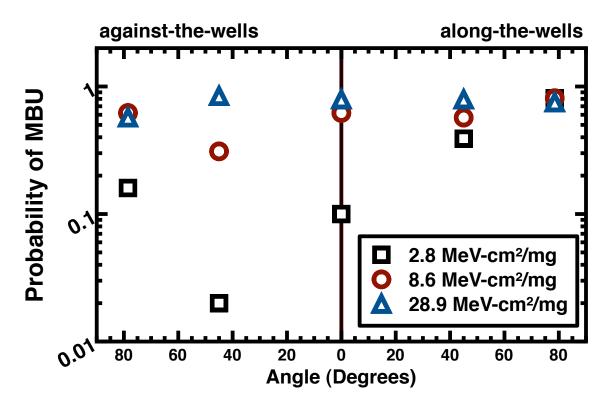

| 15. | The probability of MBU is plotted for the against-the-wells orienta-<br>tion (left) and the along-the-wells orientation (right). The probability<br>approaches 100% at large angles of incidence because the ion trajecto-<br>ries travel through more cells. The against-the-wells rotations exhibit<br>lower probability for lightly ionizing ions because they produce less<br>charge and the cell pitch is larger for these rotations | 43 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

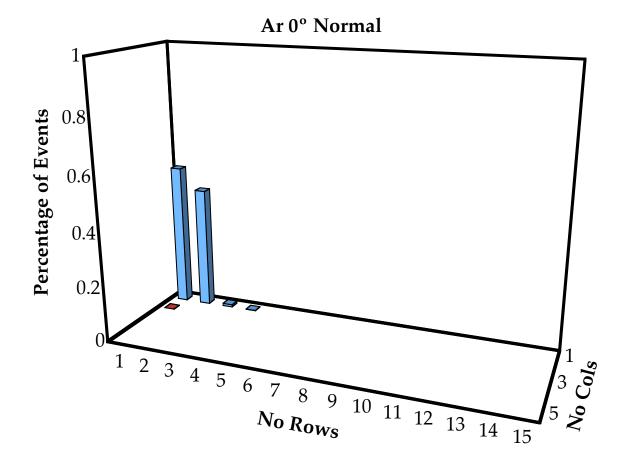

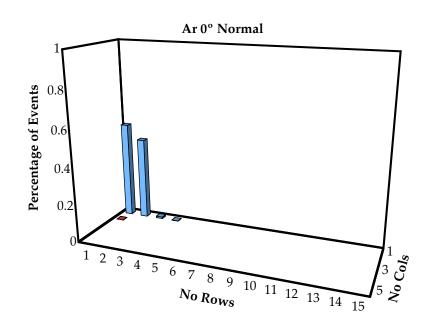

| 16. | Normalized counts of MCU events for ${}^{40}$ Ar at 0°. The majority of events are 1 × 1 single–cell upsets. Single and double–bit upsets account for 98% of all events at this orientation.                                                                                                                                                                                                                                              | 44 |

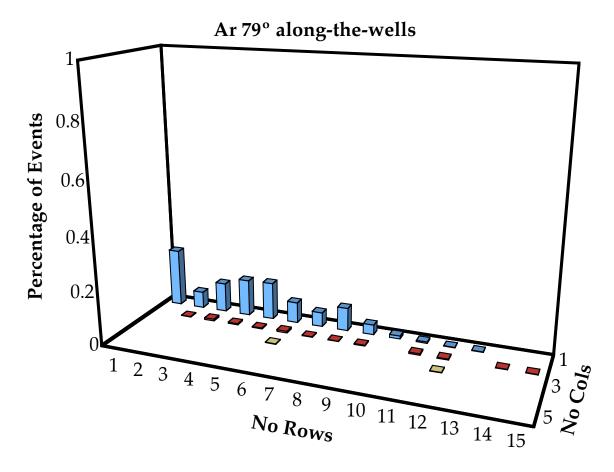

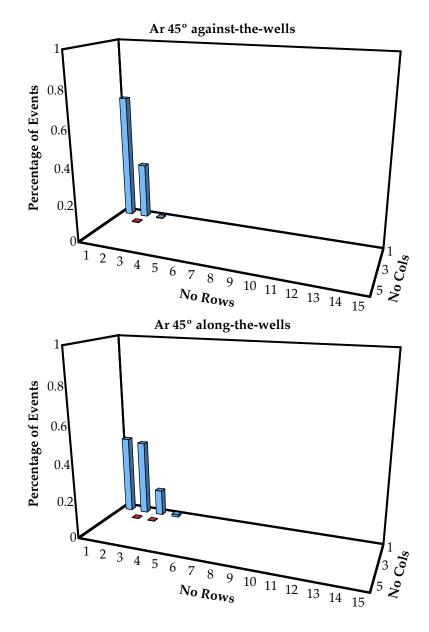

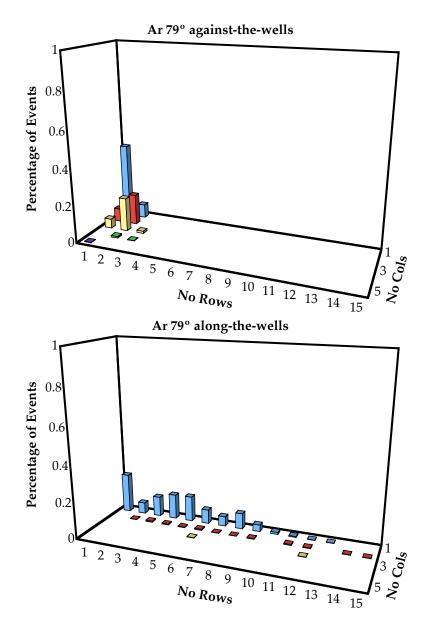

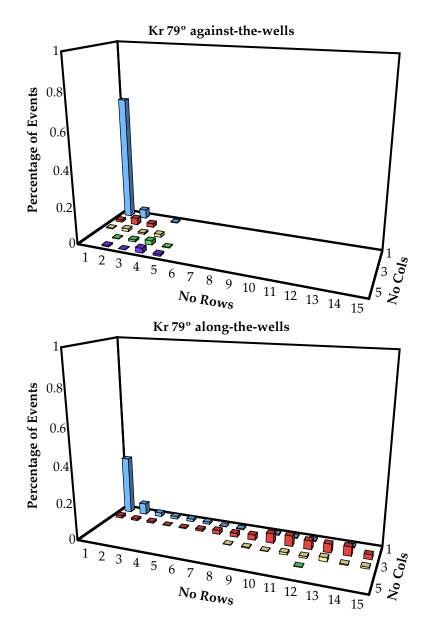

| 17. | Normalized counts of MCU events for <sup>40</sup> Ar at the worst case 79° in the along–the–wells direction are shown for the number of affected rows and columns. MCU events at this orientation affect primarily one column because the trajectories of the heavy ions is parallel to the SRAM columns                                                                                                                                  | 46 |

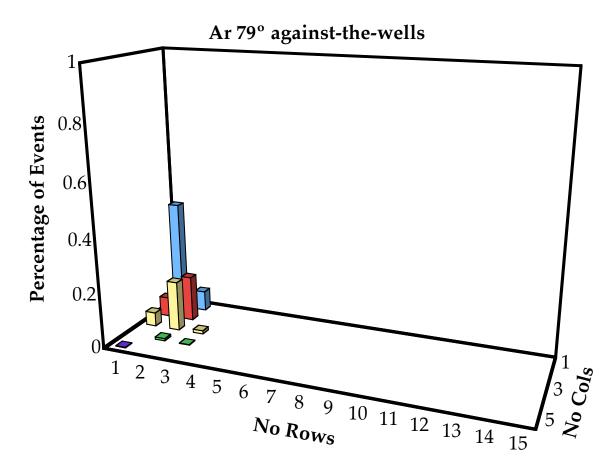

| 18. | Normalized counts of MCU events for <sup>40</sup> Ar at worst case 79° in the against–the–wells direction are shown for the number of affected rows and columns. The trajectories of heavy ions is parallel to the rows in this direction.                                                                                                                                                                                                | 47 |

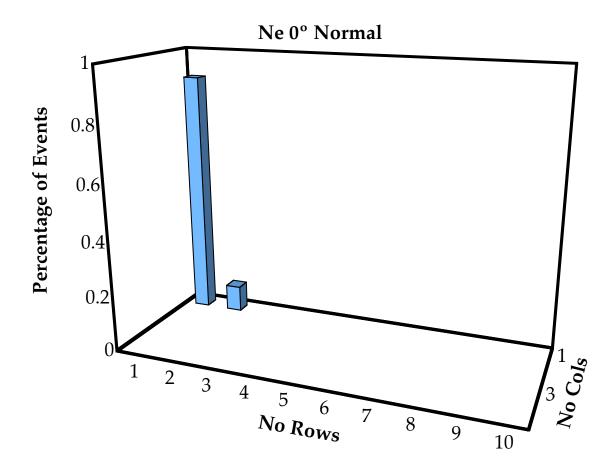

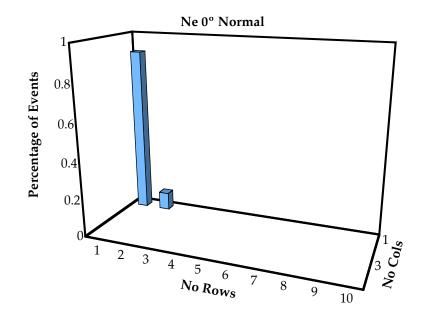

| 19. | Ne ions incident at $0^{\circ}$                                                                                                                                                                                                                                                                                                                                                                                                           | 49 |

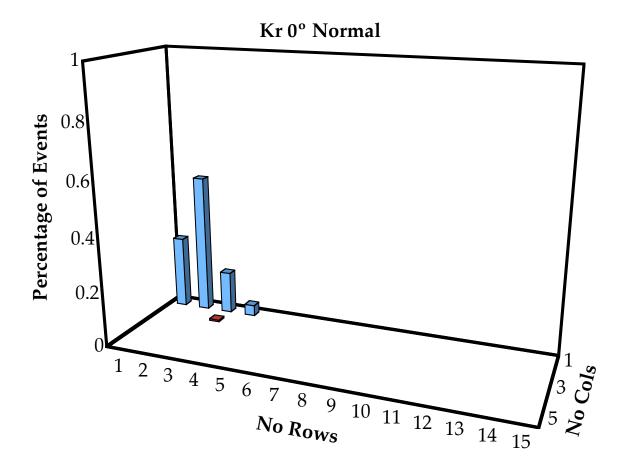

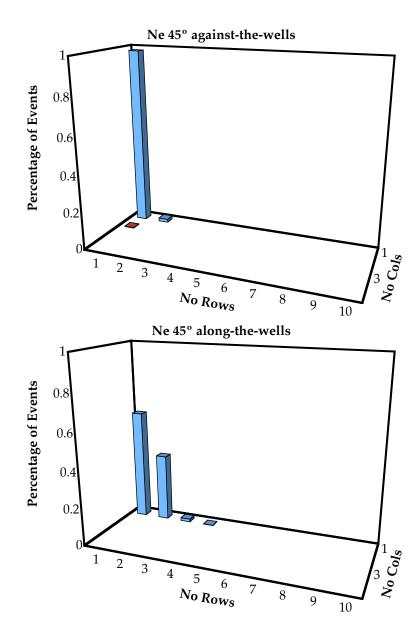

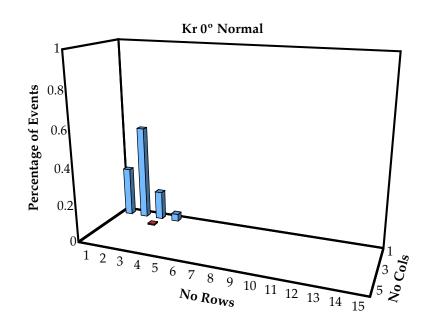

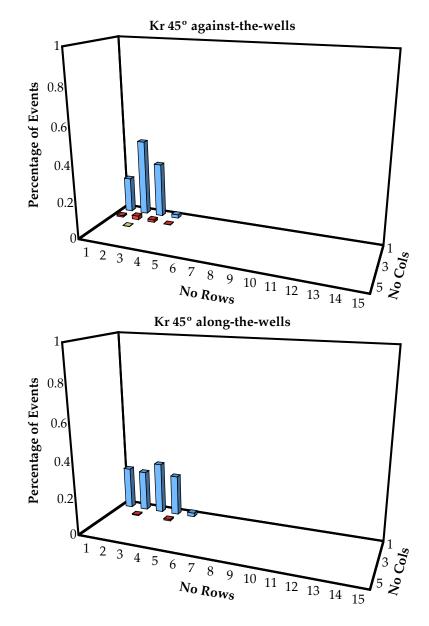

| 20. | Kr ions incident at $0^{\circ}$                                                                                                                                                                                                                                                                                                                                                                                                           | 50 |

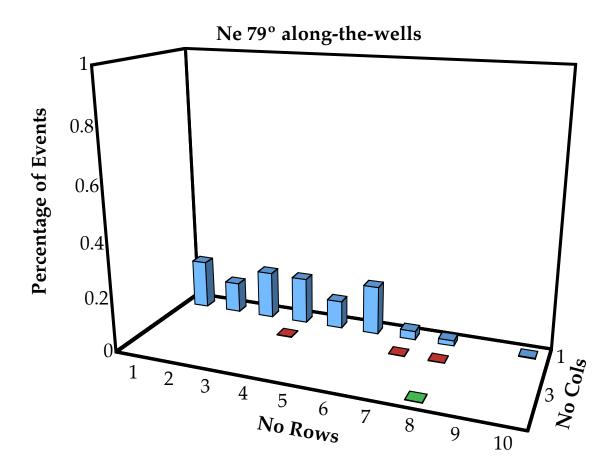

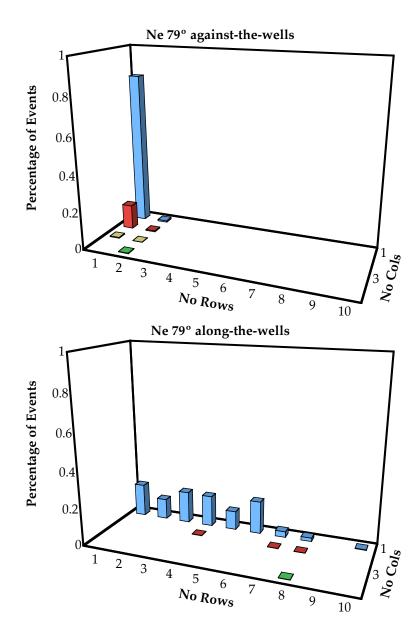

| 21. | Ne ions incident at 79° along–the–wells                                                                                                                                                                                                                                                                                                                                                                                                   | 51 |

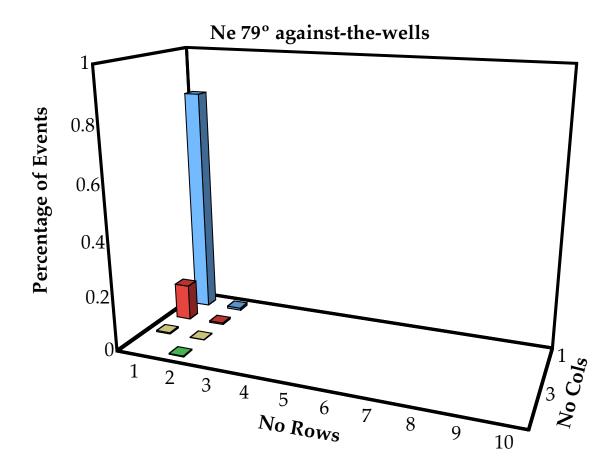

| 22. | Ne ions incident at 79° against–the–wells                                                                                                                                                                                                                                                                                                                                                                                                 | 52 |

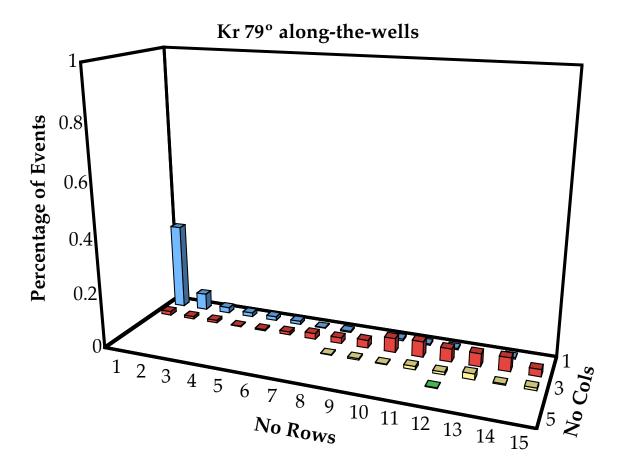

| 23. | Kr ions incident at 79° along–the–wells                                                                                                                                                                                                                                                                                                                                                                                                   | 53 |

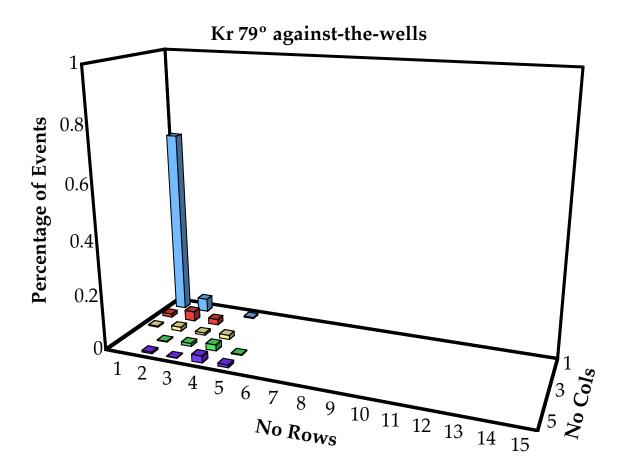

| 24. | Kr ions incident at 79° against–the–wells                                                                                                                                                                                                                                                                                                                                                                                                 | 54 |

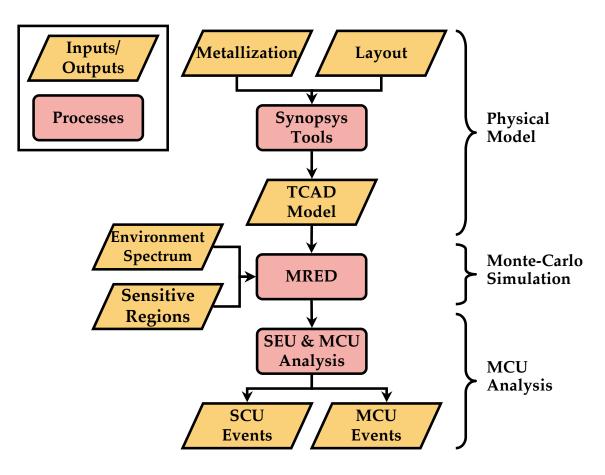

| 25. | MCU modeling methodology. This methodology uses the Synop-<br>sys TCAD tools to create a physical model. MRED simulates energy<br>transport through the structure and the results are analyzed to deter-<br>mine MCU events.                                                                                                                                                                                                              | 58 |

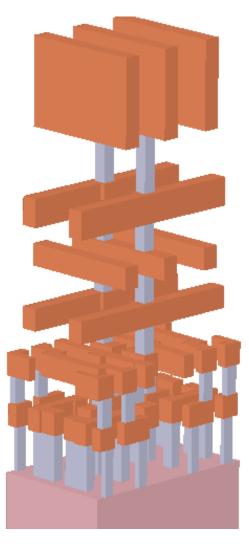

| 26. | Physical model of a single SRAM cell created using Synopsys TCAD tools. Six layers of copper lines, tungsten vias, and silicon bulk are visible. Layout and BEOL characteristics of the process are used to create the structure. This structure is used by MRED to simulate radiation transport                                                                                                                                          | 60 |

|     | radiation transport.                                                                                                                                                                                                                                                                                                                                                                                                                      | 60 |

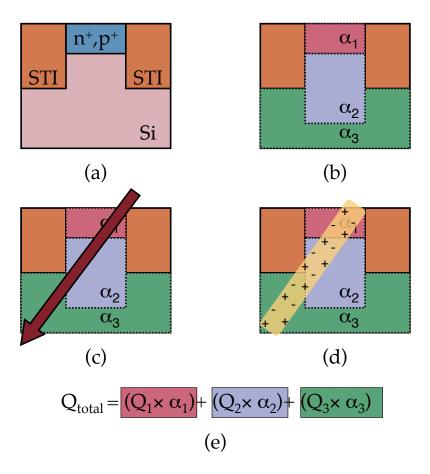

| 27. | (a) The sensitive volume description begins with the junction of a sensitive node. (b) A set of sensitive volumes is defined for the sensitive region. Associated with each sensitive volume is a charge collection efficiency $\alpha$ . (c) The path of a charged particle passing through the sensitive volumes is illustrated. (d) Charge is generated along the path and $Q_{total}$ is calculated using Eq. 10. (e) The explicit equation for $Q_{total}$ in this illustration is shown.                                    | 63 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

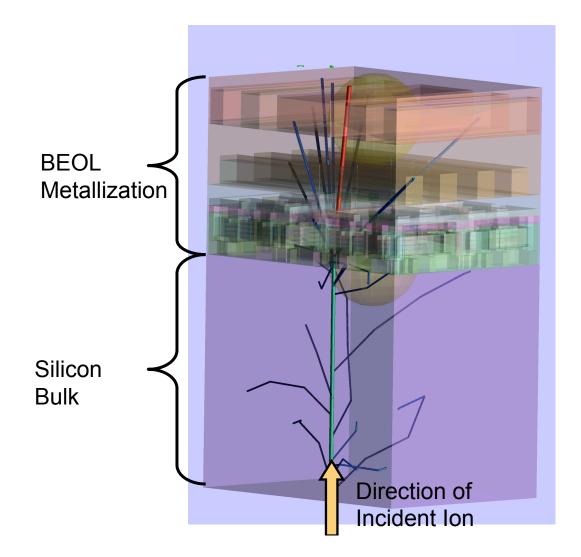

| 28. | Example MRED generated event. The BEOL material is shown a the top of the figure. The incident heavy ion enters through the bottom of the bulk silicon and induces a nuclear reaction near the surface of the silicon. The trajectories of the incident ion and secondary products are detailed by the colored lines. Courtesy of Marcus Mendenhall                                                                                                                                                                               | 65 |

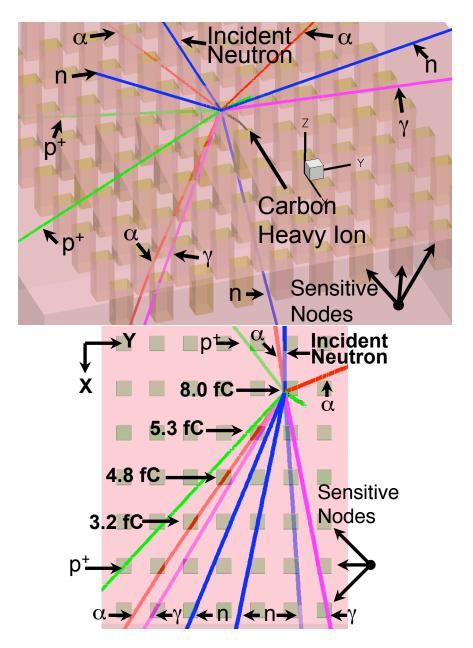

| 29. | A TCAD representation of an MRED-generated nuclear event. Only<br>the bulk silicon is shown for clarity. The shaded volumes represent<br>the sensitive nodes of the memory device. The incident neutron en-<br>ters and induces a nuclear event. The shower of secondary products<br>includes alpha particles, protons, neutrons, gamma rays, and a car-<br>bon heavy ion (n+Si $\rightarrow$ C+3n+2p+3 $\alpha$ ). In the top-down view on bot-<br>tom, generated charge for sensitive nodes with more than 1 fC are<br>labeled. | 67 |

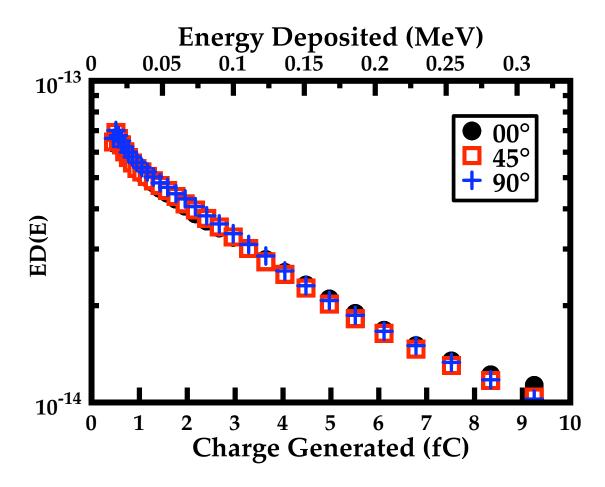

| 30. | The MRED simulated upset rate versus charge generated for the TI 90 nm SRAM shows little dependence on the device orientation for the ICE House neutron spectrum.                                                                                                                                                                                                                                                                                                                                                                 | 69 |

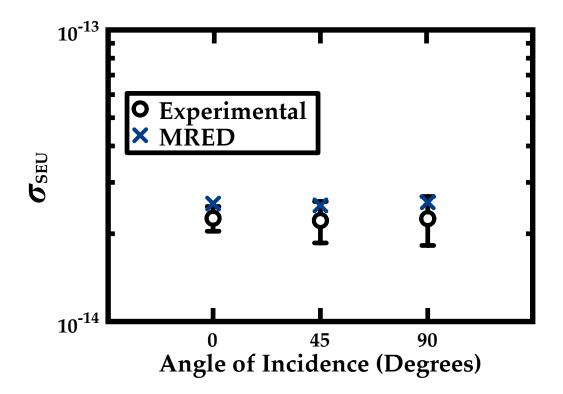

| 31. | The $\sigma_{SEU}(E)$ simulated by MRED is compared with experimental data.<br>MRED simulation is in good agreement with the experimental data.<br>Error bars represent the counting statistics for simulation and exper-<br>imental results and they are only shown when visible.                                                                                                                                                                                                                                                | 70 |

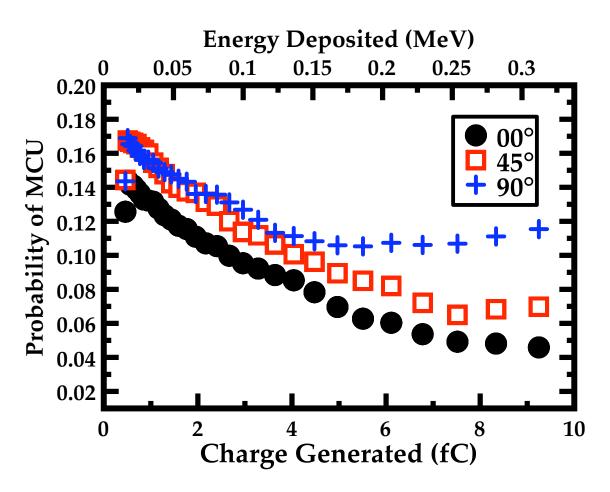

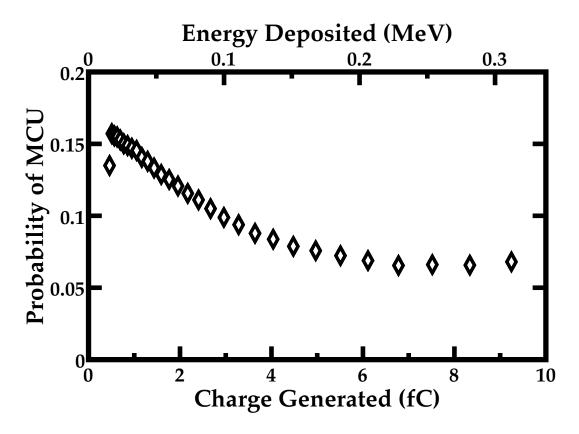

| 32. | The MRED simulated probability of MCU versus charge generated<br>shows a dependence on the orientation of the device. The probability<br>increases at grazing angles because the secondary products tend to<br>scatter in the forward direction                                                                                                                                                                                                                                                                                   | 72 |

| 33. | The probability of MCU simulated by MRED is compared with experimental data. MRED simulation is in good agreement except at the largest grazing angles where the board obstructs the beam path.                                                                                                                                                                                                                                                                                                                                   | 73 |

| 34. | The MRED simulated error rate versus generated charge is shown for single–cell to four–cell upsets for ground level operation. An upset rate of approximately 400 FIT/Mbit is predicted for the cell at ground level.                                                                                                                                                                                                                                                                                                             | 75 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 35. | The MRED simulated probability of MCU versus generated charge<br>is shown for ground level operation. A probability of approximately<br>10% is predicted for the cell at ground level.                                                                                     | 76 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 36. | The calibrated MRED response (indicated by the Xs) is compared with experimental data (indicated by the circles).                                                                                                                                                          | 77 |

| 37. | The heavy ion flux spectrum for the GEO environment for ions with atomic numbers 1-92. The spectrum is taken from the CREME96 TRANS algorithm through 100 mils of aluminum                                                                                                 | 78 |

| 38. | The probability of MCU events for 1 and 2 column events versus the number of affected rows. Approximately 90% of events are SCU, $1 \times 1$ , events. Small dimension events dominate the MCU response. Events affecting nine rows account for one in every $10^5$ event | 79 |

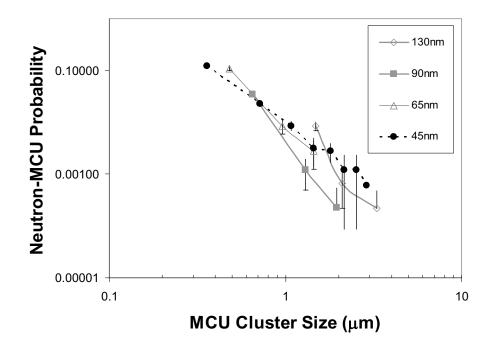

| 39. | The probability of MCU is shown for four generations of Intel's CMOS process. The MCU cluster size represents the maximum distance in an MCU cluster. The trends in probability for all generations exhibit a similar dependence on the size of the cluster.               | 82 |

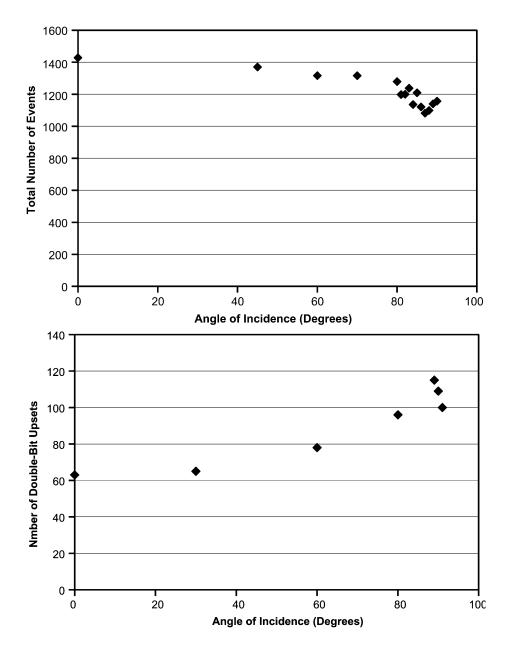

| 40. | Comparison of total SEUs (top) and total double–bit upsets (bottom) for a 16 Mbit NEC DRAM from 198 MeV protons. The device was rotated to a grazing angle where the number of double–bit upsets doubled.                                                                  | 84 |

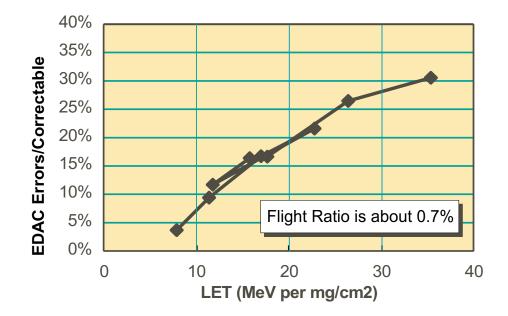

| 41. | Ratio of uncorrectable EDAC errors to all bit errors versus LET for<br>the Cassini solid–state recorder. Poor bit–interleaving was identified<br>for the high number of uncorrectable errors.                                                                              | 86 |

| 42. | Ne ions incident at $0^{\circ}$                                                                                                                                                                                                                                            | 91 |

| 43. | Ne ions incident at $45^{\circ}$                                                                                                                                                                                                                                           | 92 |

| 44. | Ne ions incident at $79^{\circ}$                                                                                                                                                                                                                                           | 93 |

| 45. | Ar ions incident at $0^{\circ}$                                                                                                                                                                                                                                            | 94 |

| 46. | Ar ions incident at $45^{\circ}$                                                                                                                                                                                                                                           | 95 |

| 47. | Ar ions incident at $79^{\circ}$                                                                                                                                                                                                                                           | 96 |

| 48. | Kr ions incident at $0^{\circ}$                                                                                                                                                                                                                                            | 97 |

| 49. | Kr ions incident at $45^{\circ}$                                                                                                                                                                                                                                           | 98 |

| 50. | Kr ions incident at $79^{\circ}$                                                                                                                                                                                                                                           | 99 |

#### CHAPTER I

#### INTRODUCTION

This invention relates to miniature electronic circuits, and more particularly to unique integrated electronic circuits fabricated from semiconductor material.

—Jack Kilby, U. S. Patent 3,138,743

#### The Integrated Circuit

Jack Kilby of Texas Instruments was granted the first patent of the integrated circuit (IC) in 1964 [1,2]. In 1967 a patent for the complementary metal oxide semiconductor (CMOS) system was issued to Frank Wanlass of Fairchild Semiconductor Research and Development [3]. Since then, improvements in performance and packing density for each new generation of IC have been primarily achieved by shrinking transistor sizes. State-of-the-art microprocessors boast nearly a billion transistors. Such transistor densities make the metal-oxide-semiconductor field effect transistor (MOSFET) easily the most manufactured item in history.

The International Technology Roadmap for Semiconductors (ITRS) reports 65 nm as the 2007 feature size – as defined by  $\frac{1}{2}$  the pitch of metal [4]. Scaling to such small feature sizes has not been easy or cheap. After development and design cost, IC Insights estimates that the required sales for positive return on investment (ROI) for a 65 nm process to be \$8.3 billion. Only Intel, Samsung,

Texas Instruments, STMicroelectronics, and Toshiba had 2006 sales greater than that number [5].

#### Radiation Effects

The interactions of charged particles with semiconductor devices may lead to logic errors in digital ICs. Charged particles are the source of single-event effects (SEEs) in integrated circuits. In 1962 Wallmark and Marcus proposed an absolute minimum size and maximum packing density for semiconductor devices [6]. Cosmic ray interaction at ground level was identified as one limitation to the minimum device size. Other reasons included heat dissipation and dopant fluctuations. It is interesting to note that the authors concluded 10  $\mu$ m to be the limiting feature size.

Binder *et al.* first reported in 1975 on single event phenomenon for space systems [7]. In 1979 May and Wood identified SEEs in commercial parts due to alpha particles from radioactive decay in packaging materials [8]. In that same year Ziegler and Lanford examined the impact of terrestrial radiation from galactic cosmic rays on ground based systems [9].

Development of the modern IC to increase functionality and performance has forced higher device densities and smaller devices. Reduction of power consumption has also become a major concern as device densities increase and has forced operating voltages to scale down as well. The trends in density and operating voltage have increased the susceptibility of ICs to radiation induced soft errors in state-of-the-art electronics [10,11]. Soft error rate (SER) refers to the rate at which data errors occur. SER not only depends on the device susceptibility to ionizing radiation, but also the environment in which the device is expected to operate. In general, device scaling has created competing trends for some single-event effects. For bit errors, the single-bit SER has generally decreased in highly-scaled technologies, but the drastic increase in bit density has kept system level SER generally constant across generation. Fig. 1 shows the neutron induced SER/bit for Intel's 180 nm–45 nm technology nodes [10]. Each successive generation of CMOS technology shows a decrease in single bit SER.

Figure 1: The neutron–induced bit soft error rate for Intel's 180 nm–45 nm technology nodes decreases with each new generation. The probability of MCU increases with each new generation because higher device densities places sensitive nodes closer together.

#### The Multiple Cell Upset

When a charged particle travels through material, it loses energy through their interactions with matter. In semiconductor materials, charge is generated from this energy loss along the path of the incident particle. When sufficient charge is collected on a circuit node to change its state, this leads to a corruption of the data called a single event upset (SEU). A single-cell upset (SCU) occurs when these interactions change the logic or memory state of one bit. Relative to the size of the charge track produced by the incident particles, the geometries of stateof-the-art integrated circuits are small. Interaction with multiple bits is possible for some particle trajectories and paths. Multiple-cell upset<sup>1</sup> (MCU) results when SCU occurs in multiple cells from a single ion. MCUs are important because may be more difficult to correct using error correction [20].

With smaller semiconductor devices, the packing density increases. Higher packing densities increase the probability that an inoizing particle will induce an MCU event. Fig. 1 shows the probability of MCU for Intel processes. The probability increases from approximately 1% in 130 nm feature sizes to 15% in their state–of–the–art 45 nm process.

Fig. 2 is an example of an MCU event from a 63 MeV proton represented in a technology computer aided design (TCAD) structure. Only this silicon material is shown as the overlayers have been omitted. The incident proton induces a

<sup>&</sup>lt;sup>1</sup>The SCU and MCU effects are termed single-bit upset (SBU) and multiple-bit upset (MBU) respectively in [12–18]. This semantic change reflects the JEDEC (Joint Electron Devices Engineering Council) standard where the bit upset nomenclature is reserved for logical bit upset in the context of data words in a memory architecture [19].

nuclear reaction near silicon surface of the memory array. The shaded boxes represent sensitive regions of the silicon, each corresponding to one bit in a memory array. The incident proton enters at a grazing angle and interacts with the silicon to cause a nuclear event. The trajectories of the incident proton and secondary particles are represented by the colored lines. A 14 MeV oxygen ion is emitted from the reaction that traverses six, darker shaded, sensitive volumes. The other reaction products include a proton, gamma rays, and alpha particles. This is an example of a six-bit upset if the deposited energy is sufficient to upset the cells. The oxygen secondary ion from the nuclear reaction is responsible for the MCU event.

The probability of a given event producing an MCU increases as the size of semiconductor devices scale smaller because the distance between cells is reduced [12, 21, 22]. Fig. 1 shows the increasing probability of MCU with successively new generations of Intel's CMOS technologies because of higher device densities. MCUs from broad-beam proton and neutron irradiations have been shown to depend on the orientation of the device relative to the incident beam [12, 14, 15, 23]. Nucleons incident at large angles of incidence tend to traverse more cells and MCU increases at these orientations.

Testing of electronic devices must account for these dependences to predict the radiation response accurately. Testing at a single device orientation may not observe the worst case MCU response. Previously it was shown that MCU cross section increases an order of magnitude for 63 MeV protons at grazing angles compared to normal incidence [12]. The cross section increases because the ionizing secondary products produced by these protons have trajectories similar to

Figure 2: A TCAD representation of an MRED generated nuclear event for a 63 MeV proton incident at a grazing angle in silicon with the sensitive volumes shown by the shaded boxes. The overlayers have been omitted. The secondary products from the reaction are a 14 MeV oxygen ion, a proton, gamma rays, and alpha particles. The oxygen heavy ion transverses six sensitive volumes of SRAM cells.

the incident proton. For these protons, the maximum likelihood of interacting with multiple cells is realized at the largest grazing angles. That is, the radiation response depends on the orientation of the device relative to the trajectories of the secondary heavy ions.

#### Summary of this Work

In this work, device orientation effects on MCU are examined for neutrons and heavy ions. Accelerated testing is used to evaluate static random access memories (SRAMs) for MCU by changing the orientation of the device in the beam path. Experimental results from accelerated tests are used to characterize two technologies for MCU and they are used to calibrate an MCU model. The size, shape, and probability of MCU are shown to depend on orientation for both particle types. The worst case MCU events occur at large angles of incidence. Additionally, heavy ions also exhibit a strong dependence on the ion's trajectory with respect to the SRAM layout for the size and shape of MCU events.

This work analyzes the MCU response for neutrons and heavy ions using the Monte-Carlo Radiative Energy Deposition (MRED) code [24, 25]. The transport of radiation through matter is simulated using MRED. MRED is a Monte–Carlo transport code based on the Geant4 libraries [26]. These libraries model the transport of radiation through matter. The Geant4 libraries contain models for ionization and nuclear processes. MRED has been used to examine: the role of heavy ion induced nuclear reactions on SER [27, 28], the role of metallization near semiconductor devices on heavy ion induced nuclear reactions [29], on–orbit SER predictions [30, 31], and the effects of nucleon induced radiation events [13, 32].

The experimental results are used to calibrate a model for the devices in this work. The radiation transport model is used to analyze MCU for real environments and compared to the accelerated response.

Chapter II discusses the background and trends of MCU in state-of-the-art microelectronics. Chapter III discusses MCU analysis of radiation events. In Chapter IV neutron–induced MCU effects are reported and the heavy ion effects are reported in Chapter V. Chapter VI details the Monte-Carlo modeling and discusses the MCU response for real environments. Finally, a discussion of the implications of MCU is found in Chapter VII.

#### CHAPTER II

#### BACKGROUND

This chapter gives a broad overview of the source and mechanisms of SEEs and MCU. The sources, types, and mechanisms of MCU are discussed. The upset mechanisms important to this work are reviewed. The origins of MCU are discussed. The development and trends in MCU are discussed for nucleon and heavy ion induced effects.

#### Single Event Effects (SEEs)

This section outlines the basics of SEEs important for MCU. The sources, types, and mechanisms are discussed. Finally, SRAM upset is discussed because it is the device type considered in this work.

#### Sources of SEEs

SEEs are the result of ionizing radiation interacting with semiconductor circuit elements. The severity and frequency of these interactions on circuit operation depends strongly on the environment in which the system will operate. Particles found in the space environment are dominated by protons and heavy ions. Galactic cosmic rays (GCR), the solar activity of the sun, and particles trapped in the Earth's magnetic fields are the sources of those particles. The distributions of energies and ion species depend on the specific orbit. Detailed discussions of the space environment can be found in [33, 34].

Protons and heavy ions are of little concern for terrestrial systems because these particles are shielded by the Earth's atmosphere. Cosmic ray interactions in the Earth's atmosphere through the strong force create cascades of secondary particles that move towards ground level. These secondary products penetrate to ground level leading to a terrestrial environment of non-ionizing neutrons that indirectly ionize through nuclear interactions. Radioactive decay by materials in and around devices are another source of SEEs for ground based systems. A discussion of the terrestrial environment can be found in [35].

#### Types of SEEs

SEEs are broadly grouped into two categories: destructive and non-destructive. Destructive SEEs result in permanent damage that impinges on the proper operation of a circuit element. While these effects leave circuit elements inoperable, their impact on circuit operation varies and depends on the role of the specific element in the circuit operation. Non-destructive SEEs occur when radiation events disrupt circuit operation. These effects do not cause permanent damage, but they can lead to interruption of normal circuit operation and, in some cases, data corruption. These errors can be transient pulses that appear as current pulses on circuit nodes that may propagate through the circuit or they can be static errors that change the state of a static circuit such as a latch [36]. This work focuses on non-destructive static SEU in SRAMs.

#### SEE Mechanisms

Radiation interactions in matter fall into two categories: electromagnetic interactions and nuclear interactions. Electromagnetic processes are conventionally considered only for heavy ions while nuclear processes are considered for nucleons though heavy ion nuclear interaction is possible (note, proton ionization is consider for sensitive devices such as imagers). What follows is an overview of the major interactions of concern for electronics. A more detailed discussion of these processes can be found in [37, 38].

#### Heavy ions

From the perspective of radiation effects on ICs, heavy ions interact primarily through electromagnetic processes. In some cases, heavy ions have been shown to interact through nuclear collisions and contribute to SEEs as well [28,29,39]. When a charged particle passes through matter, its energy is transferred to the material. This process continues until the ion loses all its kinetic energy and comes to rest. Linear energy transfer (LET) is the average amount of energy lost per unit length and is usually normalized to the density of the material. The LET of a particle is dependent on the species of ion, energy of the ion, and target material. The average LET of an ion in a material is available from codes like SRIM [40].

Energy loss in a semiconductor material creates electron-hole pairs (EHPs). In silicon, 3.6 eV of energy loss produces, on average, one EHP [41]. For example, an ion with an LET of 9.7 MeV–cm<sup>2</sup>/mg creates a charge density of 10 fC/ $\mu$ m. The EHPs that are created are subject to normal semiconductor transport mechanisms. From a circuit perspective, charge collection on a node appears as a current pulse

on the node. The shape of the resulting current pulse depends on the location and amount of charge generated relative to the contact where it is collected. The injection of charge leads to SEEs in integrated circuits.

#### <u>Nucleons</u>

Nucleon-induced effects differ from heavy ions because their electromagnetic interactions produce negligible or no EHPs. Rather, these particles interact mainly through nuclear interactions. Protons and neutrons can overcome the Coulomb barrier and interact with an atom's nucleus through the strong force when they are transported through semiconductor materials. Breakup of the nucleus produces secondary heavy ions and other products that in turn generate charge through electromagnetic forces. The charge produced by secondary products is the source of nucleon-induced SEEs in integrated circuits.

#### SEE – SRAM upset

In this work, upsets in SRAM devices are considered. Fig. 3a shows a circuit schematic diagram of a conventional four transistor (4T) SRAM circuit. The SRAM circuit is a cross coupled pair of inverters with an active feedback network. The logic diagram is shown in Fig. 3b where the two connected inverters store the data. When an ionizing particle strikes the SRAM cell, the collected charge appears as a current pulse on the circuit nodes. Whether or not the cell will upset depends on which node is struck. Typically, strikes to the diffusions of the OFF state n–MOSFET or p–MOSFET transistors will lead to upsets. A strike to the drain of the n–MOSFET is termed an "n-hit" and a strike to the p–MOSFET is termed a "p-hit". The current pulse can discharge the node and change the potential. The feedback path is shown by the arrows in Figs. 3a and 3b.

The ON state device, the p-MOSFET in the case of an n-hit or the n-MOSFET in the case of a p-hit, will attempt to restore the node voltage. At the same time the resulting voltage transient on the struck node will propagate to the other cross coupled inverter. If sufficient charge is collected and the resulting voltage transient propagates through the feedback, then the circuit will upset. The current and voltage at the struck node of the OFF n–MOSFET in Fig. 3a are illustrated in Fig. 3c. The spike in the current is the result of the initial charged particle strike to the drain of the device. The initial drop in the voltage, which appears as a single event transient (SET) at the struck node, begins to recover as the ON p-MOSFET supplies current to restore the node. The feedback of the initial strike through the other inverter eventually drives the voltage down and results in an SEU. The total collected charge, Q<sub>Coll</sub>, on the struck node is determined by integrating the current pulse. Strikes such as the one in Fig. 3c will not always result in an SEU. The size of the current peak is related to the location of the charged particle strike. The current pulse must overcome the restoring current from the ON device. The minimum charge required to induce upset is called the critical charge, Q<sub>Crit</sub>, of the circuit.

#### The Multiple Cell Upset

In this section MCU and MBU effects are described. These effects are grouped into heavy ion and nucleon effects because the physical mechanisms for each are different.

Figure 3: (a) A circuit schematic diagram of an SRAM formed by two crosscoupled inverters. The ON and OFF state devices are labeled for one possible state of the SRAM. The feedback path of a strike to the drain of the OFF n-MOSFET device is shown by the dotted line. (b) The logic diagram of the circuit shows the feedback path of a transient strike indicated by the dotted line. (c) The current and voltage transients at the node of the OFF n–MOSFET are illustrated. The initial current pulse drops the voltage at the node. The ON p–MOSFET attempts to restore the state of the node. The feedback of the initial strike and the additional collected charge eventually result in an SEU.

Many of the first uses of accelerated heavy ion broad beam SEU testing also reported MCU and MBU events. Criswell *et al.* reported the first observation of MCU in 1984 while using heavy ions for SEE testing [42]. The device under test was a 256–bit bipolar SRAM. The experimental data showed as many as 16 cells upsetting for 600 MeV/u Fe heavy ions. Bisgrove *et al.* calculated the first MCU cross sections for heavy ions in Intel 64 kbit 1.5  $\mu$ m DRAMs from heavy ion and proton testing [43]. Blake *et al.* reported on-orbit observations of 1.25  $\mu$ m SRAMs using bitmaps to show the physical locations of MBUs which accounted for 19% of all events [44]. SEE testing since that paper has often noted MCU and MBU. MCU/MBU evaluation are often part of the SEE testing for new technologies.

MCU and MBU have been noted in on–orbit data by several authors [44–48]. Error detection and correction (EDAC) is commonly used to correct MBU events for memory arrays [48–52]. MBU poses reliability concerns for EDAC circuitry because data corruption of multiple bits is more difficult to protect against. Bit– interleaving, where bits in the same data word are separated by distance in the memory array, is one way to increase the effectiveness of EDAC. Lack of aggressive bit–interleaving has been identified for unexpectedly high data corruption of on–orbit memories because of MCU events [48].

Alpha emission and thermal neutrons are the primary concerns for MCU and MBU in ground based systems [53–60]. Cache and memory are primarily a concern for large servers [20]. In those systems, soft errors induced by alpha particles and neutrons can induce MCU. EDAC are used extensively for large server memory arrays with bit interleaving schemes [20, 58].

15

#### Heavy Ion Induced MCU

The probability of double bit upset had been shown to depend on the radial charge density of the charge generated by ion strikes [61]. It was shown that heavy ions with larger radial tracks could more easily make direct hits to multiple memory cells. This was shown by characterizing MBU with respect to device spacing.

The right parallelepiped (RPP) sensitive volume was proposed by Pickel and Blandford [62]. This upset model for SEU assumed a fixed RPP volume in which generated charge would lead to upset. The model assumes a fixed Q<sub>Crit</sub> and uses an average of all possible cord lengths for the RPP volume to determine upset. This model was updated by Petersen *et al.* [63]. An extension of this model to double bit upset was developed by Edmonds [64] then extended by Smith and Shoga [65]. Following from the RPP model, the double bit model assumes a common path length through multiple sensitive volumes due to a single heavy ion track corrected for angle. This model has its limits, however. Because of shrinking dimensions, the simple geometric approximation of the RPP becomes inadequate. Other charge collection mechanisms such as charge sharing and bipolar amplification can play roles in SEU for highly scaled technologies [66,67].

Increased MCU has been attributed to diffused charge collection in SRAMs [68]. Device simulation was used to show the role of diffusion charge in MCU as early as 1.25  $\mu$ m technologies [69–71]. It was shown that diffusive charge collection for heavy ions incident on pn-junctions was greater than for incident heavy ions that do not strike junctions. The general observation was that ions incident on junctions produced more charge collection on that node and reduced the amount of

charge that could diffuse to nearby nodes, thus reducing the probability of MCU. Bipolar charge collection was identified as another MCU mechanism [72].

Heavy ion induced MCUs can be separated into two types [73]. Type I errors are due to a heavy ion passing through multiple sensitive volumes and inducing multiple upsets. Type II MCU is due to diffusive charge and other charge collection mechanisms. The differences between the two can be seen by comparing MCUs from normally incident ions with MCUs from ions incident at oblique angles. Other causes of MBU have been attributed to heavy ion interactions with control circuitry that induce word line upset [74].

Three–dimensional mixed mode device simulation by Dodd *et al.* mapped out regions of MCU sensitivity between two nodes for Type II events [75]. Diffusion from heavy ion ionization was identified as the upset mechanism. Relative to bulk processes, epitaxial structures showed a reduced diffusion component of charge collection making them more desirable for mitigating MCU. Laser testing has also been used to map MCU sensitivities [76].

#### Nucleon Induced MCU

O'Gorman *et al.* measured SEU at ground level from cosmic rays [53, 77]. Dynamic Random Access Memory (DRAM) SER was tested at various altitudes above and below sea level and showed an order of magnitude increase in SER at an altitude of 3.1 km compared to sea level. That study found that not only SEU but also MBU at ground level is possible. Higher altitudes exhibited increased SER. While neutron environments have shown a decrease in the SER for single– cell upsets, MCU has increased in highly scaled devices [10,11,22]. Seifert *et al.* showed increased MCUs due to decreased node spacing [10] as did Baumann [11]. Device scaling reduces the charge collection sensitive volume, making upset less likely. Scaling also reduces the charge required to upset, making more likely. These competing effects have held the SEU rate relatively constant for newer and smaller CMOS processes. The MCU response is dominated by device scaling, however, and the probability of MCU has increased for smaller dimensions.

The CRRES MEP satellite noted on–orbit MCU at a high rate in [45]. The frequency of these events inside proton belts dominated the SEE and MBU responses. Reed *et al.* also observed increased proton–induced MCU at grazing angles in [78]. CUPID calculations agreed with the angular dependence observed for proton irradiation. Buchner *et al.* showed MCU events to double at large grazing angles for 63 MeV and 198 MeV protons [79]. Testing confirmed that the SEE response due to proton irradiation exhibits an angular dependence in more highly scaled SRAMs [80]. CUPID simulations in [79] and GEANT4 in [80] suggested that angular dependencies would be more pronounced for lower proton energies because of the direction of spallation products with respect to the incident proton direction. It was shown by both studies that MCU should be expected to increase with device downscaling because of reduced device dimensions.

MRED simulations of 63 MeV and 200 MeV protons on SRAMs exhibit higher MCU probabilities at grazing angles [12,13]. Fig. 4 shows the simulated probability of MCU for the IBM 8RF 130 nm bulk CMOS process from 63 MeV protons. Four angles of irradiation are shown from normal incidence to oblique grazing angles. The energy deposition profiles are shown for generated charge in the sensitive volume of the SRAM cells. Evaluating the curve at the  $Q_{Crit}$  of the circuit yields the MCU probability. Circuit simulation suggests  $Q_{Crit}$  to be approximately 10 fC. Evaluating at this value, the highest probabilities at the largest grazing angles are approximately 5%.

Figure 4: The probability of MCU from 63 MeV protons increases with the angle of proton incidence.

#### Summary

The space radiation environment important to SEEs in ICs is composed of heavy ions and protons. GCR and solar activity if the sun are the sources of those particles. GCR interaction in the atmosphere produces showers of neutrons that penetrate to ground level. The terrestrial radiation environment is composed primarily of those neutrons and alphas.

In this work, SEEs on SRAMs are examined. The upset mechanism for SRAM cells is due to charge collection on the circuit nodes of the SRAM. The inherent feedback network of SRAM cells attempts to balance any perturbation. The minimum collected charge to upset a cell, Q<sub>Crit</sub>, is an important characteristic in modeling SEEs in SRAM cells.

As the characteristic feature sizes are reduced in state–of–the–art semiconductor processes, MCU continues to increase in probability for SRAM arrays [10, 11]. The close proximity of cells is the driving force behind this increase because of the increased coupling of individual cells' charge collection during ionizing radiation events.

MCU has been observed in both the space and terrestrial radiation environments [45,77]. Heavy ions and nucleons have different upset mechanisms: direct heavy ion ionization and ionization by secondary products from nuclear reactions induced by nucleons. Evidence for orientation dependences due to these particles in highly scaled technologies exists. Particles incident at large angles of incidence with respect to the surface of semiconductor devices exhibit higher probabilities of MCU.

In the chapters that follow, evidence of the dependence of MCU on device orientation with respect to incident heavy ions and neutrons is presented. Accelerated testing is used to examine the orientation effects and modeling of these effects is used to examine real environments.

20

#### CHAPTER III

#### MULTIPLE CELL UPSET ANALYSIS

In this chapter the methods used in this work for the analysis of SEU and MCU events are presented. The methods presented in this chapter will be used to analyze the MCU radiation response. The methods used to analyze the SEU response are presented first. The SEU response is separated into the analysis of SCU and MCU events. MCU analysis in this work characterizes MCU events by their multiplicity and the area of affected bits.

#### Single Event Upset

Ground based accelerated testing using particle accelerators is used extensively to characterize the radiation response of ICs [81]. The SEU response is used by convention to calculate and predict the SER performance of the device. Error rate predictions in a specific environment are made based on accelerated SEU testing. The primary purpose of SEU testing is to evaluate the SEU cross section versus energy deposition for use in calculating SER performance. The SEU cross section,  $\sigma_{SEU}$ , is the uncorrelated bit upset cross section for all bit upsets from SCU and MCU events. It is defined as

$$\sigma_{\text{SEU}} = \sum_{i=1}^{\infty} \frac{i \times \text{Event}_{i-\text{bit}}}{\Phi} = \frac{1 \times \text{Event}_{1-\text{bit}} + 2 \times \text{Event}_{2-\text{bit}} + 3 \times \text{Event}_{3-\text{bit}} + \dots}{\Phi}$$

(1)

where  $\text{Event}_{i-\text{bit}}$  is the number of MCU events with *i*-bits upset, and  $\Phi$  is the fluence of incident particles.

For heavy ions, the  $\sigma_{SEU}$  is calculated for each ion at a single accelerated energy. Since it is impossible to test every ion at every energy for a space environment, ions are selected in SEU testing such that they cover a range of heavy ion LETs. Note, in this work no cross sections are reported as effective cross sections (*i.e.*, LET is not converted to effective LET and fluence is not converted to effective fluence). All fluences in this are reported as measured in the plane perpendicular to the beam line. In recent highly-scaled technologies, the traditional RPP model assumptions are no longer valid [30]. Note also, all SRAM cross sections in this work are normalized to the total number of bits in the device under test unless stated otherwise.

#### Multiple Cell Upset

The SEUs in an SRAM array can be divided into SCU and MCU events. An SCU event is defined as an isolated single cell upset with no other cell upsets nearby. An MCU event is defined in this work as two or more physically adjacent bits failing in the same exposure. Bits are considered to be physically adjacent for bit upsets in adjacent rows, adjacent columns, or both rows and columns (*i.e.*, diagonal bits). A cross section is defined for both types of events. The single–cell upset cross section,  $\sigma_{SCU}$ , is the cross section for events affecting only one cell and is given by

$$\sigma_{\rm SCU} = \frac{\rm Event_{1-bit}}{\Phi} \tag{2}$$

where Event<sub>1-bit</sub> is the number of SCUs and  $\Phi$  is the fluence of incident particles.

Similarly, MCU events are characterized by events for a specific number of affected bits in the MCU cluster. Each cluster multiplicity has a distinct cross section. The cross section for an MCU event with *i* affected bits,  $\sigma_{i-\text{bits}}$ , is

$$\sigma_{i-\text{bits}} = \frac{\text{Event}_{i-\text{bit}}}{\Phi} \tag{3}$$

where *i* is the number of affected bits in the MCU cluster,  $Event_{i-bit}$  is the number of events with *i* bits in the MCU cluster, and  $\Phi$  is the fluence of incident particles. By this definition events are only counted once regardless of the number of events and  $\sigma_{i-bits}$  represents the cross section for an event of i–bit size.

The total cross section for all MCU events,  $\sigma_{MCU}$ , is the event cross section for clusters of 2–bit upsets and larger, with each MCU event counting as one event, independent of the number of bits upset.  $\sigma_{MCU}$  is given by

$$\sigma_{\rm MCU} = \sum_{i=2}^{\infty} \frac{\text{Event}_{i-\text{bit}}}{\Phi} = \frac{\text{Event}_{2-\text{bit}} + \text{Event}_{3-\text{bit}} + \text{Event}_{4-\text{bit}} + \dots}{\Phi}$$

(4)

where the sum of  $\sigma_{SCU}$  and  $\sigma_{MCU}$  represents the total number of events. This deweighting of MCU event multiplicities allows for equal comparison of SCU and MCU events such that an explicit definition of MCU probability is defined.

#### Probability of MCU

The probability of MCU is an important characteristic of the MCU radiation response because of the role it plays in memory architecture design [10]. Error detection and correction (EDAC) in memory arrays are susceptible to multiple upsets. The probability of MCU reflects the susceptibility of a technology to MCU events that may pose EDAC reliability concerns for the device. The probability of MCU is the fraction of events that result in an MCU. The probability can be written as  $\infty$

Probability Of MCU =

$$\frac{\sum_{i=2}^{\infty} \text{Event}_{i-\text{bit}}}{\sum_{i=1}^{\infty} \text{Event}_{i-\text{bit}}}$$

(5)

where the summation in the numerator counts MCU events and the summation in the denominator counts all events. Note, regardless of the multiplicity of the event, each event is counted only once and are not weighted.

#### MCU Dimension Analysis

By convention, the size of MCU events is characterized by the number of affected bit (*e.g.*, 2–bit, 3–bit, 4–bit, *etc...*). However, this does not detail the shape of the MCU event or the spatial distribution of the upsets. For the purpose of the present discussion, a better metric of size is the affected area in dimensions of rows and columns. In this manner, the dimension of an MCU event can be written as

$$MCU Dimension = N_{row} \times N_{col}$$

(6)

where  $N_{row}$  is the number of affected rows and  $N_{col}$  is the number of affected columns. MCU dimension is illustrated in Fig. 5. The example illustrates a 3 × 3 bit array where the red blocks indicate bit upsets. Fig. 5a is an example of a SCU

event. All  $1 \times 1$  events are SCUs. While Fig. 5b and Fig. 5c are both examples of  $2 \times 2$  events, their bit multiplicities are 2-bit and 4-bit, respectively. They are considered to have the same dimension. Note, in this work nearby cell upsets that are not physically adjacent are not considered to be part of the same cluster.

Figure 5: (a) MCU dimension is illustrated for SCU events. All SCU events are  $1 \times 1$  events. (b) and (c) MCU events with dimension  $2 \times 2$  are illustrated for two different event types. While their dimensions are the same, (b) is a 2-bit event and (c) is a 4-bit event. (d) A  $3 \times 2$  3-bit upset is illustrated

## Summary

In this chapter, the methods for quantifying MCU have been identified. SEU measurements are conventionally used to characterize the SEE response of memory arrays. All SEUs are characterized as SCU or MCU events. MCU events are characterized by the bit multiplicities of MCU clusters and the dimension of the MCU event. The MCU probability is an important metric for a technology.

### CHAPTER IV

#### NEUTRON MCU RADIATION RESPONSE

In this chapter orientation effects from accelerated neutron irradiations are presented. The experimental detail and results are presented and then the MCU response is discussed. Neutrons incident at grazing angles (*i.e.*, parallel to the device surface) double the number of MCU events compared to normally incident neutrons. Additionally, the neutrons incident at grazing angles produce MCU events with the largest multiplicities (*i.e.*, number of affected bits).

#### Experimental

The device under test was a high performance 6–transistor (6T) SRAM from a Texas Instruments (TI) 90 nm bulk CMOS process that operated at 1.2 V. Neutron irradiations of the SRAM were carried out at Los Alamos National Laboratory's (LANL) Weapons Neutron Research (WNR) facility using the ICE House neutron beam line. The energy distribution of the WNR neutron beam closely resembles the shape of the atmospheric neutron energy distribution at sea level, though the flux is scaled 10<sup>6</sup> times greater. Fig. 6 shows both the ground–level neutron flux scaled by a factor of 10<sup>6</sup> and the ICE House neutron beam flux at WNR [82]. The ICE House beam closely tracks the ground–level flux out to approximately 600 MeV and then rapidly falls off for higher energies.

Neutron irradiations were performed by placing the device in the ICE house beam line. Irradiations were performed at  $0^{\circ}$ ,  $45^{\circ}$ , and  $90^{\circ}$  angles of incidence to

Figure 6: Ground–level neutron flux scaled by a factor of 10<sup>6</sup> and the ICE House neutron flux at WNR. The ICE House beam closely tracks the ground–level flux out to approximately 600 MeV and then rapidly falls off for higher energies [82].

the device surface. The device orientation with respect to the incident neutrons is shown in Fig. 7. The arrow indicates the angle of incident neutrons with respect to the surface of the die. The neutron response was measured by rotating about one axis of the device. Neutrons incident normal to the device surface correspond to  $0^{\circ}$ , while 90° neutrons arrive at a grazing angle of incidence. At 90° the test board was turned into the beam so the incident neutrons were not directly incident to the surface of the die. Rather, they are incident on the edge of the test board. Because neutrons only interact through nuclear forces, the flux and energy distribution of the beam remains relatively unchanged at the active device.

Figure 7: The device orientation is illustrated for neutrons incident on the device. The arrow indicates the direction of incidence as measured from normally incident 0° neutrons. At the largest grazing angle, 90°, the test board is rotated so that neutrons are not directly incident on the device surface. Rather, they are incident on the edge of the test board.

The memory was periodically read during irradiation to record bit errors. The flux of incident neutrons was monitored using a fission ionization detector [83]. Error data were time stamped so that SCU and MCU events could be identified.

Single Event Upset Response

Fig. 8 shows  $\sigma_{SEU}$  for the three angles of neutron irradiation using Eq. 1. The experimental  $\sigma_{SEU}$  varies little with angle of incidence for the three orientations. The error bars represent counting statistics and the error associated with the beam fluence.

Figure 8: The experimental SEU cross section  $\sigma_{\text{SEU}}$  is plotted for the three different rotation angles. The SEU response varies little with the orientation of the device. The error bars represent the counting statistics and the error associated with the beam fluence.

## Multiple Cell Upset Response

In this experiment, MCU is defined as two or more physically adjacent bits failing within the same memory read. Each occurrence meeting this criterion is counted as one MCU event. Fig. 9 shows the cross section for events that induce upsets in two or more adjacent cells and is calculated using Eq. 3. A value with no upset rate means no upset of that multiplicity was observed. This figure demonstrates that the average number of bits upset per MCU event increases with the angle of incidence. The greatest number of MCUs occurs at 90°, and those events have the largest event multiplicities. At normal incidence, 89% of MCU events are two-bit events and only one event greater than three bits was recorded. The average MCU sizes for MCUs greater than two bits are listed in Table 1.

Figure 9: The  $\sigma_{i-\text{bits}}$  is shown for MCU events larger than two-bits. The greatest number of MCU events and largest sized MCU events are seen at the largest angle of incidence, 90°. The average MCU size for MCUs greater than two bits is 3.4, 5.2, and 6.4 for 0°, 45°, and 90°, respectively.

| Angle of     | Average      |  |

|--------------|--------------|--|

| Incidence    | Cluster Size |  |

| 0°           | 3.4          |  |

| $45^{\circ}$ | 5.2          |  |

| 90°          | 6.4          |  |

Table 1: Average size of MCU clusters from neutron irradiation.

### Probability of MCU

The probability of MCU represents the probability that an event will upset multiple cells. Fig. 10 shows the probability of MCU at the three angles of incidence calculated using Eq. 5. Each probability is normalized to the MCU probability when neutrons are incident normal, 0°, to the device surface. The probability increases as the angle of incidence increases. The largest probability is at the highest grazing angle, 90°. In contrast to the  $\sigma_{SEU}$ , the probability of MCU doubles for angles farthest from normal incidence. The orientation of the device with respect to the neutron beam affects the MCU probability.

### Summary

In this chapter, the impact of device orientation on the neutron–induced MCU response of a highly–scaled 90 nm technology has been examined. The accelerated neutron response was measured by rotating the device in front of the neutron beam. The SEU response is independent of the orientation, but the MCU response is not. The probability of MCU doubles at grazing angles when compared with irradiations at normal incidence. Additionally, neutrons incident at grazing angles produce the bits for MCU clusters and on average the largest events.

Figure 10: The probability of MCU is shown for the three angles of irradiation normalized to neutrons at normal incidence. The probability increases at grazing angles with the highest probability seen at the largest grazing angle, 90°. In contrast to the  $\sigma_{\text{SEU}}$ , the probability of MCU depends on the orientation of the device with respect to the beam.

These data are used in Chapter VI to analyze the MCU response in a ground– level neutron environment. In a realistic environment, neutrons are incident from all angles of incidence. MRED simulations in Ch. VI, calibrated to the data presented in this chapter that account for the orientation dependence, will be used to examine the sizes of MCU clusters.

### CHAPTER V

### HEAVY ION MCU RADIATION RESPONSE

In this chapter accelerated heavy ion irradiations are reported. The experimental detail including a description of the technology and results from heavy ion irradiations are presented. A discussion of the experimental results includes an analysis of the MCU events. MCUs exhibit a strong dependence on the axis of rotation of the device relative to the incident heavy ion beam for any LET. For higher LET ions, the probability of MCU approaches 100%; almost all events upset more than one bit. The sizes and shapes of the MCU events change for the different device orientations.

### Technology

The device under test in this chapter was fabricated in a TI 65 nm bulk CMOS process. The test die contained 4 Mbit of a density–optimized SRAM. The SRAM operated at 1.2 V. The nominal n–well bias was 0.7 V for this test die. The die was bonded directly to a test board to reduce obstruction of the heavy ion beam by the packaging of the device at oblique angles of incidence. An FPGA–based tester was used to write and read the memory between irradiations [84].

Irradiations were carried out at several angles of incidence. The board was rotated about both the x–axis and y–axis, making two distinct die orientations to the beam. The orientations of the die will be described with respect to the SRAM layout. The layout of the SRAM array results in alternating columns of n– MOSFET and p–MOSFET devices. From a macroscopic view, the chip is laid out with alternating columns of n–wells (containing p–MOSFET devices) and p–wells (containing n–MOSFET devices).

Fig. 11 illustrates the orientation. The alternating blue and red columns represent the wells of the device. Rotation about the x-axis is referred to as "along– the–wells" rotation because ions incident at this orientation move along the long length of the wells. Y-axis rotation is referred to as "against–the–wells" because ions incident at these angles are perpendicular to the well lengths. Additionally, the cell pitch plays an important role in the SEE response. For these cells, the cell pitch in the against–the–wells direction is twice the pitch of the along–the–wells direction. The trajectories of incident heavy ions are illustrated at the bottom of Fig. 11 by the arrows for both orientations.

### Experimental

Irradiations were carried out at Texas A&M University's Cyclotron Institute. Three 15 MeV/nucleon ions were used: 299 MeV <sup>20</sup>Ne (2.8 MeV-cm<sup>2</sup>/mg), 596 MeV <sup>40</sup>Ar (8.6 MeV-cm<sup>2</sup>/mg), and 1248 MeV <sup>84</sup>Kr (28.9 MeV-cm<sup>2</sup>/mg). The test board was mounted in the ion beam path and room temperature irradiations were performed at three angles: 0°, 45°, and 79°. The 79° angle was the largest angle such that the chip was not shadowed by the test setup. The die was irradiated in both orientations: along–the–wells and against–the–wells. Fig. 11 shows the board setup and axes of rotation and the trajectories of the incident heavy ions are indicated by the arrows. As the angle of incidence increases, the incident ions

Figure 11: (top) The test board was rotated about the x-axis and y-axis. The alternating blue and red columns represent the n- and p-wells of the die. The two die orientations are defined from the wells. Rotation in the direction of the wells is called "along-the-wells" rotation while rotation in the perpendicular direction are called "against-the-wells" rotation. (bottom) The trajectories of incident ions is shown for the two orientations.