## MODEL BASED PERFORMANCE TESTING OF DISTRIBUTED LARGE SCALE SYSTEMS

By

Turker Keskinpala

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

## DOCTOR OF PHILOSOPHY

in

Electrical Engineering August, 2009 Nashville, Tennessee

Approved,

Professor Gabor Karsai

Research Associate Professor Theodore Bapty

Research Assistant Professor Sandeep Neema

Professor Gautam Biswas

Professor Paul Sheldon

Dedicated to my beloved wife Hande, my lovely son Arda, my parents and my brother.

#### ACKNOWLEDGEMENTS

I would like to thank my academic advisor, Prof. Gabor Karsai, whose advice and guidance helped me immensely during my PhD research. This thesis would not be possible without his guidance.

I would also like to thank my research advisor, Research Associate Professor Ted Bapty, for his valuable advice help on setting the vision for the research project. I would like to thank Research Assistant Professor Sandeep Neema for his help and guidance as well.

We spent countless hours with my colleagues Dr. Abhishek Dubey and Dr. Steve Nordstrom discussing various project related issues. It was a pleasure working with them. I would like to thank them for the insight they brought into this thesis and for their invaluable contributions to my research. It was also a pleasure to work on authoring several publications together.

I would like to thank Prof. Paul Sheldon for the insights he brought into this thesis from Physics point of view. I'd like to thank Mike Haney for always being there with his answers and clarifications during our work on CMS project.

I would like to thank my parents and my younger brother for always being there, always supporting me and always believing in me. I would also like to thank my extended family for their support and encouragements.

I would like to thank Institute for Software Integrated Systems and its staff for providing the resources for me to complete my research and taking care of everything that would get in the way.

Last but not least, I would like to thank my wife, Hande Kaymaz Keskinpala, for her endless support and for the sacrifices she made to provide the best possible conditions for me to work on my research. This thesis would not be possible without her support and belief in me. Finally I would like to thank my 13 month old son, Arda, who was clueless about what his dad has been doing in front of the computer for long hours, for being a big motivational push with his existence without being aware of it.

# TABLE OF CONTENTS

|         | Page                                                                                                                                                                                                                                                                                                                                               |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNC   | WLEDGEMENTS iii                                                                                                                                                                                                                                                                                                                                    |

| Chapter |                                                                                                                                                                                                                                                                                                                                                    |

| I.      | INTRODUCTION                                                                                                                                                                                                                                                                                                                                       |

| II.     | A METHOD FOR PERFORMANCE TESTING DISTRIBUTED         MIDDLEWARE BASED SYSTEMS       5         Challenges       5         A Model Based Approach       8         Test Series Definition Modeling Language       12         Modeling Behavior with DEVS       33         Closing the Loop: Performance Engineering       35         Summary       43 |

| III.    | BACKGROUND ON DEVS MODELING FORMALISM<                                                                                                                                                                                                                                                                                                             |

| IV.     | BACKGROUND ON CMS DAQ SYSTEM       52         DAQ Architecture       54         Event Builder       56         RU Builder       58         Event Manager (EVM)       59         Readout Unit (RU)       59         Builder Unit (BU)       60         Summary       63                                                                             |

| V.      | MODEL BASED PERFORMANCE ENGINEERING OF CMS         DAQ SYSTEM       64         System Under Test       65         Application Layer       66                                                                                                                                                                                                       |

|         | Middleware Layer                                                                                                                                            | 3 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|         | Application Simulation Models                                                                                                                               | 9 |

|         | Processor Model                                                                                                                                             |   |

|         | Performance Aspect in Models                                                                                                                                | 7 |

|         | Input Data Generator                                                                                                                                        | 3 |

|         | Performance Monitor                                                                                                                                         | 2 |

|         | Communication Interfaces Between Applications 93                                                                                                            | 3 |

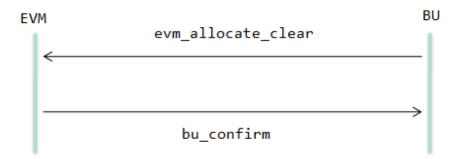

|         | EVM-BU Interface                                                                                                                                            | 3 |

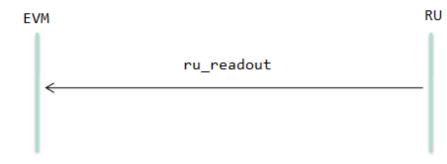

|         | EVM-RU Interface                                                                                                                                            | 6 |

|         | BU-RU Interface                                                                                                                                             | 7 |

|         | Application-Executive-PT Interface                                                                                                                          | 3 |

|         | Application-Processor Interface                                                                                                                             | 9 |

|         | Test Generation from TSDML Models 100                                                                                                                       | C |

|         | Constructing a Test Series Definition 103                                                                                                                   | 3 |

|         | Test Case Generation $\ldots \ldots \ldots$ |   |

|         | Test Execution $\ldots \ldots 120$                                             | 0 |

|         | Results, Analysis and Performance Engineering 121                                                                                                           | 1 |

|         | Comparison to Related Work                                                                                                                                  | 0 |

|         | Summary $\ldots \ldots 136$                                             | 6 |

| VI.     | CONCLUSION AND FUTURE WORK                                                                                                                                  | 7 |

|         | Future Work                                                                                                                                                 | R |

|         |                                                                                                                                                             | ) |

| BIBLIOG | GRAPHY                                                                                                                                                      | C |

|         |                                                                                                                                                             |   |

# LIST OF FIGURES

| Figure | Pa                                                          | age |

|--------|-------------------------------------------------------------|-----|

| 1.     | Applications, Middleware and Platform [1]                   | 3   |

| 2.     | Application metamodel in GME                                | 15  |

| 3.     | Data Flow Aspect of a Sample Application Model              | 17  |

| 4.     | Test Series Definition Aspect of a Sample Application Model | 17  |

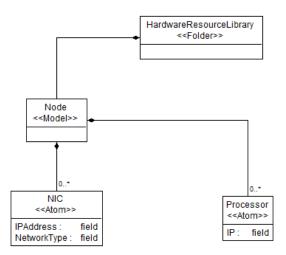

| 5.     | Resource Library Metamodel                                  | 20  |

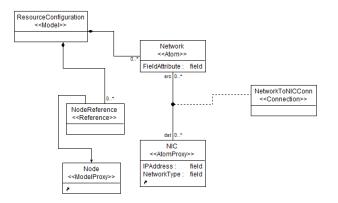

| 6.     | Resource Configuration Metamodel                            | 21  |

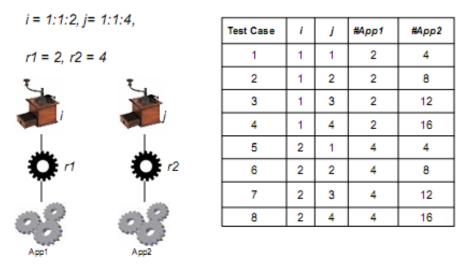

| 7.     | Use of iterators and replicators in the model               | 22  |

| 8.     | Use of iterators and replicators with connectors $\ldots$ . | 23  |

| 9.     | Resulting Configuration for Example 2                       | 23  |

| 10.    | Input Generator Meta Model                                  | 26  |

| 11.    | Test Series Definition Meta Model                           | 27  |

| 12.    | Test Cases Run on System Implementation                     | 38  |

| 13.    | Test Cases Run on Simulation Engine                         | 39  |

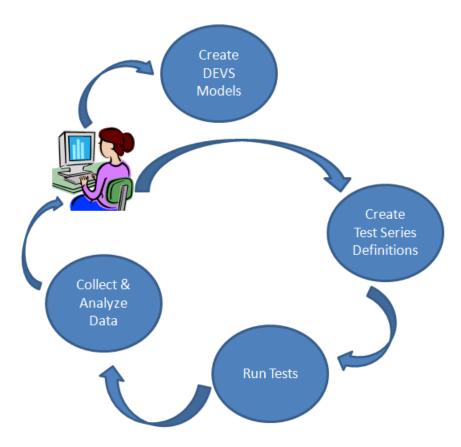

| 14.    | Engineering Process                                         | 42  |

| 15.    | Symmetric Structure of Atomic DEVS [2]                      | 46  |

| 16.    | Atomic DEVS Models [2]                                      | 48  |

| 17.    | A Coupled DEVS Model [2]                                    | 49  |

| 18. | Data Flow in the Trigger/DAQ System              | 53 |

|-----|--------------------------------------------------|----|

| 19. | CMS DAQ System Architecture                      | 55 |

| 20. | Front and Side Views of the DAQ                  | 57 |

| 21. | Three-Dimensional View of the System             | 58 |

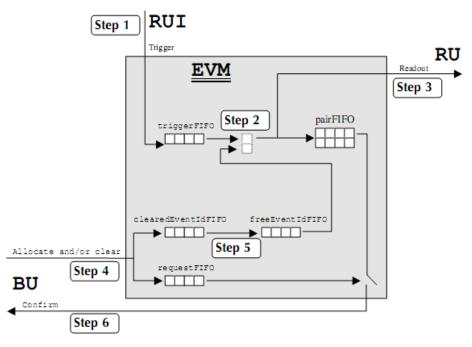

| 22. | Dynamic Behavior of EVM                          | 60 |

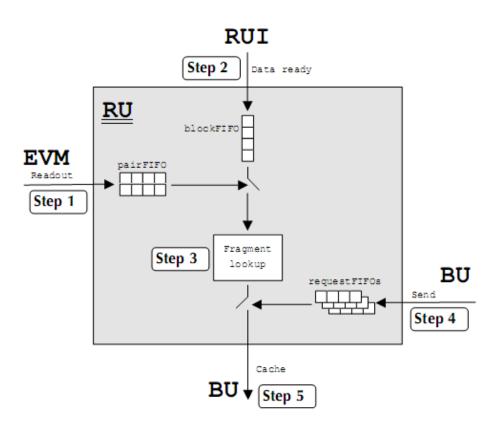

| 23. | Dynamic Behavior of RU                           | 61 |

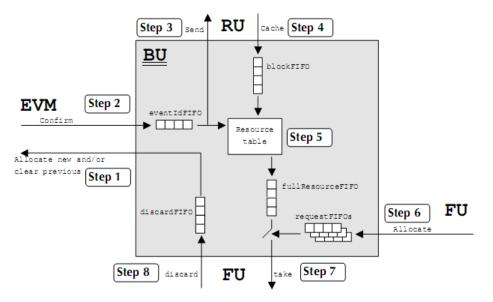

| 24. | Dynamic Behavior of BU                           | 62 |

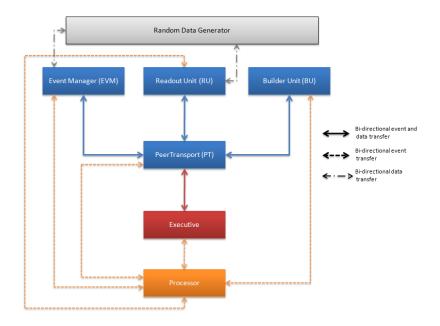

| 25. | System Architecture                              | 65 |

| 26. | Implementation of System Under Test              | 66 |

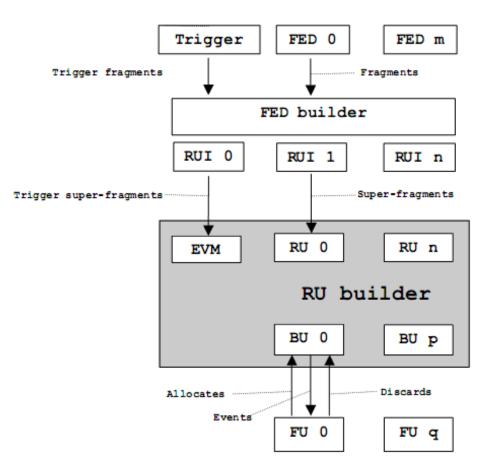

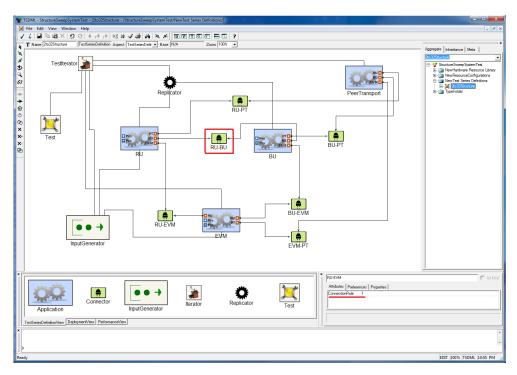

| 27. | RU Builder Connected to Event Builder            | 67 |

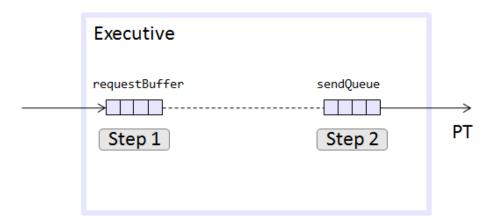

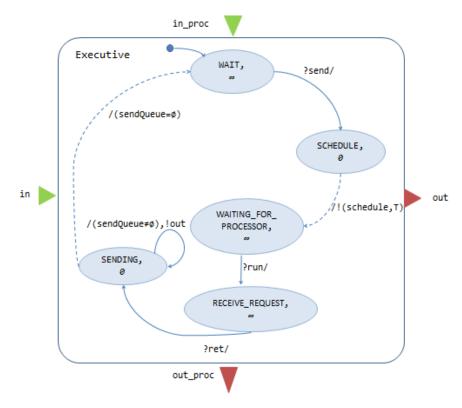

| 28. | Dynamic Behavior and Internal FIFOs of Executive | 69 |

| 29. | Executive Model                                  | 71 |

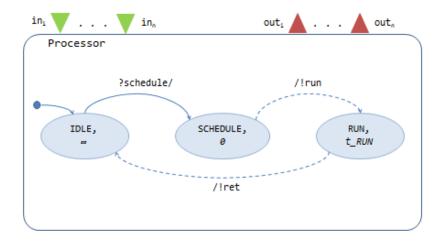

| 30. | Processor DEVS Model                             | 72 |

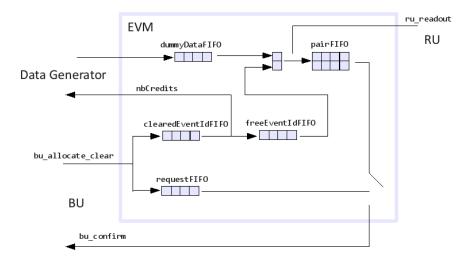

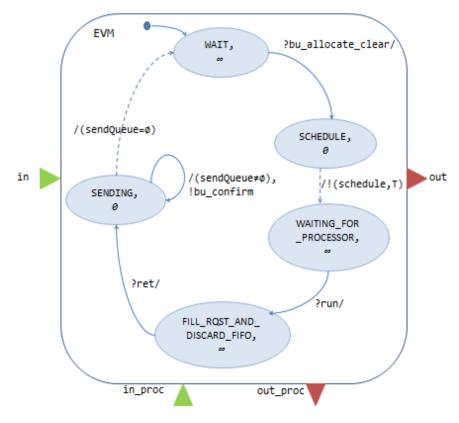

| 31. | Dynamic Behavior and Internal FIFOs of EVM       | 74 |

| 32. | EVM Model                                        | 76 |

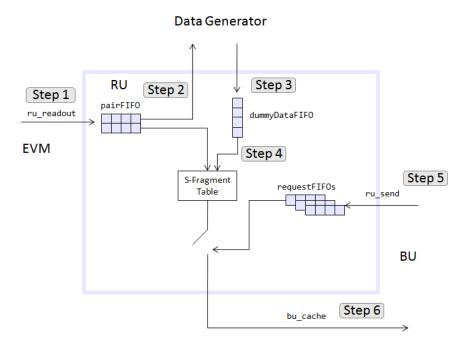

| 33. | Dynamic Behavior and Internal FIFOs of RU        | 78 |

| 34. | RU Model                                         | 79 |

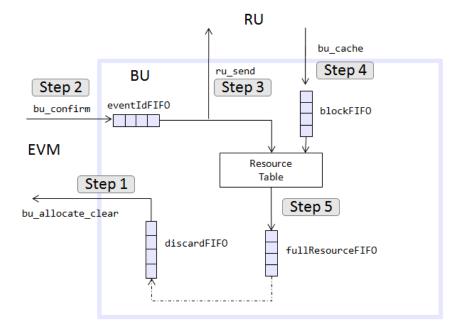

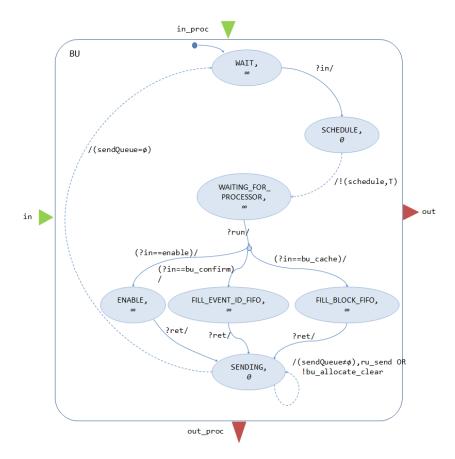

| 35. | Dynamic Behavior and Internal FIFOs of BU        | 81 |

| 36. | BU Model                                         | 83 |

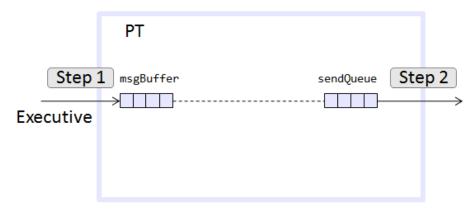

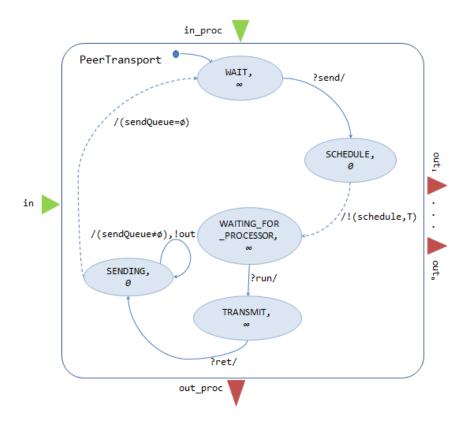

| 37. | Dynamic Behavior and Internal FIFOs of PT        | 84 |

| 38. | PeerTransport Model                              | 86 |

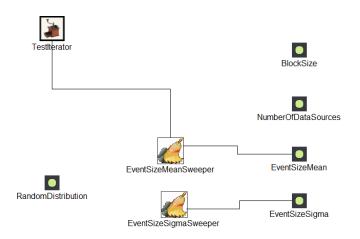

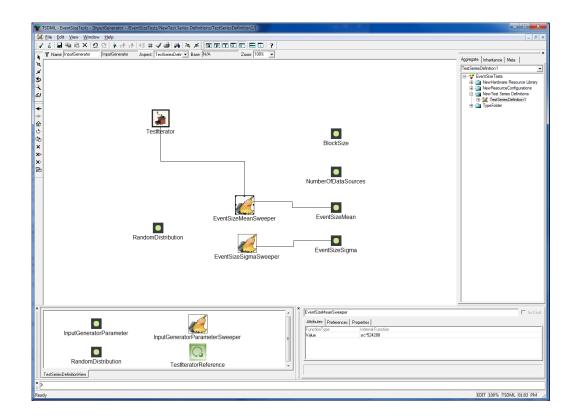

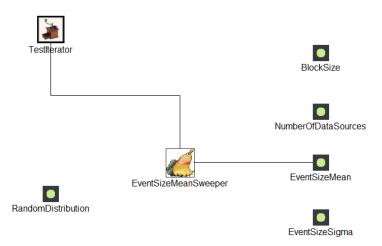

| 39. | Sweeping EventSizeMean and EventSizeSigma 90                                  |

|-----|-------------------------------------------------------------------------------|

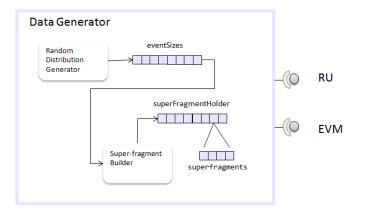

| 40. | Input Data Generator Component View                                           |

| 41. | EVM-BU Interface Diagram                                                      |

| 42. | EVM-RU Interface Diagram                                                      |

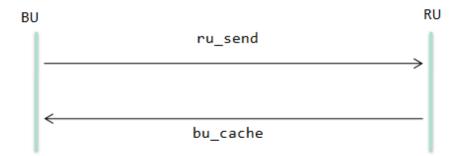

| 43. | BU-RU Interface Diagram                                                       |

| 44. | Executive-Peer Transport Interface Diagram                                    |

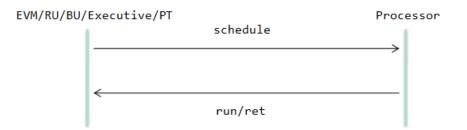

| 45. | Processor-Application Interface                                               |

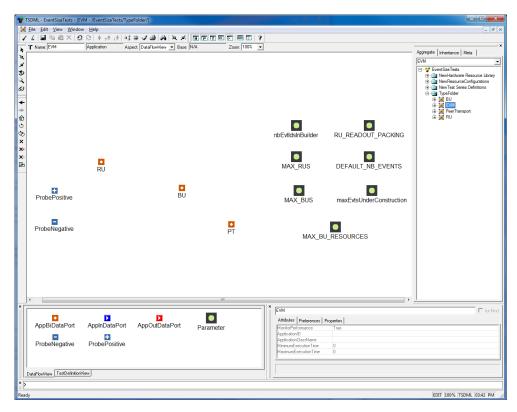

| 46. | Application Type Model for EVM                                                |

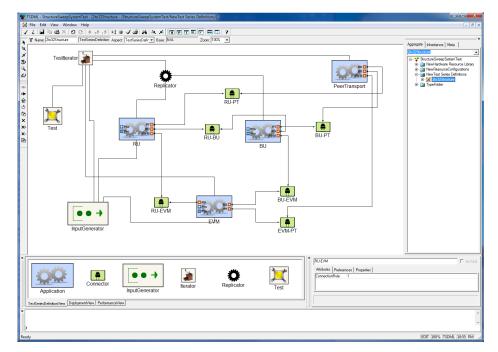

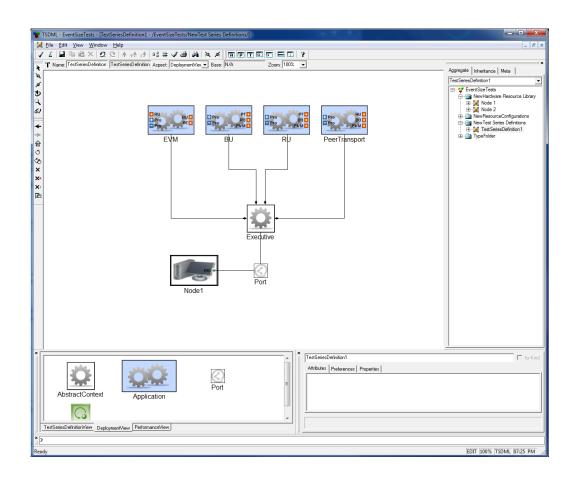

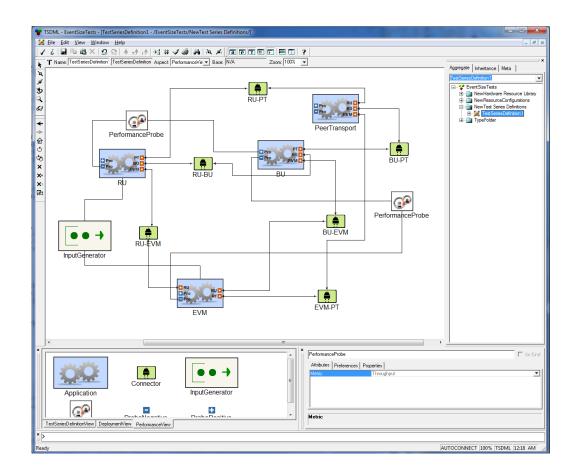

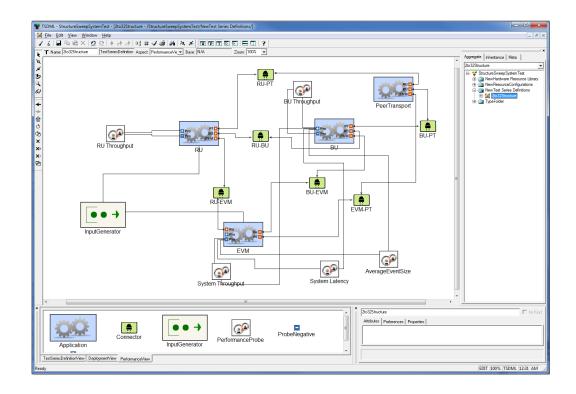

| 47. | Test Series Definition View of a Test Series Definition with      Replicators |

| 48. | Iterator and Replicator Values                                                |

| 49. | Connection Rule is 1: All instances are connected 108                         |

| 50. | Sweeping Application Parameter Value                                          |

| 51. | Sweeping Event Size in Input Generator                                        |

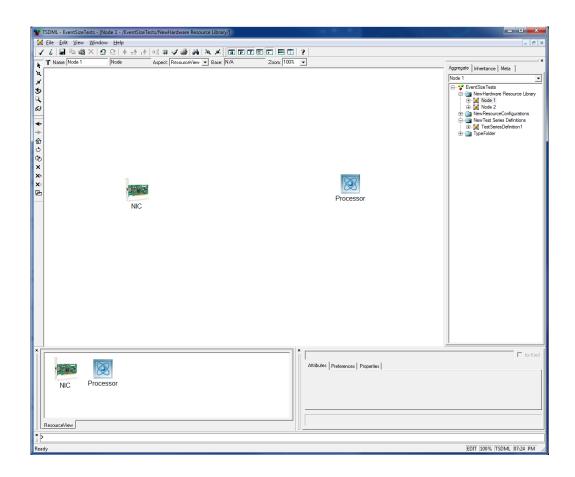

| 52. | Model of a Node in Resource Library                                           |

| 53. | Deployment View of Test Series Definition                                     |

| 54. | Performance View of Test Series Definition                                    |

| 55. | Metric Choices for Performance Probe                                          |

| 56. | Test Generation Process                                                       |

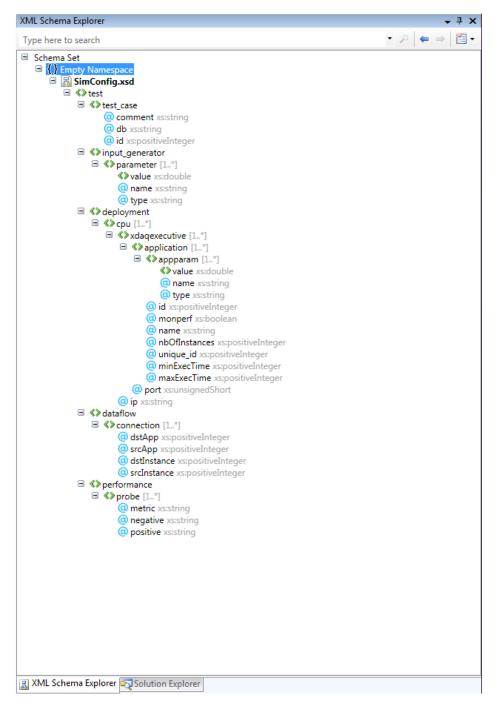

| 57. | Test Case Schema                                                              |

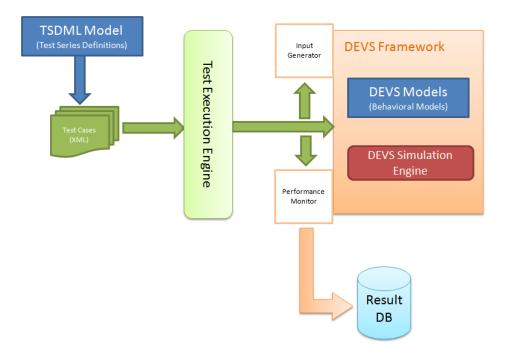

| 58. | Test Case Execution                                                           |

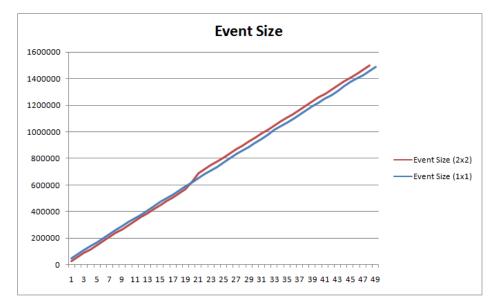

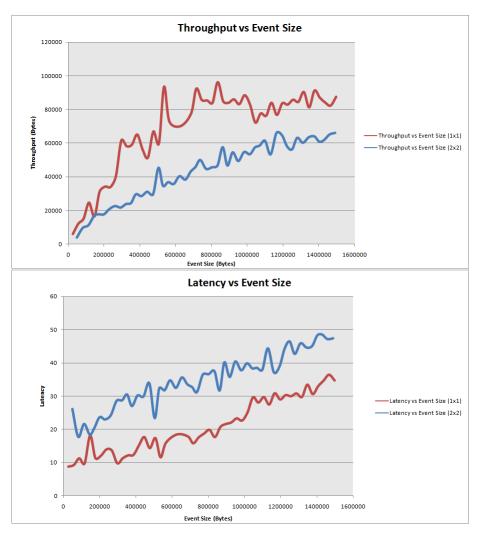

| 59. | Event Size Variation                       |

|-----|--------------------------------------------|

| 60. | Event Size Variation                       |

| 61. | Throughput vs Event Size                   |

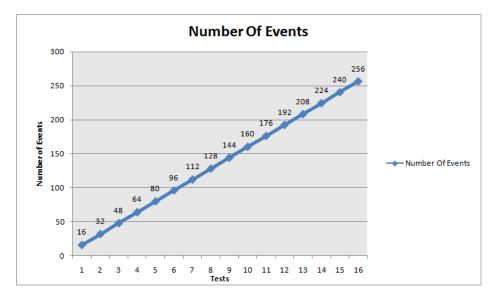

| 62. | Variation in Number of Events              |

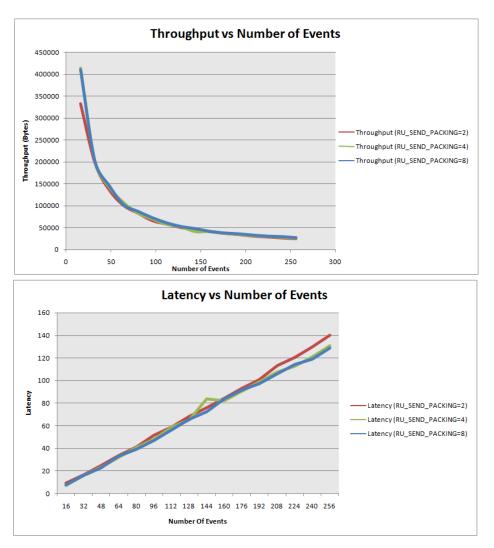

| 63. | Throughout and Latency vs Number of Events |

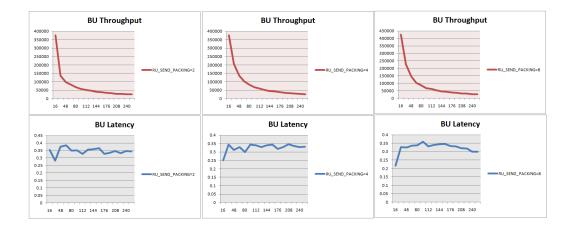

| 64. | BU Throughput and Latency                  |

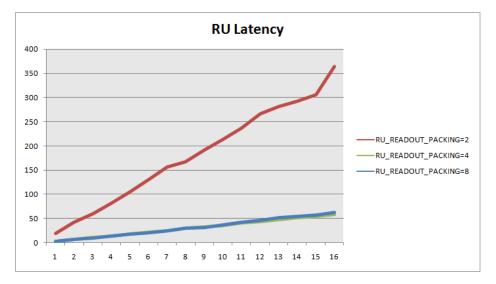

| 65. | RU Latency                                 |

## CHAPTER I

#### INTRODUCTION

Size and complexity of software systems are increasing and there is increasing demand for component based distributed applications and systems. Performance characteristics such as throughput and scalability are crucial quality attributes of such systems. For this reason, it is very critical to validate that the system satisfies the performance requirements. Performance testing is a way to evaluate the design of the system with respect to performance requirements.

IEEE Standard Glossary of Software Engineering Terminology defines performance testing as "testing conducted to evaluate the compliance of a system or component with specified performance requirements" [3]. This definition will be taken as the working definition in the scope of this thesis. In [4], Weyuker and Volokos list possible goals for performance testing as follows:

- 1. "the design of test case selection or generation strategies specifically intended to test for performance criteria rather than functional correctness criteria."

- 2. "the definition of metrics to assess the comprehensiveness of a performance test case selection algorithm relative to a given program."

- 3. "the definition of metrics to compare the effectiveness of different performance testing strategies relative to a given program."

- 4. "the definition of relations to compare the relative effectiveness of different performance testing strategies in general."

- "the comparison of different hardware platforms or architectures for a given application."

The notion of performance testing in this dissertation is the first of these goals. An approach that focuses on *generating performance test cases that* can be used to exercise the system will be described in the upcoming chapters.

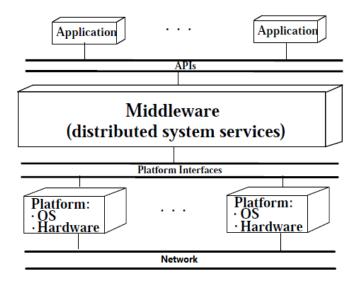

Distributed systems are generally built on top of middleware services. Middleware services are general-purpose services that are positioned between applications and the operating system (OS) and implement low level OS and hardware application programming interfaces (APIs) [1].

Primary goal of middleware is to provide the means for applications to connect and interact with each other and the underlying platform. The underlying platform is OS, network protocols, and hardware that it runs on. Furthermore, middleware aims to make the integration of heterogeneous applications easier [5]. Middleware is often component based. Components that implement platform APIs to facilitate communications, memory management, event notifications, etc. can be middleware services [1]. Such components that are middleware services hide implementation details of the underlying platform from the applications.

Figure 1: Applications, Middleware and Platform [1]

Large scale distributed systems often have stringent performance requirements. Throughput, latency, scalability are important performance metrics for such systems [4, 6]. For this reason, performance testing plays an important role in middleware based distributed systems.

In this thesis, it will be recognized that there is a need for a way to characterize and capture performance characteristics of components and the component model in a distributed system so that the effect of complex component interactions on system performance can be explored. In order to be able to test the performance of the system by taking into account the couplings of components and middleware, component interactions should precisely be understood and captured from a performance perspective in a component oriented performance model. An approach focusing on this need will be presented in the following chapters. In Chapter II, the approach will be explained in detail. Chapter III will present a brief background on Open DEVS modeling formalism followed by Chapter IV which give the background on CMS DAQ system that will be used for implementing the approach. Chapter V will dive into the details of implementation of the approach on the CMS DAQ system along with results and analysis. Finally, Chapter VI will summarize the approach and implementation along with ideas on how the approach can be improved by future work.

## CHAPTER II

## A METHOD FOR PERFORMANCE TESTING DISTRIBUTED MIDDLEWARE BASED SYSTEMS

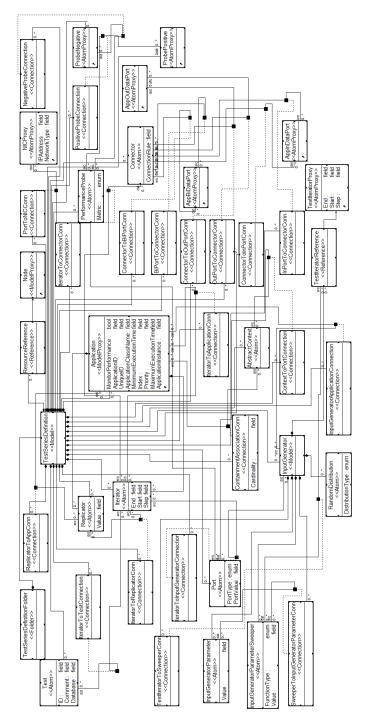

In this chapter a method to help build a distributed middleware based system, capture its performance characteristics and perform performance testing and/or performance engineering on it will be introduced. The method consists of creating a domain specific modeling language for capturing the structure and performance characteristics of the system, and creating a discrete event based system model to capture the behavior of the system.

The domain specific modeling language is created by using the concepts and tools introduced by Model Integrated Computing (MIC) [7]. A brief background on MIC will be given in the following sections in this chapter. The behavioral model is created by Discrete Event System Specification (DEVS) which is a modeling and analysis formalism for discrete event systems [8]. A background of DEVS is given in Chapter III.

#### Challenges

In Chapter I it was mentioned that large scale distributed middleware based systems generally have stringent performance requirements and that performance testing plays an important role in middleware based distributed systems. Middleware platform provides services such as transactions, and remote communication which affect the performance of a system in a major way. The role of middleware often makes it the entity that is most influential on the overall performance of the system [9]. Although the major effect of middleware on the whole system performance cannot be denied, it is also important to consider the relationships of the applications with each other and the middleware services when performance testing a system. This requires detailed understanding of these interactions and the ability to create the conditions to properly test those interactions.

It is also important to take into account the context of the middleware since it may behave differently in the context of different applications [10, 11]. For example, if middleware hosts mostly applications that use its event management services to pull event status information periodically, there will not be many frequent and complex interactions between applications and the middleware. Thus, the middleware may perform very well. On the other hand, if there are many applications that are constantly using communication services of a middleware to perform operations on the underlying OS and/or hardware layer, middleware performance will be different. Tight coupling between the applications and the middleware services will potentially cause complex component interactions. Those complex interactions will potentially affect the performance of the system. As applications cannot be executed without the underlying middleware services, it is not sufficient to perform performance testing on the applications in isolation in order to understand the performance of the system. Likewise, performance testing middleware in isolation would not be enough because coupling with the applications that use its services is too important to ignore.

A typical performance testing goal is to test a system under various workloads in order to evaluate how the system will perform when deployed. For example, when performance testing a large industrial client/server transaction processing system, a real challenge is to determine what a representative workload is [4]. In addition, it is also identified in [4] that lack of earlier version of a system presents a challenge in coming up with a representative workload. Another interesting challenge identified in [4] is how to measure and interpret the observations. This is interesting because the implication is that selecting what to measure and how to measure for performance testing may affect the objectivity of performance results.

An aspect of testing a distributed middleware based system and its components is creating many configurations that would configure functional operation of components as well as their deployment in the cluster. The configurations are usually described by XML. It is cumbersome and inefficient for test engineers to write XML test configurations by hand as the tester would be making many copy-paste operations which can introduce errors into the process. Moreover, the configuration space of the control and deployment parameters of applications within the framework is sufficiently large; there is no way for the tester to manually create configurations for all possible combinations of parameters. Last but not the least, it would be very time consuming to scale up and modify a manually written XML test configuration in response to changes in hardware resources or other test criteria.

In the following section, an approach based on model based testing and test generation will be described.

#### A Model Based Approach

In the previous section, several challenges for performance testing a distributed middleware based system was given. As a result of a literature review on the subject matter [12], the following observation was made: There is a need for a way to characterize and capture performance characteristics of components and the component model in a distributed system. Such a model would help explore the effect of complex component interactions on system performance. In order to be able to test the performance of the system by taking into account the couplings of components and middleware, component interactions should precisely be understood and captured from a performance perspective in a component oriented performance model. Such a performance model can be used to automatically generate executable performance test cases.

A systematic modeling approach for characterizing and capturing distributed system components' and underlying middleware's performance properties can be used to tackle the challenges described above. The systematic modeling can also be used to investigate the effects of different applicationapplication and application-middleware interactions on the performance of the system. A domain specific modeling approach will be used for the following reasons:

- Domain of middleware based distributed systems is a well known and studied domain, and it is possible to come up with a domain specific modeling language.

- A domain specific modeling language is a manageable solution compared to a general purpose solution since it's tailored to the specific domain.

- A model based approach enables including performance testing at an earlier point in the development life cycle. Models of a system can be created and performance characteristics of a system can be captured in models during as early as requirement/specification phases.

- A model based approach is flexible to changes introduced to the system. When a behavioral or structural change is introduced to the, it can be reflected on the models. Similarly, if performance characteristics are changed, they can be easily reflected on the models.

The systematic modeling approach which is described in this chapter uses a two layered modeling approach. One layer of modeling is done using a model based design methodology called Model Integrated Computing (MIC) [13, 7]. The second layer of modeling is done using the Discrete Event System (DEVS) Specification modeling and analysis formalism for discrete event systems which is described in Chapter III.

As a model based design methodology, MIC provides a scalable methodology for system design and analysis based on sound system theory and abstraction by integrating the efforts in system specification, design, synthesis, validation, verification and design evolution. MIC brings in key concepts of domain modeling to the paradigm of model driven system development. A key capability supported by MIC is the definition and implementation of domain-specific modeling languages (DSMLs). Crucial to the success of DSMLs is metamodeling and auto-generation. A metamodel defines the elements of a DSML, which is tailored to a particular domain. The modeling language which is used to construct metamodels is known as a metamodeling language. Auto-generation involves automatically synthesizing useful artifacts from models, thereby relieving DSML users from the specifics of the artifacts themselves, including their format, syntax, or semantics.

MIC methodology is found to be suitable for carrying out the modeling task. The properties of the MIC methodology provides a strong means to tackle challenges mentioned above. Using MIC and its accompanying tool Generic Modeling Environment [14] enables the creation of a DSML targeted for distributed middleware based systems and enables incorporating performance testing aspects. Furthermore, auto-generation capabilities of GME enables synthesis of series of configurations and tests. On the other hand, DEVS modeling formalism enables modeling the behavior of MIC model components and provides a event based simulation engine for easily observing the effect of changes in behavior in the performance of the system.

The modeling methodologies will enable modeling of the following about the system:

- MIC will allow capturing data flow and deployment information about the system. This involves modeling the middleware component, applications, resources and their connections to capture how data flows in the system and how they are deployed.

- MIC will allow modeling performance characteristics of the system in addition to data flow and deployment. This involves modeling the parts of the system which will guide the test case selection and generation strategies.

- DEVS will allow modeling behavior of middleware and applications. This involves determining different states and state transition conditions of the middleware and applications.

The following steps are involved in using the model based approach that is described in this chapter:

- Identify the applications (including the middleware) of the system and their configuration parameters

- Identify the relationships and interactions between applications

- Identify the structure and data flow in the system

- Identify the behavior of each application in the system

- Identify the physical (processor, network card) and logical (ports) resources that will be needed in the system

- Model identified applications, their relationships, and resources using the Test Series Definition Modeling Language (TSDML)

- Model the behavior of the applications and the event based data flow using DEVS modeling formalism

- Identify performance metrics for the applications and the system

- Configure the DEVS behavioral model with the information captured in TSDML

- Run the DEVS simulator to collect performance results

- Alternatively, run the system with the configuration generated from the TSDML

In the following section, the domain specific modeling language called Test Series Definition Modeling Language (TSDML) will be described in detail.

#### Test Series Definition Modeling Language

Test Series Definition Modeling Language (TSDML) is a domain specific modeling language designed to model distributed component based systems from a performance testing point of view. TSDML aims to make it easier to capture the structure and interaction of components along with the performance characteristics of the system.

The TSDML has the following high level properties:

- Define application types

- Define the connection association between applications by connection rules

- Define association rules between applications and contexts

- Define association rules between connections and logical networks

- Define association rules between context and hosts

- Define replication factors for the types and connections

- Form a template test case from the modeled applications, connections, and resources

- Define the scope of the test series

In the following sections details of the modeling process and abstraction levels for these aspects will be described.

#### Modeling Application Types

An important advantage of using a MIC model based methodology is the ability to view the system to be modeled from different aspects and enable separation of design concerns. Aspects help define visibility of different parts of the model by grouping. An aspect is defined when a group of parts of a model are made visible in that aspect [15]. Modeling a system from different aspects means making different parts of a model visible in different aspects. For example, a model may have a data flow aspect which has parts like components, ports and connections as visible. A model may also have a deployment aspect which has parts like processors, computers, network switches as visible.

From this perspective TSDML defines two different aspects for modeling an application (type): Data Flow Aspect and Test Definition Aspect.

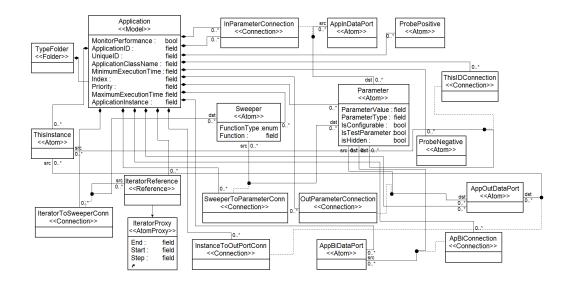

From the Data Flow Aspect an application is modeled to contain Parameters, Input Data Port, Output Data Port, and Bidirectional Data Port. From the Test Definition Aspect an application is modeled to contain Sweeper (see Subsection II), Negative Probe, Positive Probe and reference to Iterator (see Subsection II). The application metamodel is shown in Figure 2. A metamodel is a UML class diagram, representing the abstract concepts, relationships, and attributes used in a DSML. For more details please see [16].

The Data Flow Aspect lays out the data ports that the application has and the parameters to configure the application. The data ports can be input only, output only and bidirectional. The application has the following attributes:

Figure 2: Application metamodel in GME

- MonitorPerformance: Boolean flag to denote whether the performance of the application needs to be monitored

- ApplicationID: Unique identification number of the application

- ApplicationClassName: Class name of the application's implementation

- MinimumExecutionTime: Minimum execution time of the application

- MaximumExecutionTime: Maximum execution time of the application

The parameters of the application have the following properties:

• ParameterValue: Value of the application parameter

- ParameterType: Basic type of the application parameter (e.g. double, int)

- IsConfigurable: Boolean flag to denote if the parameter is a configurable parameter

- IsTestParameter: Boolean flag to denote if the parameter is a test parameter

The Test Definition Aspect provides Sweeper to vary the values of test parameters of an application and Negative Probe and Positive Probe to attach performance measurement points. These will be explained in detail later.

Sweeper is an important element in TSDML which has the following attributes:

- Function Type: Internal function or look-up table. Internal function is a function of test series iterator whereas the look-up table may have specific values that an application can take.

- Function: The definition of the function.

Sweeper is attached to an application parameter and varies the value of the parameter based on the function provided in its attribute. A new value for an application parameter is used in each test case that will be generated from the model.

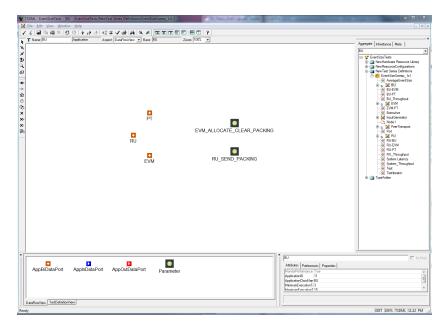

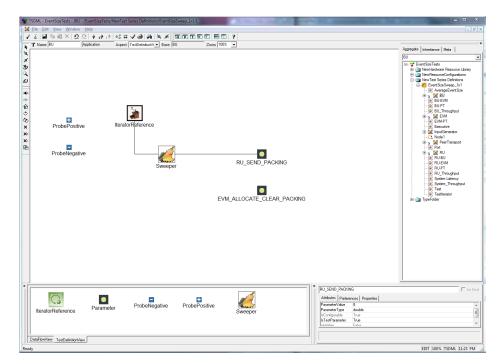

Figure 3 shows the Data Flow and Figure 4 shows the Test Series Definition aspect of sample application model.

Figure 3: Data Flow Aspect of a Sample Application Model

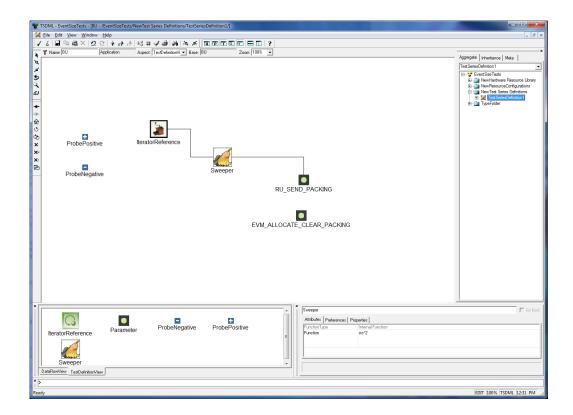

Figure 4: Test Series Definition Aspect of a Sample Application Model

In the Data Flow aspect seen in Figure 3, parts of the application model that are related to data flow are visible. These are parameters, and data ports. In the specific model shown in the figure, the application is modeled to have four parameters, namely, *blockFIFOCapacity*, *RU\_SEND\_PACKING*, and *requestFIFOCapacity*, *EVM\_ALLOCATE\_CLEAR\_PACKING*. In addition, the application is modeled to have three bi-directional ports connecting it to other applications.

In the Test Series Definition aspect seen in Figure 4, parts of the application model that are related to test series definition are visible. These are parameters, Sweeper, reference to the iterator, negative and positive probe points. In the specific model shown in the figure, the application is modeled such that the *RU\_SEND\_PACKING* parameter is attached to a Sweeper which means that the value of that parameter will be varied in each iteration. Positive and negative probes of the application are the points where performance probes will be connected. Performance probes will be explained shortly.

Modeling application types in this manner tackles several challenges mentioned in the previous sections. This approach treats both the middleware and its applications as application types and enables modeling and configuration of them separately. For this reason, it will be possible to consider not only middleware-application relationships but also application-application relationships. In addition, it'll be possible to identify the couplings between middleware and applications that use its services.

#### Modeling Resources and Resource Configurations

TSDML includes a way to model the resources to be used to deploy the system. Two main parts are the resource library and the resource configurations. TSDML has been constructed such that resource library collects models of the resources that can be used in a resource configuration. Resource configurations use references to resource models in the library to define specific configurations.

A resource is described as a *Node* in TSDML. TSDML uses the following entities and their attributes to define a node:

• Network Card (NIC)

IP Address

Network Type (e.g. Gigabit, Infiniband, etc.)

• Processor

## IP Address

Resource configuration model is described by a reference to a node that is created in the resource library model. The main point of a resource configuration model is to define the connections between the nodes. A connection between nodes is made through the *Network* entity. TSDML uses the following entities and their attributes to define a resource configuration:

• Node Reference: Reference to a node created in resource library

Figure 5: Resource Library Metamodel

• Network

Network Type (e.g. Gigabit, Infiniband, etc.)

Resources and resource configurations are modeled on a high level of abstraction by hiding many details. For example, a node is modeled as a box containing only a network card and processor and hides many details of the network card and the processor and many internal connections. Similarly, model of a resource configuration hides the details of how the connection between nodes is implemented. However, these models can easily be extended to drill down to the details of resources and resource management.

Figure 6: Resource Configuration Metamodel

#### Parameterizing the Model

As mentioned previously, it is desired that the TSDML model should be parametrized in order to be able to generate series of test cases from a single model. The parameterization is achieved by using "Iterator" and "Replicator" entities in the system model.

**Iterators** are used to define the series  $i, j, k \dots$  for the notions of *start*, *step*, *stop*. There can be many iterators in a test series definition.

**Replicators** are used to define the replication factor for the attached object. The replication factor determines how many of the object to which the replicator is attached to will be generated when the model is interpreted. Replicators are functions of iterators as in  $r = K \times si$ . There can be many replicators in a test series definition. Replicators must be attached to an iterator in the model since they are functions of iterators. They must also be attached to an application, network or context entity.

Figure 7: Use of iterators and replicators in the model

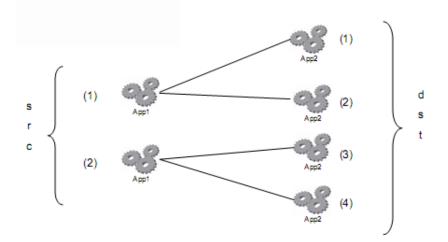

Figure 7 shows a possible example use of replicators and iterators in the model to generate multiple instances of two different application models.

In the example, it is assumed that i = 1 : 1 : 2 and j = 1 : 1 : 4 and r1 = 2 and r2 = 4. By design, iterators function as the outer loop whereas the replicators function as inner loops. In this case, the table in Figure 7 shows the total number of test cases that will be generated and the numbers of App1 and App2 instances in those test cases. In this example, total of 8 cases will be generated and number of App1 instances will change between 2 and 4 and the number of App2 instances will change between 4 and 16.

Iterators and connectors also function similarly when there is a connector between applications. Figure 8 shows an example of such a situation.

Figure 8: Use of iterators and replicators with connectors

Figure 9: Resulting Configuration for Example 2

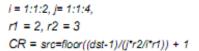

As described above, since connectors are boolean functions of iterators and replicators, it is possible to define the connection relation between applications with respect to the iterators and replicators to which the applications are attached to. In the example shown in Figure 8, iterator *i* is defined as i =1:1:2 and iterator *j* is defined as j = 1:1:4 and replicators r1 and r2 are defined as 2 and 3 respectively. The connection relation between applications is defined as the boolean function  $src = floor((dst - 1)/(j \times r2/i \times r1)) + 1$ . As can be seen in the figure, App1 is the source (src) and App2 is the destination (dst).

In order to fully understand what type of a model this example will lead to, we should first consider the iteration and replication of the applications. This example shares the same configuration for applications as shown in Figure 7. That is, there will be a total of 8 test cases. For the first test case, there will be 2 instances of App1 and 4 instances of App2. The connection between these applications is determined by the connection relation and results in the configuration shown in Figure 9.

Modeling iterators and replicators as part of the TSDML aims to tackle the challenge of writing and managing many test configurations. By using iterators and replicators and taking advantage of auto generation capabilities of the modeling approach, a test engineer will be able to create and control many test cases with minimal effort. The concept of iterators and replicators easily and conveniently achieve the parameterization goal of the TSDML and enable creation of series of test cases from the single test template model.

#### Modeling Input Generator

Input Generator is an important entity in the TSDML. It is not necessarily part of the overall system however it is crucial to model the input to the system for testing purposes.

In TSDML, input generator is modeled as a construct containing some parameters. The input generator is assumed to be used for generating events for the event based system. The following parameters make up the input generator:

- Input Generator Parameter: Any parameter that may relate to modeling an input generator (e.g. mean, sigma, etc.)

- Random Distribution: Enumeration to model the type of distribution (e.g. Lognormal, normal, exponential, etc.)

- Parameter Sweeper: Similar to application types, a sweeper can be connected to parameters to vary the values of parameters for each test

- Iterator Reference: Reference to the iterator used for test series definition.

Most important part of the input generator model is parameter sweeper. It is the same sweeper that is used for varying values of application parameters. By connecting the iterator reference to a sweeper, values of input generator can be varied for each test case to be able to test the system against varying input data.

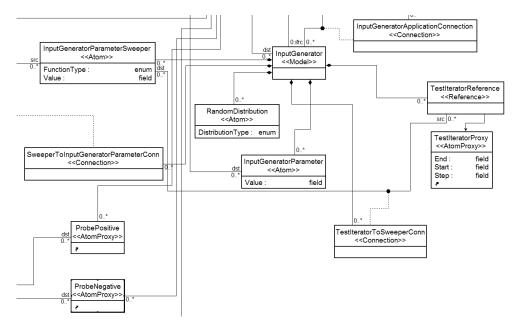

Based on the design of the system, the input generator can be connected to any application which accepts the input data and is the trigger for the operation of the system. Figure 10 shows the Input Generator portion of the TSDML metamodel.

Figure 10: Input Generator Meta Model

Figure 11: Test Series Definition Meta Model

# Modeling Test Series Definitions

Test series definition models bring together all the entities of the TSDML from a test generation perspective and enables generation of series of test cases utilizing model parametrization described in the previous subsection.

An important advantage of using MIC model based methodology is the ability to view the system to be modeled from different aspects and enable separation of design concerns. From this perspective TSDML defines three different aspects: Test Series Definition Aspect, Deployment Aspect, Performance Aspect. All there aspects of modeling a test series definition will be explained in detail.

The **Test Series Definition Aspect** includes all the modeling elements that were described in the previous subsections. Test Series Definition aspect acts like a design surface for designing series of test cases. It contains the following modeling elements:

- Application Reference

- Iterator

- Replicator

- Connector

- Input Generator

- Test entity

### • Connections between these entities

References to application types and connectors that connect the applications make up the data flow among the applications. In order to create a test series definition not all application types need to be present. Different test series definitions with different applications and with same applications and different parameter values can be modeled since test series definitions are collected under a folder structure and lead to different set of test cases.

Iterators and replicators are the entities which define the scope of the series and add parameterization to the test series definition model. As described in "'Parameterizing the Model"', a replicator enables using a single application type and generate multiple application instances during test case generation. By use of replicators and iterators, it is possible to easily create a template of an application to be replicated at each step of test case generation.

Connector defines the relationship and data flow between the applications. When a connector entity is used to connect ports of two applications, it denotes that there is a data flow between those applications. As explained before, it is also a very powerful entity with its ConnectionRule property which is a function of the iterator. Making connections this way enables variations on the application structure that is to be tested.

The InputGenerator entity supplies the test data to the system to drive the test run. It can be connected to the applications which are expecting data to be enabled. The Test entity is a placeholder entity which captures the general information about the test that is being designed. The information captured is used to store the results of the test run appropriately in a database or test log. The primary attributes of the Test entity are the Comment and Database fields. The Comment field is used to give a brief description of the test series being designed. The Database field is used to capture the name of the database that the test results will be saved to.

A test series definition is obtained when all these entities are connected to each other appropriately. The number of test cases that will be generated from one test series definition is based on the value of the iterator.

The Test Series Definition aspect provides the solution for the challenge of manually creating several XML test configurations and makes the process easier to scale and less time consuming. In addition, by bringing together the pieces that are mentioned in the previous sections, this view makes it possible to span a considerable portion of the configuration space of parameter applications. This is made possible by being able to change application parameter values by means of Sweepers and control this change by iterators and replicators for each test case.

The **Deployment Aspect** includes modeling entities that can be used to devise different deployment scenarios for the system. The following entities can be used in this aspect:

• Application (Reference)

- Resource (Reference)

- Middleware

- Port

Any common entities across aspects are carried over to the respective aspect. For this reason, the application reference is the same as the on used in the Test Series Definition aspect. The difference across different aspects is the perspective those entities are being looked at. While in the Test Series Definition aspect, the application reference was viewed from the perspective of creating a test series definition with multiple instances of applications generated automatically. In this aspect, the applications are viewed from a deployment perspective. The connections that are to and/or from an application reference are related to the deployment aspect of the system.

Resource reference is a reference to any resource that is modeled in the Resources and Resource Configurations. Deployment aspect is the only place where a resource can be utilized because it's inherently related to deployment. From the testing perspective, having a resource model in this view makes it possible for a test designer to deploy a system on various resources and devise several test cases.

Another entity in the Deployment aspect is Middleware. It is a key entity for deployment because applications cannot run in absence of middleware and have to be deployed in a middleware instance. Technically, middleware is no different than an application, it's defined and modeled with application types. However, it's special in the sense that can contain other application types. As applications can be deployed on middleware, middleware is deployed on resources on specific ports.

Port, as the name suggests, is a logical entity used to define endpoint for the application on the resource that it is deployed to. It is used to connect middleware to a resource. Port has the following attributes:

- Port Type: Type of port (e.g. TCP/IP, SOAP, etc.)

- Port Value: Value of port (e.g. 8080, 4000, etc.)

The Performance Aspect includes entities related to capturing performance information about the system. The main entity of this aspect is the Performance Probe. It's designed to be analogous to a voltmeter or ammeter used to measure electric voltage and current in electronic circuits. In this manner, a performance probe is connected to positive and negative end points and measures a performance metric between those points.

A performance probe has one attribute:

• Metric: It's an enumeration of possible performance metrics to be measured (e.g. throughput, latency, bandwidth).

For example, when a performance probe is connected between the negative probe end of App1 and positive probe end of App2 and its metric is set as Throughput, it means that throughput between App2 and App1 will be measured. All the aspects of the Test Series Definition make up the main parts of the TSDML. Test series definition uses the modeling constructs defined elsewhere to model a system from test, deployment and performance points of views.

### Modeling Behavior with DEVS

The Test Series Definition Modeling Language makes it possible to model the system from various perspectives. It is a graphical domain specific language that can be used to capture structure and data flow of a system from a higher level of abstraction. TSDML also enables the design of a system from the testing perspective.

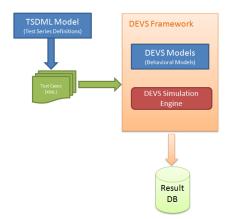

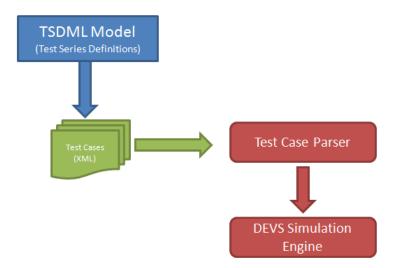

In model driven engineering, the crucial step after modeling a component or a system is to be able to interpret the meaning of the abstractions in the model. The artifact of such interpretation can be a design document, source code, etc. In the case of the approach described in this chapter and the TSDML, the desired artifact is several test cases (e.g. in the form of XML configurations) that can be executed on the real implemented system.

In some cases, the real implementation of the system modeled by TSDML may not be available. Moreover, it may not always be feasible to execute the test cases on the real system. An implementation of the system may not yet be available or it may be costly to run unpredictable tests on the real implementation or replicate the real system setup for testing purposes. In such cases, it is important to be able to model the behavior of the system as well. In the approach described in this chapter, the behavior model of the applications of the system is created using the Open DEVS modeling formalism. A background on Open DEVS is given in Chapter III.

DEVS modeling formalism and the underlying simulation framework enables the execution of test cases generated from TSDML on a simulated system. In order to achieve that, each application type that is modeled using TSDML should have a corresponding DEVS behavior model. An application is modeled using DEVS as described in Chapter III. The main aspect of this process is correctly determining:

- States of the application

- Input and output events of the application

- Input and output connections/ports of the application

Since DEVS is an event based framework, it is possible model the data flow and interactions among applications. In a middleware based system, it is particularly important to determine interactions between applications. It is possible with DEVS to model the application interaction in such a way that no application can talk to each other without going through middleware.

An example implementation of a DEVS model will be given in Chapter V.

### Closing the Loop: Performance Engineering

In Chapter I, it was stated that the scope of the approach described in this thesis is within the boundaries of designing "'test case selection or generation strategies specifically intended to test for performance criteria rather than functional correctness criteria"'.

Although the description and the goal is pretty clear and easy to understand, some questions and details are hidden below the surface. Functional requirements define how the system is supposed to behave whereas nonfunctional requirements define the expected operation of the system beyond the functional behavior, e.g. response time. Non-functional requirements are harder to gather and define than functional requirements. Similar difficulty exists in testing non-functional requirements [17]. The difficulty generally stems from the nature of non-functional requirements being frequently observed and evaluated subjectively. Performance is such a non-functional system requirement. Non-functional requirements like performance are usually evaluated, analyzed or even predicted during design time and rarely monitored and tested during run-time.

The integration of performance analysis with the engineering process is commonly called as performance engineering. The first approach to integrating performance analysis with development cycle early on has been the Software Performance Engineering (SPE) methodology. SPE was first introduced by Smith in her seminal work in early 90s [18]. The goal of SPE is to provide guidelines for performance modeling throughout the software development cycle [19].

In the core of the SPE methodology, there is the domain analysis and object-oriented development. The models that are created as a result of the domain analysis are used to predict the performance of software systems in an early stage. The performance model to be used to implement SPE methodology depends on the purpose of the analysis. Smith lists three analysis strategies that guide the model selection [19]:

- Adapt-to-precision strategy: Availability of system information knowledge directs the modeling effort. Using easy to construct models is suggested.

- Simple-to-realistic strategy: Abstracting away details initially and then adding more details incrementally as the system evolves is suggested.

- Best-and-worst-case strategy: In the early stages of software development, the input data is rarely complete and precise. Thus, investigating performance bounds with best-case and worst-case data sets is suggested.

The main elements of the SPE methodology are Software Execution Models and System Execution Models. First, the important aspects of the software performance behavior is modeled with execution graphs [18] to form the Software Execution Models. The execution graphs are then used to generate parameters for the System Execution Model. The system execution model includes information regarding the hardware resources including queue-servers and their possible connections throughout the system. Execution scenarios are formed from these possible connections which form the model workloads. System execution models are analyzed [20] and the solution results in meanvalue results. The mean-value results are checked against performance goals and if the performance is not satisfactory, system designers turn back to models to work on more advanced system execution models [19].

In the previous sections, an approach for modeling a system's behavior and structure from performance perspective was described. The approach described enabled generation of many test cases from TSDML models to be executed on a discrete-event DEVS simulation engine running behavioral models of the system. There are two paths that can be taken from the model level to the system level:

- Test cases may be executed on the real system (Figure 12). Running test cases on the real system for performance testing potentially gives the best results. However, this option may not always be available since it may be costly to run test cases with unpredictable outcomes on a real system. In such a case, it may be desirable to replicate the real system in a similar environment which may also be a costly operation.

- Test cases may be executed on a simulation environment using behavioral models for the applications (Figure 13). This path is less costly

Figure 12: Test Cases Run on System Implementation

albeit the quality of performance test results are highly dependent on how closely the system behavioral models capture the design of the system.

In either case mentioned above, there needs to be a way to make an assessment about the results of the test run. If performance requirements were clearly captured and each performance metric could be measured at the end of a test run, it might be possible to make pass/fail decision on the test run. However, the question is: is it desirable to merely verify performance, or in general non-functional requirements, in the same manner as functional requirements? One may argue that non-functional requirements testing phase in the development life cycle is more about observing, understanding how the system performs in different conditions, environments or with different system parameters. It is more valuable to be able to analyze test run results,

Figure 13: Test Cases Run on Simulation Engine

reason about the system performance, and identify relationship of system parameters with performance then to make a pass/fail decision. From this perspective, (performance) testing approaches (performance) engineering. In this sense, it is crucial to be able to feed the results of a test run back into design og the system, thus closing the loop. This does not necessarily mean to automatically feed a test run result back into the system. This feedback may be in the form of understanding more about the system and devising more and interesting test cases with variations in system parameters or system environment.

There is extensive literature on performance prediction from performance models (e.g. [21], [22], [23]) and those literature was investigated in [12]. However, the approach described here is not about predicting the performance of a system from performance models as outlined above. It is important to make the distinction between creating a performance model for a system and creating a system model and including a performance aspect. In the approach described here, in a typical model based development sense, behavioral and structural abstractions of a system are captured in a system model and this model is extended from performance point of view. Since it is also possible to generate series of test cases from this system model, it is possible to run the actual test cases either on the real system or in a simulation environment to reason about the actual performance of the system.

In order to get information about the performance of the system, a monitoring system is typically needed when this information cannot be obtained from the system during design time. A monitoring system is used to collect run-time information about a system [24]. Performance information of a system is a typical information that can be obtained during run-time. When the generated test cases are run on the actual system, obtaining performance results will rely on the monitoring system in place for the actual system. On the other hand, when the generated test cases are run on the simulated system, a performance monitoring component is needed. For the implementation of the approach, a performance monitor that collects performance information about the simulation system under test is explained in Chapter V.

A system designer has the knowledge about the internals of the system and how it should work. If one considers a designer who is designing a distributed middleware based system, it's safe to assume that she knows the structure of the system to be designed, the services the middleware is going to provide to the applications, how applications will use those services, and what type of complex interactions will take place between applications and the middleware services. The modeling approach described in this thesis gives the designer ability to capture her knowledge about the system she is designing in the form of models. When both the structure and behavior of the system is captured and either a simulation environment or parts of the real system is available, the designer can easily explore the behavior of the system and its effect on the performance of the system.

The approach enables the designer to easily create experiments, *Test Series Definitions*, and effortlessly generate test cases to exercise either the simulated or the real system. Since models also allow the designer to capture information about configuration parameters of system components, it is possible to observe how certain values of parameters in a certain system structure effects the performance of the system. Designer can then analyze the resulting data from the experiments, compare them to her performance goals. If the results are not satisfactory, she can turn back to the design and make changes to engineer the system to the needs of the design. Figure 14 shows the cycle that the system designer will typically go through for performance engineering the system.

Finally, an important note should be made about validating the simulation models that are used to make design decisions. One of the challenges mentioned in Section II of this chapter was about having previous versions of a system. The remark on that challenge was about determining a representative workload for the system. However, similar challenge also applies to having historical benchmark data about a system. If there is historical

Figure 14: Engineering Process

performance benchmarks for the system, results of performance tests can be compared against the benchmarks to catch invalid abstractions made in the simulation models. Results of a test run can be compared against trends of performance metrics with respect to changes in parameters whose impact on the system is well known. In addition, designer should always question the validity of results and should perform sanity checks to consider whether resulting data makes sense. Another aspect that needs to be considered is the validity of system behavior models. Performance test results depend on the DEVS behavior models. Those models are derived from functional requirements of the system. In order to have higher confidence in the validity of behavioral models, functional testing techniques [25] can be employed.

### Summary

In this chapter, a method for performance testing distributed middleware based systems were described. Several challenges including difficulty of creating many system configurations for a distributed middleware system were identified. As a possible solution to the challenges identified, a model based approach was described. Test Series Definition Modeling Language (TSDML) was presented in detail.

The approach described in this chapter focused on using modeling a system from performance perspective. It was pointed out that it was different from research that is focused on creating performance models for performance prediction. The modeling approach enabled the use of models during the system design cycle with an added perspective of performance testing. In addition to the TSDML, modeling behavior of the system using DEVS modeling formalism was presented. The connection between the TSDML and DEVS modeling layers were explained.

Finally, a brief discussion on performance engineering of a system was given. The discussion focused on clarifying that the goal of the approach is enable performance engineering of a system based on observations from experiments conducted on the system using TSDML and DEVS models.

# CHAPTER III

### BACKGROUND ON DEVS MODELING FORMALISM

Discrete Event System Specification (DEVS) is a modeling and analysis formalism for discrete event systems [8]. Modular and hierarchical modeling views are two important aspects in DEVS formalism. Modularity is achieved by input and output events whereas hierarchical aspect is realized by the coupling operation.

A DEVS system is formed of states, input and output events, a notion of time, and functions that describe how the system evolves with respect to input and output events.

There are two types of DEVS models. Atomic DEVS models enable a system to be modeled modularly by first creating models by simple fundamental dynamic behaviors. Coupled DEVS models enables the definition of the system hierarchically by coupling the atomic models to create a complete system specification. Mathematical definitions of those models will be given in the next sections.

### Atomic DEVS Models

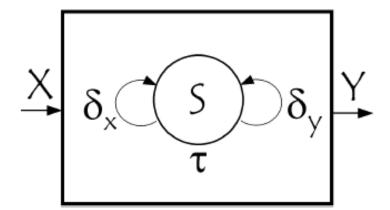

An atomic DEVS is a 7-tuple structure  $A = \langle X, Y, S, s_0, \tau, \delta_x, \delta y \rangle$  [2] where

• X is a set of *input events*.

Figure 15: Symmetric Structure of Atomic DEVS [2]

- Y is a set of *output events*.

- S is a set of *states*.

- $s_0 \in S$  is the initial state.

- τ; S → T is the time advance function where T = [0,∞] is the set of non-negative real numbers plus the transfinite number, infinity. This function is used to determine the lifespan of a state.

- $\delta_x : P \times X \to S \times \{0, 1\}$  is the *input transition function* where  $P = \{(s, t_s, t_e) | s \in S, t_s \in T, t_e \ in[0, t_s]\}$  represents the set of states. Times  $t_s$  and  $t_e$  are the lifespan of the state and the elapsed time since the last reset of  $t_e$ , respectively. The booelan result in the definition determines whether the elapsed time will be reset or not.

Figure 15 shows the structure of an atomic DEVS model. The symmetric nature of the DEVS model comes from the fact that input event set X and

input transition function  $(\delta_x)$ , and output event set Y, and output transition function  $(\delta y)$  are on the opposite sides of the structure [2].

There are two types of transitions in an atomic DEVS model: external and internal transitions. These transitions are the only ways a model can change its state. Internal transitions are time-based. That is, an internal transition occurs when the elapsed time reaches to the lifetime of the state which is defined by  $\tau(s)$ . An internal transition not only causes a state change but may also generate an output event. External transitions are event-based. That is, an external transition occurs when an input event arrives. An input event causes a state change when the conditions given by  $\delta_x$  is satisfied. External transitions are instantaneous and only trigger state change and do not generate an output event.

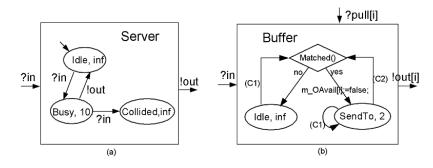

Figure 16 shows two atomic models called Server and Buffer. In the figure, ?in, and *out* correspond to input and output of the Server atomic model, whereas *in*, *pull*[*i*] are inputs and *out* is the output of the Buffer atomic model. *Idle*, *Busy* and *Collided* are the states of the Server atomic model. On the other hand, the states of the Buffer atomic model are *Idle*, *Matched* and *SendTo*. There are also several input and output transitions functions. For example, Server changes its state from *Idle* to *Busy* when *in* is received and stays in the *Busy* state for 10 seconds since the lifespan of the state is denoted as 10 in the figure. Different than the Server, Buffer atomic model can accept two different inputs, *in* and *pull*[*i*]. The difference

Figure 16: Atomic DEVS Models [2]

between these inputs will be evident shortly when the Coupled DEVS model is explained.

# **Coupled DEVS Models**

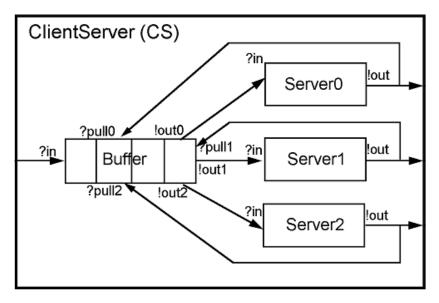

A coupled DEVS is also a 7-tuple structure [2]  $N = \langle X, Y, D, \{M_i\}, EIC, ITC, EOC \rangle$  where

- X is a set of input events

- Y is a set of output events

- *D* is a set of names of subcomponents

- $\{M_i\}$  is a set of DEVS models where  $i \in D$ .  $M_i$  can be either atomic DEVS model or a coupled DEVS model

- $EIC \subseteq X \times \bigcup_{i \in D} X_i$  is a set of external input couplings where  $X_i$  is the set of input events of Mi.

Figure 17: A Coupled DEVS Model [2]

- $ITC \subseteq \bigcup_{i \in D} Y_i \times \bigcup_{i \in D} X_i$  is a set of internal couplings where  $Y_i$  is the set of output events of  $M_i$ .

- $EOC \subseteq \bigcup_{i \in D} Y_i \times Y$  is a set of external couplings.

A coupled DEVS model defines the subsystems that are contained by the model and how there are connected to each other. Coupled DEVS models realize the modular and hierarchical aspect of the DEVS formalism by enabling a system designer to build a larger system by designing and connecting simpler subsystems. Although it is not impossible to create a complete system only with atomic models, it is very tedious and error prone. Coupled DEVS model eliminates this complexity and lets subsystems be composed together and connected to each other enabling a better system specification. Figure 17 shows a coupled DEVS model [2]. It's part of a Client-Server system. The configuration in Figure 17 is for 3 servers. A buffer is present to hold requests from clients and coordinate allocation of clients on to the servers. As mentioned in the previous section, Buffer can accept to inputs denoted by ?in and ?pull. The in input comes from a client whose model is not shown here. The pull inputs come from servers and are indexed by the server in the form of pull[i]. Since this is a coupled system, outputs out1, out2 and out3 from the Buffer is fed into the input ports of the corresponding Server. Similarly, output of each Server becomes the pull[i] input for the Buffer.

Since the resulting DEVS model is modular and hierarchical, events generated within a subsystems can propagate through other parts of the subsystem horizontally, or through other subsystems vertically within the hierarchy of the system through well defined interfaces.

### Summary

DEVS formalism provides the means to describe discrete event systems and provides constructs like time, events, states and transitions as well as composition of models. In this research, DEVS was chosen to be used to model a distributed data acquisition system from simple atomic models of system components along with domain specific models. Event-based nature of the data acquisition system made DEVS the proper tool to model its middleware and applications using the DEVS modeling formalism. The Open DEVS simulation framework [2] provides suitable ground work to model applications as DEVS models and simulate the complete system.

# CHAPTER IV

# BACKGROUND ON CMS DAQ SYSTEM

The Compact Muon Solenoid (CMS) experiment is a particle physics detector built on the proton-proton Large Hadron Collider (LHC) being built at CERN in Switzerland. One of the goals of CMS is to discover the Higgs boson. CMS is designed as a general-purpose detector and is going to be capable of studying results of proton collusions to take place inside the LHC.

An experiment at a hadron collider requires a sophisticated trigger and data acquisition (DAQ) system because of very high collision and overall data rates. The frequency of protons crossing each other at the LHC is 40 MHz [26].

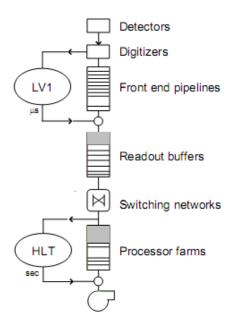

The main goal of the CMS Trigger and Data Acquisition System (TriDAS) is to inspect the detector information arriving at 40 MHz frequency and to select events and to store them for offline processing. The events are selected at the maximum rate of  $O(10^2)$ . There are two steps in the functionality of the system. The first step, which is called the Level-1 Trigger [26], is designed to reduce the rate of events selected for offline processing to less than 100 kHz. The second step, which is called High-Level Trigger (HLT), is designed to further reduce the 100 kHz. of the Level-1 Trigger to the final output rate of 100 Hz.

Functionality of the CMS DAQ and HLT is given in the CMS DAQ Technical Design Report as follows [26]:

Figure 18: Data Flow in the Trigger/DAQ System

- "perform the readout of the front-end electronics after a Level-1 Trigger accept"

- "execute physics selection algorithms on the events read out, in order to accept the ones with the most interesting physics content"

- "forward these accepted events, as well as a small sample of rejected events, to the online services which monitor the performance of the CMS detector and also provide the means of archiving the events in mass storage"

Figure 18 shows the data flow in the Trigger/DAQ system and also visualizes the Level-1 Trigger and HLT stages mentioned above.

# **DAQ** Architecture

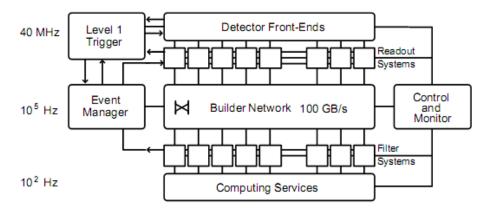

Figure 19 shows the architecture of the CMS DAQ system. The system consists of the following elements:

- **Detector Front-ends** are the components that are connected to the front-end electronics to store the data from them as the Level-1 Trigger accept signal is received.

- Readout Systems are the components that are connected to the Front-End System (FES) to read the data from the detector. Readout systems store the data until they are sent to the processor to which will analyze the event. There are about 500 components which are called "Readout Columns". Each Readout Column consists of a number of Front-End Drivers (FEDs) and one Readout Unit (RU). RU is responsible for keeping the event data in its buffer and interfacing to the switch.

- Builder Network is a collection of networks providing the interconnections between the Readout and Filter Systems. It can handle 800Gb/s sustained throughput to the Filter Systems.

- Filter Systems are the processors that the RUs provide the events with. Filter systems are the entities that decide whether a supplied event is interesting and will be kept for offline processing or not. The interestingness of an event is determined by executing the High-Level

Figure 19: CMS DAQ System Architecture

Trigger algorithms. There are about 500 entities which are called "Filter Columns". Each of those include one Builder Unit (BU). A BU is responsible for receiving incoming data fragments that correspond to a single event and building them into full event buffers.

- Event Manager controls the flow of events in the system. Event Manager (EVM) serves as a centralized intelligence of event management.

- **Computing Services** are composed of all the processors and networks that receive filtered events and some of the rejected events from the Filter Farms.

- **Controls** are responsible for the user interface and the configuration and monitoring of the DAQ.

Given the component breakdown of the system it is possible to identify four stages of system functionally. The first stage is a detector readout stage where events are collected and stored in buffers. The second stage is the event building stage, where all data corresponding to a single event are collected from the buffers. The third stage is the selection stage where High-Level Trigger in the processor processes the event. The final stage is the analysis and storage stage where the events that are selected in the previous stage are sent to the Computing Services for additional processing for storage or further analysis.

XDAQ uses a format called I20 data binary data format. I2O (Intelligent Input Output) is an I/O architecture specification developed by a consortium of computer companies called the I2O special Interest Group (SIG) for managing devices. The details of the I2O message format is not in the scope of this research. However, more information about the details of the I2O specification may be obtained from [27].

### Event Builder

The main task of the DAQ system is to read each event's corresponding data out of the FEDs and merge it into the single structure called "physics event" and to transmit the physics event to a filter farm consisting of processor that execute physics algorithms that decide whether the event should be kept for further processing or discarded [26]. The Event Builder (EVB) is the central component of the DAQ system and includes the components that are responsible for this task.

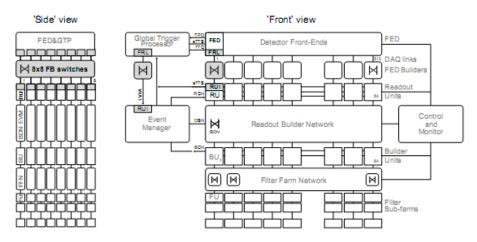

Figure 20: Front and Side Views of the DAQ

Figure 20 shows a more detailed version of the DAQ architecture depicted in Figure 19.

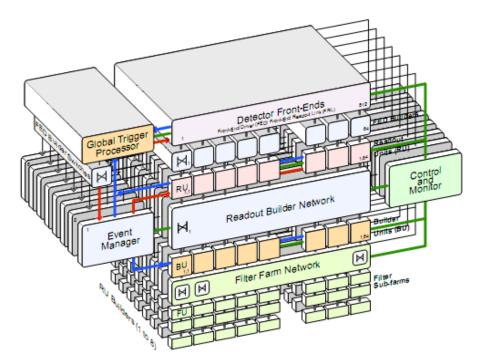

In the first of the stages that were idenfied above, there exist 8 FEDs that the RUs read data from and perform merging of event data fragments into larger data blocks called "super-fragments" or "s-fragments". This arrangement makes up a 64 "FED Builders" each of which consists of 8 FEDs, a 8x8 switch, and 8 RUs. Readout data is distributed among 64 RUs to maximize readout bandwidth. Thus, parts of data from a single event are buffered in 64 RUs. In the second state, 64 BUs which read out the data from a single event contained in 64 RUs and build these 64 s-fragments to form a single event. RUs and BUs are connected to each other through a 64x64 switch. The group of 64 RUs, the 64x64 switch and 64 BUs are called the "RU Builder". The full XDAQ system is composed of 64 FED Builders

Figure 21: Three-Dimensional View of the System

and 8 RU Builders. Figure 21 shows the three-dimensional representation of the system [26].

### <u>RU Builder</u>

This research is mainly interested in the components of the RU Builder as the experimental platform. Figure 27 shows the event builder and how the RU Builder is connected to the rest of the system [28].