# **RELIABILITY ISSUES IN GERMANIUM AND SILICON**

# **CARBIDE MOS DEVICES**

By

Rajan Arora

Thesis

Submitted to the Faculty of the

Graduate school of Vanderbilt University

in partial fulfillment of the requirements

For the degree of

### MASTER OF SCIENCE

in

**Electrical Engineering**

August, 2009

Nashville, Tennessee

Approved by:

Professor Ronald D. Schrimpf

Professor Daniel M. Fleetwood

© Copyright by Rajan Arora 2009

All Rights Reserved

To My Mother & Sisters

who always stood by me in good and bad times

#### ACKNOWLEDGEMENTS

I would first of all like to thank Prof. Ron Schrimpf for showing faith in my abilities throughout my stay at Vanderbilt. His research thought process, teaching and presentation skills always influenced me.

I would also like to thank Prof. Dan Fleetwood for his useful comments and support for my research. His immense experimental and physical knowledge always helped me in my work.

I would like to thank Dean Ken Galloway for his support and encouragement during the course of this work and the professors who helped me create strong basics in mathematics, physics, and engineering.

I thank collaborators at NCSU, IMEC and Griffith University for the success of this work. I thank AFOSR and Vanderbilt School of Engineering for providing the funds for this work.

I would like to thank all the friends I had starting from primary school to graduate school. Chetan, Aditya, Deepti, Shweta, Tripti, Tina, Aparna, Puja, Saumitra, Sameer, Sriram, Farah, Kulkarni, Bo, John, Nikkon, Srikanth, Vishwa, Tania, David, Nadia, Daniel, Jon, Ashley, Jonny, Hyunwoo, Sandeepan, Megan, Andrew, Wole, Rishab, Ankur, Nitin, Abhishek, Mayur, Rahul, Anuj, Gaurav, Sumit, Rohit, Rachita, Lovina, Malvika for their friendship.

Last but not least I thank my sisters (Prerna, Vaishali, Puja, Manjari), my mother (Mrs. Raj Arora), my brother-in-laws (Sanjay, Rajiv, Vishal), and my nieces and nephews (Aparna, Alisha, Daksh, Shreyas) for everything they have done for me.

iv

# **TABLE OF CONTENTS**

| Р                                                                                                                                   | age  |

|-------------------------------------------------------------------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                                                                                    | iv   |

| LIST OF FIGURES                                                                                                                     | i-xi |

| I. ALTERNATIVE SUBSTRATE MOS DEVICES                                                                                                | 1    |

| I) INTRODUCTION                                                                                                                     | 1    |

| II) HIGH-κ DIELECTRICS                                                                                                              | 5    |

| III) ALTERNATIVE SUBSTRATE MOSFETS                                                                                                  | 7    |

| A) Ge p-MOSFETs                                                                                                                     | 7    |

| B) III-V n-MOSFETs                                                                                                                  | 8    |

| IV) SIC POWER MOS DEVICES                                                                                                           | 9    |

| A) Polytypes of SiC                                                                                                                 | 10   |

| B) Properties of nitrided oxides on SiC                                                                                             | 11   |

| C) SiC/SiO <sub>2</sub> interface trap spectrum                                                                                     | 13   |

| v) Conclusions                                                                                                                      | 15   |

| II. BASICS OF TOTAL DOSE RADIATION AND BIAS TEMPERATURE                                                                             |      |

| INSTABILITY                                                                                                                         |      |

| <ul> <li>I) RADIATION DAMAGE.</li> <li>A) Experimental setup for x-ray radiation.</li> </ul>                                        |      |

| <i>B)</i> Optimum lab source for radiation testing                                                                                  |      |

| C) Total dose effects on MOS devices                                                                                                |      |

| <i>D)</i> Total dose radiation in high- $\kappa$ dielectric MOS devices                                                             |      |

| <ul> <li>I) Iolal abservation in high-k alelectric MOS devices</li> <li>II) NEGATIVE BIAS TEMPERATURE INSTABILITY (NBTI)</li> </ul> |      |

| <i>A)</i> What is NBTI?                                                                                                             |      |

| B) NBTI models                                                                                                                      |      |

| C) Interface traps and oxide charges                                                                                                |      |

|                                                                                                                                     | 27   |

| <b>III.RADIATION EFFECTS ON GERMANIUM P-MOSFETS-PART I:</b>                                                                         |      |

| BASIC MECHANISMS                                                                                                                    |      |

| I) EXPERIMENTAL DETAILS                                                                                                             |      |

| II) EFFECT OF RADIATION ON DRAIN-SUBSTRATE JUNCTION LEAKAGE                                                                         | 37   |

| III) MECHANISMS THAT CAUSE THE INCREASE IN JUNCTION LEAKAGE WITH                                                                    | 40   |

| RADIATION                                                                                                                           |      |

| IV) CONCLUSION                                                                                                                      | 43   |

| IV. RADIATION EFFECTS ON GERMANIUM P-MOSFETS-PART II:<br>UNDERSTANDING EFFECT OF VARIATION IN HALO DOPING                           |      |

| AND SI MONOLAYER THICKNESS ON TOTAL-DOSE RESPONSE                                                                                   |      |

| OF GE P-MOSFETS                                                                                                                     | 47   |

| I) DEVICE AND EXPERIMENTAL DETAILS                                                                                                  |      |

| II)         | EXPERIMENTAL RESULTS                         | 50 |

|-------------|----------------------------------------------|----|

| III)        | Mechanisms                                   |    |

| IV)         | CONCLUSION                                   |    |

| <b>V.</b> Т | EMPERATURE STRESS RESPONSE OF GERMANIUM MOS  |    |

| С           | CAPACITORS WITH HFO2/HFSION GATE DIELECTRICS | 57 |

| I)          | INTRODUCTION                                 | 57 |

| II)         | Experimental details                         | 58 |

| III)        | ELECTRICAL CHARACTERIZATION RESULTS          |    |

| IV)         | XPS ANALYSIS                                 |    |

| V)          | CONCLUSIONS                                  |    |

| VI.C        | HARGE TRAPPING PROPERTIES OF SIC MOS         |    |

| I)          | DEVICE AND EXPERIMENTAL DETAILS              | 77 |

| II)         | RESULTS AND DISCUSSION                       |    |

| III)        | CONCLUSION                                   |    |

| ,           |                                              |    |

|             |                                              |    |

| CONCLUSIONS | 37 |

|-------------|----|

|-------------|----|

# APPENDIX: CHARACTERIZATION TECHNIQUES USED IN THIS

| WORK                                                     |  |

|----------------------------------------------------------|--|

| I) CONDUCTANCE METHOD                                    |  |

| A) Theory and Evaluation:                                |  |

| B) Experimental data:                                    |  |

| (C) Conductance code used for measurements in this work: |  |

| II) CHARGE PUMPING (CP) METHOD                           |  |

| A) Square Pulse-Interface trap density                   |  |

| B) Charge pump code used (frequency variation code):     |  |

| III) MOSFET ID-VG MEASUREMENT CODE                       |  |

| ,<br>,                                                   |  |

| REFERENCES                                               |  |

# LIST OF FIGURES

| Figure Page                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

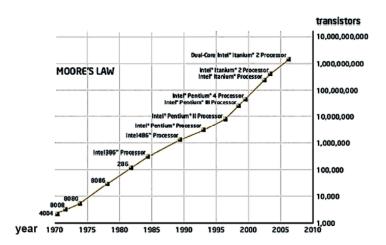

| Fig. 1.1. Illustration of Moore's law: Doubling of number of components on a chip roughly every two years [1]                                                                                                                                                                                                                |

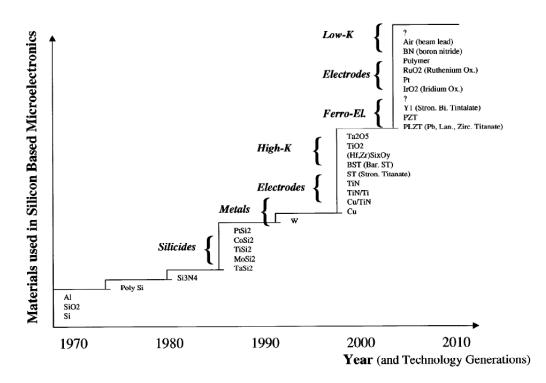

| Fig. 1.2. Quantum leap in new materials [4]. Innovations have been tried in almost every material used in fabrication of MOSFETs                                                                                                                                                                                             |

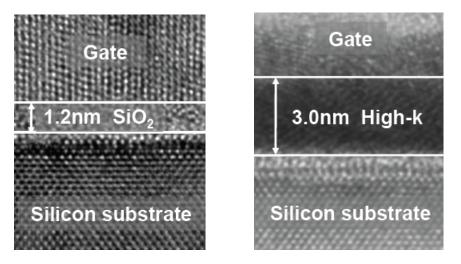

| <ul><li>Fig. 1.3. Traditional MOS with Gate, SiO<sub>2</sub> as gate dielectric, and silicon substrate.</li><li>b) MOS with high-κ as gate dielectric. (image courtesy of Intel Corp.)</li></ul>                                                                                                                             |

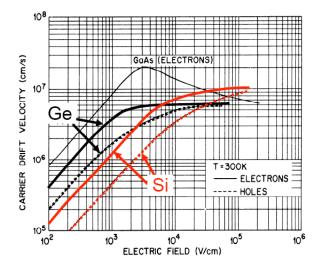

| Fig. 1.4. Comparison of carrier drift velocity of Si, Ge and GaAs [9]                                                                                                                                                                                                                                                        |

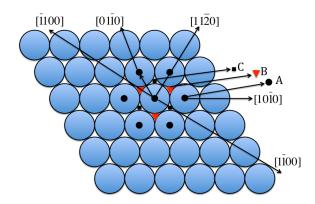

| Fig. 1.5. A closed-packed hexagonal plane of spheres with centers at points marked A.<br>A second and identical plane can be placed atop the first plane, with centers<br>over either the points marked B or the points marked C                                                                                             |

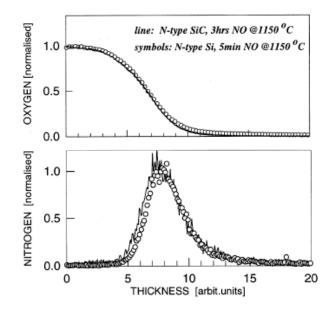

| Fig. 1.6. Normalized SIMS profiles of oxygen (top) and nitrogen (bottom) in nitrided oxides on Si (symbols) and SiC (lines). The nitrogen peak shape and position are the same relative to the oxygen profiles [28]                                                                                                          |

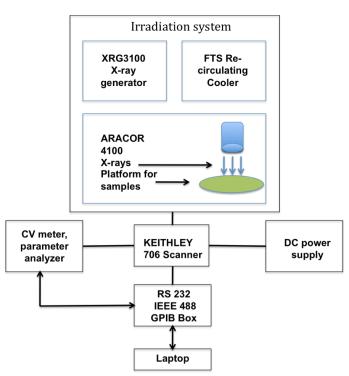

| Fig. 2.1. Experimental setup for x-ray radiation using ARACOR and device charact-<br>erization                                                                                                                                                                                                                               |

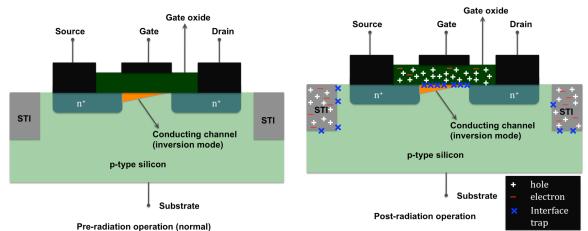

| Fig. 2.2. Schematic of n-channel MOSFET illustrating radiation induced charging of the gate oxide: a) normal operation and b) post-irradiation operation                                                                                                                                                                     |

| Fig. 2.3. Schematic energy band diagram for MOS structure, indicating major physical processes underlying radiation response                                                                                                                                                                                                 |

| Fig. 2.4. a) $I_d$ - $V_g$ characteristics showing stretch-out and mobility degradation with radiation. b) Sub-threshold $I_d$ - $V_g$ characteristics showing increase in leakage current with radiation                                                                                                                    |

| Fig. 2.5. Mobility degradation of a MOSFET as a function of radiation dose24                                                                                                                                                                                                                                                 |

| Fig. 2.6. Structural model of the (a): (111)Si surface and (b): (100)Si surface [57]27                                                                                                                                                                                                                                       |

| <ul> <li>Fig. 2.7. Band diagrams of the Si substrate of a p-channel MOS device showing the occupancy of interface traps and the various charge polarities for a p-substrate with (a) negative interface trap charge at flatband and (b) positive interface trap charge at inversion. Each of the small horizontal</li> </ul> |

| lines represents an interface trap. It is either occupied by an electron (solid circle) or occupied by a hole (unoccupied by an electron), shown by the lines                 | 29  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 3.1. TEM cross-section of the Ge p-MOSFET gate oxide-semiconductor interface                                                                                             | .35 |

| Fig. 3.2 shows the representation of the germanium –gate oxide interface                                                                                                      | 35  |

| Fig. 3.3. TEM cross-section of a 65 nm Ge p-MOSFET                                                                                                                            | 36  |

| Fig. 3.4. Schematic cross-section of the Ge p-MOSFET                                                                                                                          | 36  |

| Fig. 3.5. SEM cross-section of the contact pads of a MOSFET                                                                                                                   | 37  |

| Fig. 3.6. Prerad and post 3 Mrad(SiO <sub>2</sub> ) <i>I<sub>s</sub>-V<sub>d</sub></i> characteristics for <i>W/L</i> =9.8μm/10μm device                                      | .38 |

| Fig. 3.7. Prerad and post-irradiation gate current characteristics                                                                                                            | .39 |

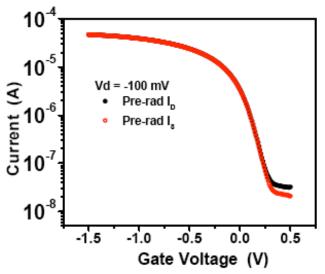

| Fig. 3.8. Prerad $I_s/I_d$ - $V_g$ characteristics                                                                                                                            | 40  |

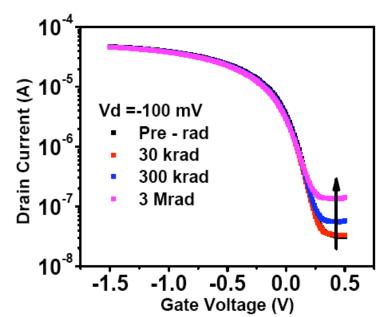

| Fig. 3.9. Prerad and till 3 Mrad(SiO <sub>2</sub> ) $I_d$ - $V_g$ characteristics                                                                                             | .41 |

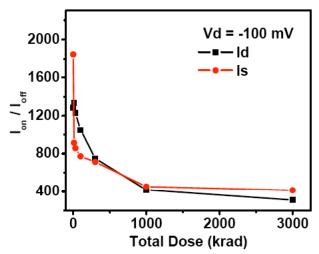

| Fig. 3.10. <i>I<sub>on</sub>/I<sub>off</sub></i> current ratio with x-ray total dose                                                                                          | .41 |

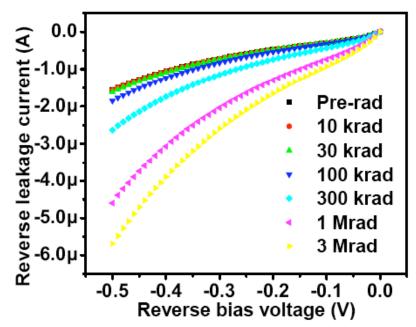

| Fig. 3.11. Reverse bias leakage current for a diode with $P/A = 400/\text{cm}$                                                                                                | .44 |

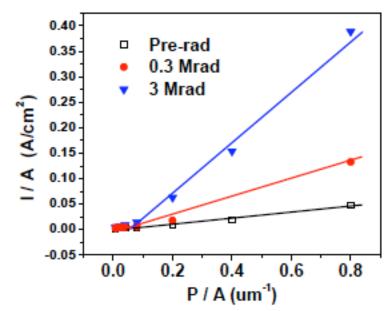

| Fig. 3.12. Current density per unit area ( <i>I/A</i> ) as a function of perimeter to area ratio $(P/A)$ at $V_R = 100$ mV for a set of different geometry diodes             | .44 |

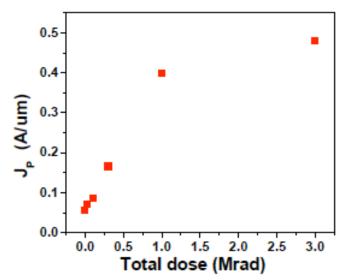

| Fig. 3.13. Peripheral current density $(J_P)$ as a function of dose for a set of diodes with different geometries                                                             | 45  |

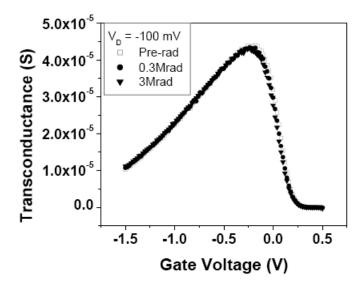

| Fig. 3.14. Transconductance as a function of gate voltage ( $V_G$ ) for an irradiated pMOSFET with $W/L = 9.8 \mu m/10 \mu m$                                                 | .45 |

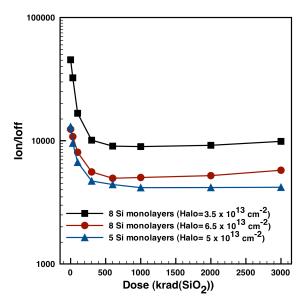

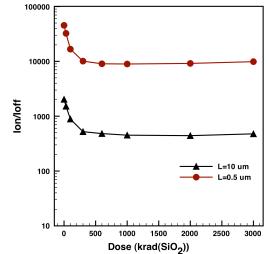

| Fig. 4.1. $I_{on}/I_{off}$ characteristics for the three devices for varying x-ray dose (in units of krad(SiO <sub>2</sub> )). All three devices have $W/L=9.8\mu m/0.5\mu m$ | 51  |

| Fig. 4.2. $I_{on}/I_{off}$ characteristics for long (10 µm) and short (0.5 µm) channel length device for varying x-ray dose (in units of krad(SiO <sub>2</sub> ))             | .51 |

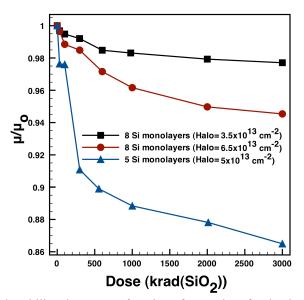

| Fig. 4.3. Normalized mobility change as a function of x-ray dose for the three devices. All three devices have <i>W/L</i> =9.8μm/0.5μm                                        | .52 |

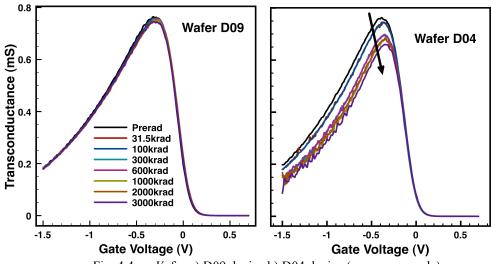

| Fig. 4.4 $g_m$ - $V_g$ for a) D09 device b) D04 device (axes-same scale)                                                                                                      | .53 |

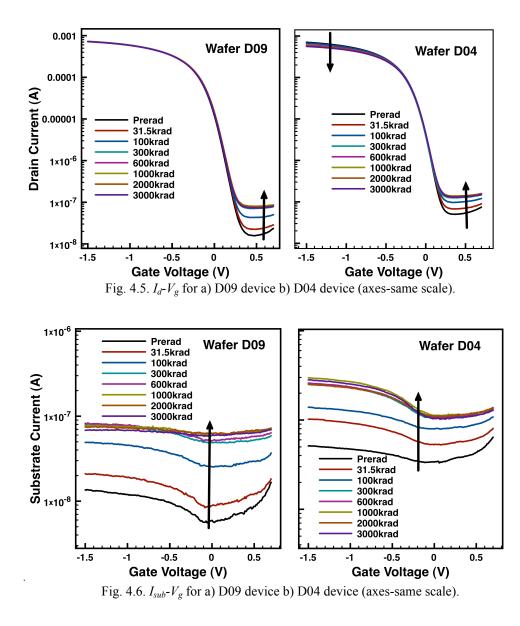

| Fig. 4.5. $I_d$ - $V_g$ for a) D09 device b) D04 device (axes-same scale)                                                                                                                                                                                                           | 1 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Fig. 4.6. $I_{sub}$ - $V_g$ for a) D09 device b) D04 device (axes-same scale)                                                                                                                                                                                                       | 4 |

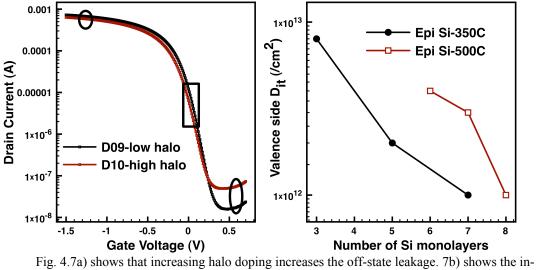

| <ul><li>Fig. 4.7. a) shows that increasing halo doping increases the off-state leakage.</li><li>b) shows the interface trap density of the device for varying number of Si monolayers</li></ul>                                                                                     | 5 |

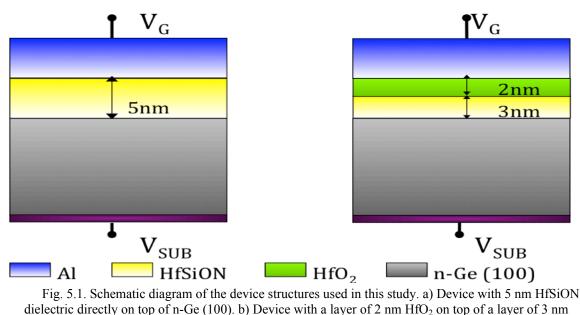

| <ul> <li>Fig. 5.1. Schematics of the device structures used in this study. a) Device with 5 nm HfSiON dielectric directly on top of n-Ge (100). b) Device with a layer of 2 nm HfO<sub>2</sub> on top of a layer of 3 nm HfSiON on n-Ge (100)</li></ul>                             | 9 |

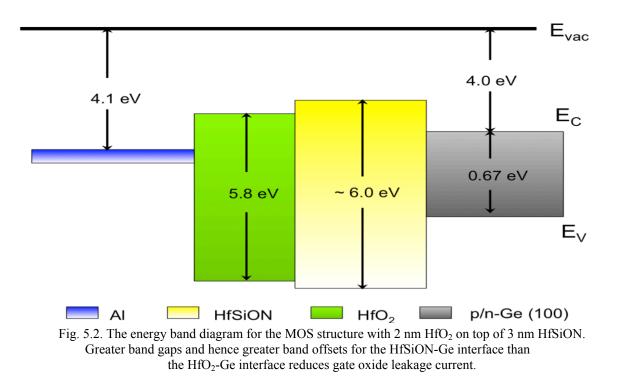

| Fig. 5.2. The energy band diagram for the MOS structure with 2 nm HfO <sub>2</sub> on top of 3 nm HfSiON. Greater band gap and hence greater band offsets for HfSiON-Ge interface than HfO <sub>2</sub> -Ge interface reduces gate oxide leakage current                            | C |

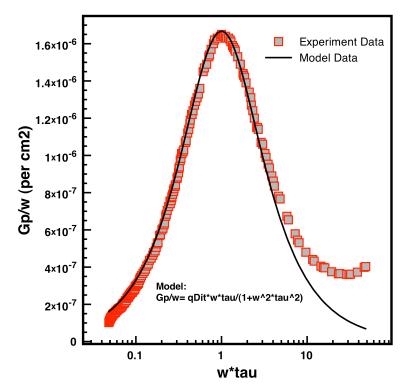

| Fig. 5.3. Showing good correlation between the analytical model for single level interface trap and experimental data                                                                                                                                                               | 1 |

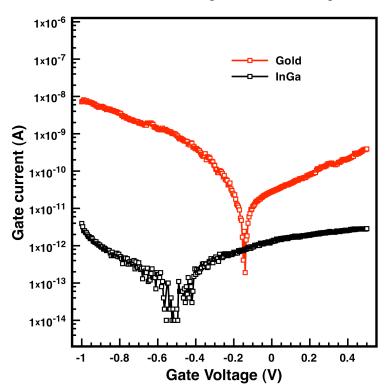

| Fig. 5.4. Gate current $(I_g)$ -gate voltage $(V_g)$ characteristics for n-Ge MOS for Gold<br>and eutectic InGa as back side contact                                                                                                                                                | 2 |

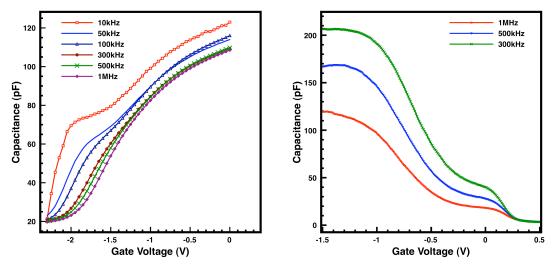

| Fig. 5.5. a) Capacitance-voltage curves showing the frequency dispersion for n-Ge substrate capacitors with HfSiON dielectrics. 5b) Capacitance-voltage characteristics for p-Ge MOS capacitors with HfSiON dielectrics. Greater frequency dispersion is observed than for the n-Ge | 3 |

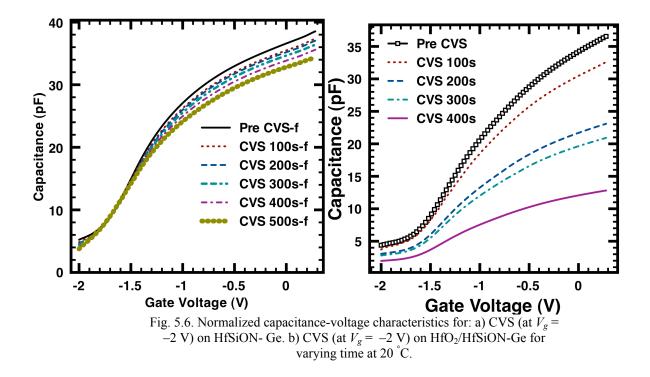

| Fig. 5.6. Normalized capacitance-voltage characteristics for: a) CVS (at $V_g = -2$ V)<br>on HfSiON- Ge. b) CVS (at $V_g = -2$ V) on HfO <sub>2</sub> /HfSiON-Ge for varying<br>time at 20 °C                                                                                       | 4 |

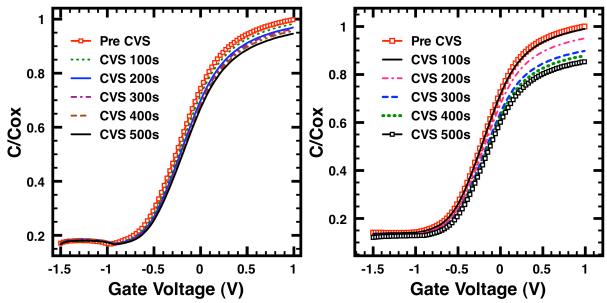

| Fig. 5.7. Normalized capacitance-voltage characteristics for: a) CVS (at –2 V) on HfSiON-Si; b) CVS (at –2 V) on HfO <sub>2</sub> /HfSiON-Si for varying time65                                                                                                                     | 5 |

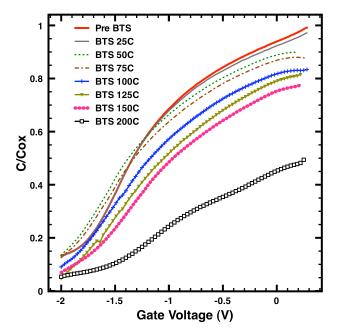

| Fig. 5.8. Normalized capacitance-voltage characteristics of HfSiON-Ge for BTS with varying temperatures (100s at each temperature)                                                                                                                                                  | 6 |

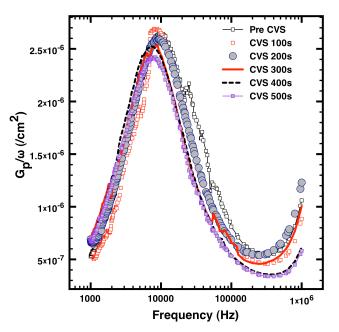

| Fig. 5.9. Conductance curves as functions of frequency for varying CVS time. The peak of the conductance curves decreases with CVS                                                                                                                                                  | 7 |

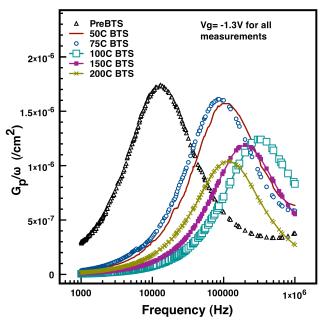

| Fig. 5.10. Conductance curves for HfSiON-Ge samples for varying temperature stress67                                                                                                                                                                                                | 7 |

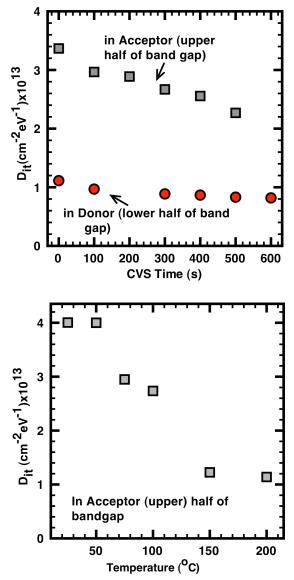

| Fig. 5.11. $D_{it}$ as a function of: a) CVS time and b) temperature ( $V_g = -2$ V) for                                                                                                                                                                                            |   |

| HfSiON- Ge MOS capacitors (100 s at each temperature)                                                                                                                                                                                                                     | 69 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

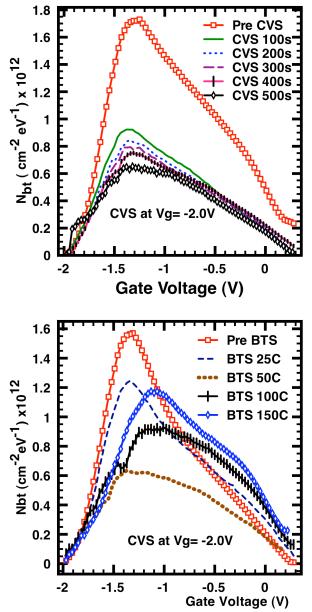

| Fig. 5.12. Border trap $(N_{bt})$ density for a) different CVS time (HfSiON- Ge) and b) varying BTS temperature (HfSiON- Ge)                                                                                                                                              | 70 |

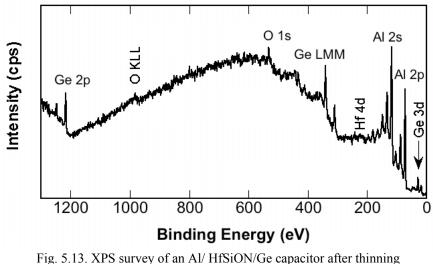

| Fig. 5.13. XPS survey of an Al/ HfSiON/Ge capacitor after thinning the electrode with argon sputtering                                                                                                                                                                    | 72 |

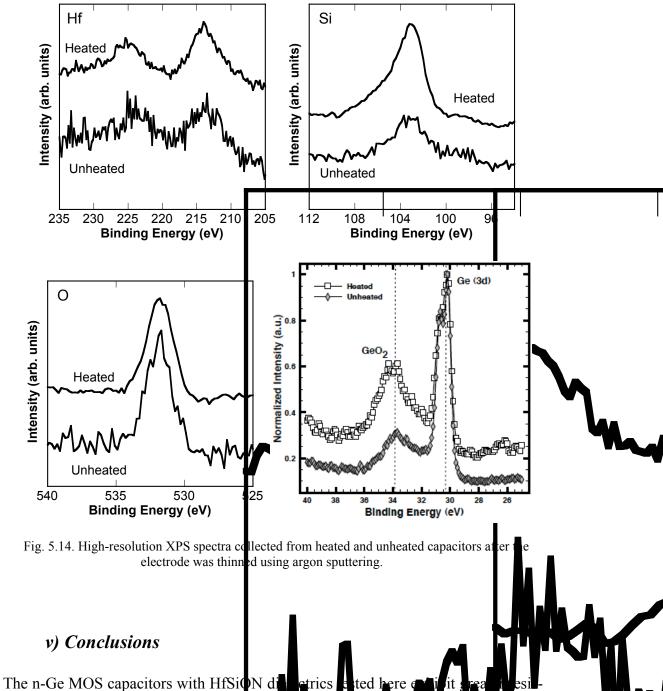

| Fig. 5.14. High-resolution XPS spectra collected from heated and unheated capacitors after the electrode was thinned using argon sputtering                                                                                                                               | 74 |

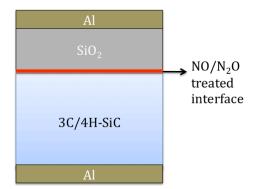

| Fig. 6.1. Schematic of the MOS capacitor used in this study                                                                                                                                                                                                               | 78 |

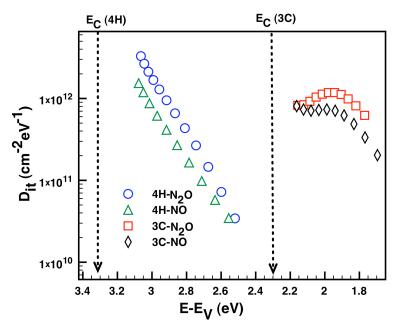

| Fig. 6.2. Interface trap density, <i>D<sub>it</sub></i> , as a function of energy for 4H- and 3C-SiC samples                                                                                                                                                              | 79 |

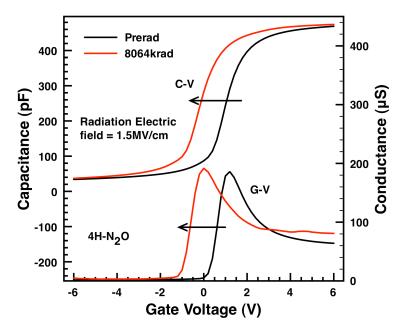

| Fig. 6.3. Capacitance/conductance-voltage characteristics for 4H-SiC MOS with N <sub>2</sub> O treatment                                                                                                                                                                  | 79 |

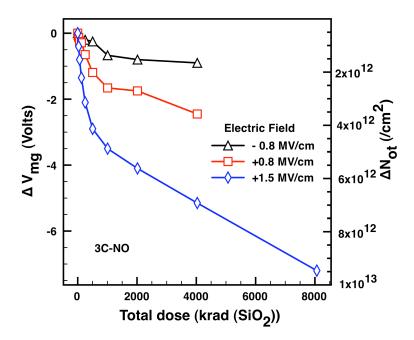

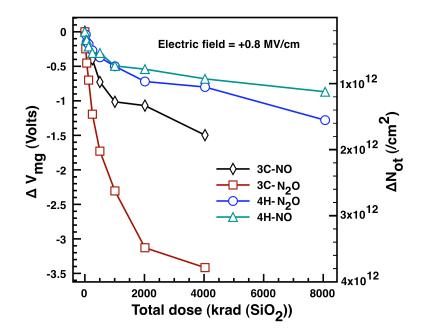

| Fig. 6.4. Shift in midgap voltage as a function of x-ray dose for 3C-SiC MOS with NO treated oxide                                                                                                                                                                        | 81 |

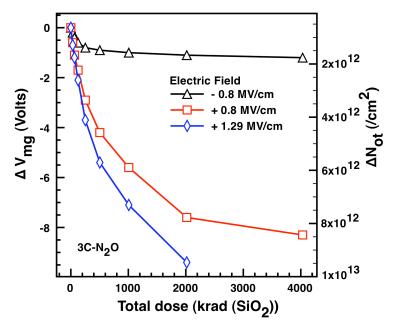

| Fig. 6.5. Shift in midgap voltage as a function of x-ray dose for 3C-SiC MOS with N <sub>2</sub> O treated oxide                                                                                                                                                          | 81 |

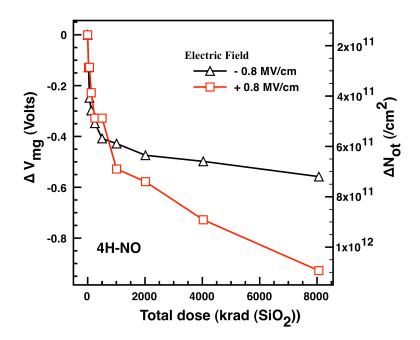

| Fig. 6.6. Midgap voltage shift as a function of x-ray dose for 4H-SiC MOS with NO treated oxide                                                                                                                                                                           | 82 |

| Fig. 6.7. Normalized midgap voltage shift comparison for a 4H-/3C-SiC MOS sample                                                                                                                                                                                          | 84 |

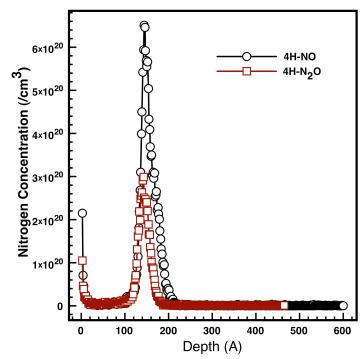

| Fig. 6.8. Nitrogen concentration as a function of depth for 4H MOS capacitors with NO and N <sub>2</sub> O nitridation                                                                                                                                                    | 85 |

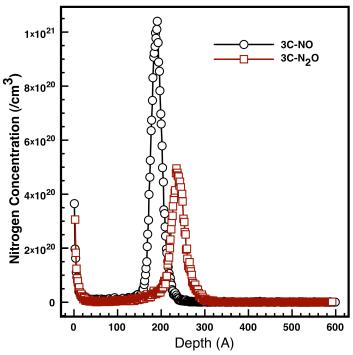

| Fig. 6.9. Nitrogen concentration as a function of depth for 3C MOS capacitors with NO and N <sub>2</sub> O nitridation                                                                                                                                                    | 85 |

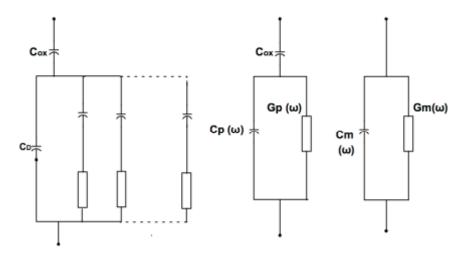

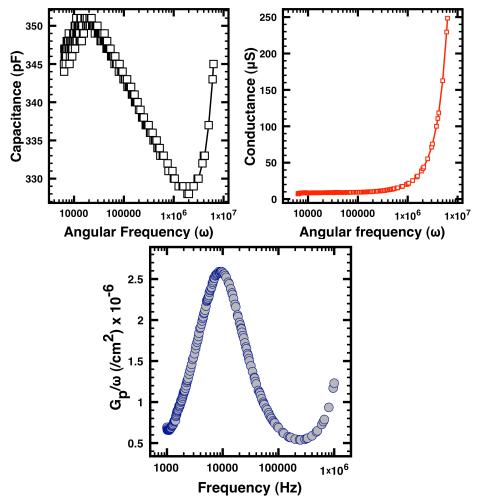

| Fig. A.1. MOS equivalent circuit                                                                                                                                                                                                                                          | 92 |

| Fig. A.2. a). Capacitance-angular frequency $(C-\omega)$ characteristics for a Ge MOS capacitor. b) Conductance-angular frequency $(G-\omega)$ characteristic for same sample. c) Equivalent parallel conductance divided by angular frequency as a function of frequency | 93 |

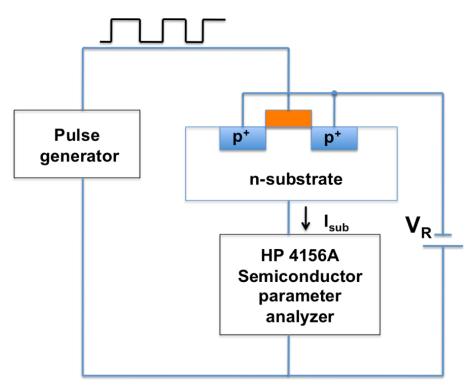

| Fig. A.3. Circuit diagram used in charge pump measurement                                                                                                                                                                                                                 | 97 |

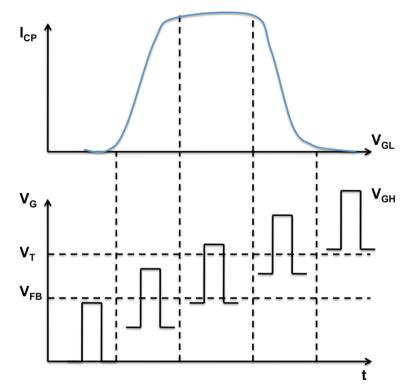

| Fig. A.4. | Schematic illustration of a square-pulse charge pump method applied |    |

|-----------|---------------------------------------------------------------------|----|

|           | to a n-MOSFET                                                       | 98 |

# **CHAPTER I**

# ALTERNATIVE SUBSTRATE MOS DEVICES

### i) Introduction

Silicon has been the material of choice for commercial MOS devices for four decades because it has excellent material and electrical properties. To improve device performance the channel length and gate oxide thickness have been historically scaled down starting from a channel length of a few micrometers to the present day's 45 nm technology node. For decades now technology scaling has allowed ever improving computing performance. MOSFET scaling has allowed an increasing number of components on an integrated circuit (IC) as seen in Fig. 1.1 for the years since 1970 [1]. The scaling of the MOSFET has allowed increased functionality per unit chip-area, reduced cost per functionality, increased performance, and reduced device-switching power. Better gate control was achieved in short channel MOSFETs by decreasing the gate oxide thickness. Gate oxide thicknesses have been scaled from a few hundred nanometers to less than one nm during this process. For future device performance improvement it is no longer possible to scale the gate oxide thickness, as the oxide thickness has reached limits where the gate tunneling current becomes too high.

The properties of silicon dioxide have been key to the success of the CMOS industry due to the high electrical quality of the  $Si/SiO_2$  interface, its favorable material properties and reliability. Dielectric materials with a higher- $\kappa$  (relative dielectric constant) value maintain channel control for larger thicknesses and improve drive current. The introduc-

tion of high- $\kappa$  gate dielectrics along with metal gate technology, which resolved the gate leakage issue in 45 nm MOSFETs [2], is deemed one of the largest innovations in CMOS technology since the introduction of the poly gate, or even the invention of the MOS integrated circuit itself. Several other technological features have been included in production MOSFETs recently to propel CMOS along the roadmap, such as lowering the  $\kappa$ -value of interconnect dielectrics to reduce interconnect delay, advanced channel strain techniques to boost performance, and numerous other innovations.

However, high- $\kappa$  materials may result in degraded carrier mobility in the inversion layer. Therefore, new materials are being looked at as alternative substrate materials for MOS devices. Among them, germanium and III-V substrates (such as GaAs, InGaAs, etc.) are the most important ones. These materials provide higher carrier (electron and hole) mobilities. However, there are many problems associated with fabrication of MOS-FETS on these materials such as the absence of a stable native oxide, intrinsic defects present in the material or finding appropriate dopants. Making MOSFETs on these materials that can meet the on and off current specs described in the ITRS roadmap is an area of active research [3].

Fig. 1.1. Illustration of Moore's law: Doubling of number of components on a chip roughly every two years [1].

Fig. 1.2 shows both the history and prospects of candidate materials that are/may-be used in integrated circuit (IC) processes [4]. As shown in the figure, the basic MOS process started with aluminum (Al) as the gate metal, silicon dioxide (SiO<sub>2</sub>) as the gate dielectric, and silicon as the substrate. Innovations were made in replacing Al with poly silicon as the gate electrode, and nitridation was introduced to improve the gate dielectric quality. Silicides have been used to decrease the series resistance of the gate conductor. High- $\kappa$  dielectrics have now replaced SiO<sub>2</sub> as the gate dielectric at the 45 nm technology node [5]. New gate electrodes made of alloys such as TiN, TaN etc. have been tried. Intentionally strained Si was introduced at the 90 nm technology node to improve carrier mobility in MOSFET channel.

Fig. 1.2. Quantum leap in new materials [4]. Innovations have been tried in almost every material used in fabrication of MOSFETs.

Examples of ongoing research to improve MOSFET performance include:

- Double gate: A double gate or FinFET device would provide better electrostatic control over device performance. It would provide better gate control over the channel and help minimize the off-state drain-source leakage current.

- 2) High mobility channel: High mobility substrates such as germanium and III-V materials are under consideration for the 22 nm CMOS technology node and be-yond. These materials can provide high mobility and injection velocity of carriers into the channel. They can provide high drive currents with low intrinsic delay.

- Schottky source/drain: Extrinsic resistance can be reduced with the help of Schottky Source/Drain contacts.

- 4) High- $\kappa$  gate dielectrics: Use of high- $\kappa$  gate dielectrics can reduce gate leakage

current and hence power consumption.

5) Metal gate: Gate depletion problems that occur with poly-Si gate electrodes can be solved with use of metal gates.

### ii) High-ĸ dielectrics

High- $\kappa$  dielectrics were introduced into IC's because SiO<sub>2</sub> gate dielectrics were getting thinner and thinner and reached the level where they were only a few atomic layers thick. SiO<sub>2</sub> is an excellent insulator, but at this thickness, the tunneling current through the gate electrode is significant. Therefore, a new material had to be introduced to decrease leakage. A material with higher dielectric constant has the potential to provide a higher capacitance (and thus a higher on-state current for a MOSFET), which makes a much faster switching transistor. Additionally the high- $\kappa$  dielectric can have greater thickness for a given capacitance, which helps reduce the gate leakage and thus reduce power consumption.

However, replacing SiO<sub>2</sub> with a high- $\kappa$  dielectric leads to two problems due to interaction of the high- $\kappa$  material with poly-Si gate electrodes:

- Threshold voltage pinning: defects that arise at the gate dielectric/gate electrode boundary cause the voltage at which the transistor switches to be too high.

- Phonon scattering: various scattering mechanisms associated with the gate dielectric decrease the carrier mobility.

The solution to this problem is to replace the poly-Si with metal electrodes. Specific gate metals are chosen for n-MOSFETs and p-MOSFETs, which optimize their individual performance.

5

The equivalent oxide thickness (EOT) of a high- $\kappa$  dielectric is defined as the thickness of the SiO<sub>2</sub> that provides the same capacitance as the high- $\kappa$  dielectric.

$$t_{EOT} = t_{high-k} \frac{\kappa_{SiO_2}}{\kappa_{high-k}}$$

(1)

An example of how high- $\kappa$  material helps reduce EOT is shown in Fig. 1.3. High- $\kappa$  material with greater physical thickness can provide a lower EOT than a SiO<sub>2</sub> film.

Fig. 1.3. a) Traditional MOS structure with Gate, SiO<sub>2</sub> as gate dielectric, and silicon substrate.

b) MOS structure with high-κ material as gate dielectric. (image courtesy of Intel Corp.)

The degradation of carrier mobility in the inversion layer in MOSFETs with high- $\kappa$  dielectrics is an area of active research. The high- $\kappa$  – silicon interface is not as smooth as the SiO<sub>2</sub>-silicon interface. Thus the interface and border trap densities are usually high for the high- $\kappa$  – silicon interface. This results in degraded carrier mobility in the inversion layer [6].

#### iii) Alternative Substrate MOSFETs

#### A) Ge p-MOSFETs

Various possibilities have been researched that can help enhance electron and hole mobilities, such as the use of strained silicon germanium [7] or strained Si on relaxed buffer SiGe layers [8]. However, bulk Ge has recently received renewed attention as a possible replacement for Si in high- $\kappa$  CMOS devices, because its higher electron (2.5×) and hole (4×) bulk mobility relative to that of Si allows for improved channel mobility (Fig. 1.4), while maintaining the potential to continue aggressive device scaling. The absence of a stable native oxide, which was a major problem in Ge MOS device development can now be overcome by the use of high- $\kappa$  gate dielectrics [10]-[11].  $V_{dd}$  scaling is compatible with the smaller energy band gap of Ge. The low processing temperatures used for Ge MOSFETs also may provide compatibility with 3-D IC integration. Germanium is a possible optical material as well. The smaller band-gap broadens the wavelength spectrum for opto-electronic integration to enhance CMOS functionality [12].

There are problems with fabrication of MOSFETs on Ge.  $\text{GeO}_2$ , the native gate oxide for Ge, is water soluble and volatile. However, deposited high-  $\kappa$  dielectrics provide a way to avoid this problem. The volatility of Ge surface oxides makes surface cleaning easy in preparation for deposition of high-  $\kappa$  dielectrics.

HfO<sub>2</sub> is a leading candidate for high- $\kappa$  dielectric devices, due to its higher dielectric constant and better thermal stability relative to other candidate materials. p-channel HfO<sub>2</sub>/Ge MOSFETs with EOT down to 0.85 nm, exhibiting higher hole mobility compared with HfO<sub>2</sub>/Si control samples, have been reported [13]-[14]. The interface-trap densities are higher for Si-passivated devices than GeO<sub>2</sub>-passivated devices, but im-

proved process control is achieved with the Si-passivated devices. The trap density is asymmetric in the band gap with a higher trap density (of the order of  $10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup>) near the conduction band and a lower trap density (of the order of  $10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>) near the valence band [15].

Fig. 1.4. Comparison of carrier drift velocities of Si, Ge and GaAs [9].

#### **B) III-V n-MOSFETs**

Significant improvements have been made in MOSFET performance by combining indium (In) rich InGaAs channels with high- $\kappa$  dielectrics grown by atomic layer deposition. This suggests that In-rich InGaAs would be an excellent channel material for n-MOSFETs. It can provide higher effective electron mobility, higher saturation velocity, and large on-state current, and still has a sufficiently wide enough band-gap for highspeed low-power logic applications [16]. Research on III-V MOSFETs began in 1965 when the Radio Corporation of America announced that it built the first GaAs MOSFET [17]. Even after decades of research, III-V MOSFETs were not able to provide higher drive currents than their Si counterparts. However, we have now entered the fifth era of advancement for alternative-substrate MOSFETs. These could include germanium, III-Vs, carbon nanotubes and possibly graphene [18].

Phosphides are also suitable for logic applications, whereas GaN-based MOSFETs could potentially improve the output power, dynamic swing and reliability for RF power applications. Meanwhile, GaAs-based MOSFETs promise to deliver higher mobilities and higher breakdown voltages than the silicon LDMOSFETs that are currently being employed in wireless base stations.

### iv) SiC power MOS devices

Silicon carbide (SiC) is another material system that has gained significant interest recently, although for a different application: power devices. Silicon carbide is a candidate material for high-power and high-frequency electronic devices due to its excellent thermal conductivity and high breakdown field [19]. It is preferred over other wide band gap semiconductors (such as GaN, AlGaN etc.) because SiO<sub>2</sub> can be thermally grown to form the gate oxide. In addition, SiC has excellent thermal and chemical stability, a large saturation drift velocity and high bulk electron mobility. SiC exists under stoichiometrically equivalent crystalline structures called polytypes. The 4H-SiC polytype has received more attention compared to others due to its greater band gap, combined with high and more isotropic bulk carrier mobility. Among the other SiC polytypes, cubic silicon-carbide (3C-SiC) is another promising candidate because of its compatibility with Si CMOS technology.

Historically, 4H-SiC MOSFETs suffered from low inversion channel mobilities due to extremely high interface trap densities ( $D_{it}$  close to the 4H-SiC conduction band-edge

~  $10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup>). Annealing in hydrogen, which is a key in improving the quality of the interface in SiO<sub>2</sub>/Si, is not effective in the case of SiC. Nitridation of the SiO<sub>2</sub>/SiC interface, via nitric oxide (NO) or nitrous oxide (N<sub>2</sub>O) post-oxidation annealing (POA), has emerged as the most effective solution to reduce the pre-irradiation interface trap densities [20]-[21]. Nitridation via post-oxidation annealing in nitric-oxide (NO) results in significant reduction of  $D_{it}$ , which significantly improves channel mobility. Thus, it is of interest to relate the incorporation of nitrogen to the reliability of SiC-based devices.

### A) Polytypes of SiC

Single-crystal SiC forms in the hexagonal lattice, with alternating planes of silicon and carbon atoms, as shown in Fig. 1.5 [22]. Each silicon atom bonds to four nearestneighbor carbon atoms, and each carbon atom bonds to four nearest-neighbor silicon atoms. As successive planes are added, each plane must be offset with respect to the plane below. In a polytype compound, similar sheets of atoms or symmetrical variants are stacked atop each other and related according to a symmetry operator. The differences among the polytypes arise only in the direction perpendicular to the sheets (along the caxis). In SiC, each sheet represents a bilayer composed of one layer of Si atoms and one layer of C atoms. There are a large number of possible polytypes, but the most important are 3C, 4H, and 6H. The polytypes differ in band gap energy, carrier mobility, and breakdown field.

Fig. 1.5. A close-packed hexagonal plane of spheres with centers at points marked A. A second and identical plane can be placed atop the first plane, with centers over either the points marked B or the points marked C [22].

| Property                                                  | Si  | 4H-SiC | 6H-SiC | 3C-SiC |

|-----------------------------------------------------------|-----|--------|--------|--------|

| Band gap (eV)                                             | 1.1 | 3.26   | 3.0    | 2.36   |

| Critical field (MVcm <sup>-1</sup> )                      | 0.3 | 2.0    | 2.4    | 1      |

| Electron thermal velocity                                 | 2.3 | 1.9    | 1.5    | 2.0    |

| $(10^7  {\rm cm s}^{-1})$                                 |     |        |        |        |

| Thermal conductivity (Wcm <sup>-1</sup> s <sup>-1</sup> ) | 1.5 | 4.5    | 4.5    | 4.5    |

Table I: Selected properties of Si, 4H-SiC, 6H-SiC and 3C-SiC

#### **B)** Properties of nitrided oxides on SiC

A major obstacle to the formation of a high quality oxide on SiC is the role that carbon plays during oxide growth. Thermal oxidation in a wet or dry atmosphere results in residual carbon in the oxide layer and carbon clusters at the oxide-SiC interface. It has been found that oxidation or post oxidation annealing in a nitrogen-containing atmosphere has two beneficial effects – enhanced removal of carbon, and passivation of silicon dangling bonds [23]. The most effective gases in achieving this effect are nitric oxide (NO) and nitrous oxide (N<sub>2</sub>O). This section reviews the previously published results on nitrided oxides on SiC. It was found by a number of research groups that annealing of dry oxides in NO reduces interface traps and improves oxide reliability, while similar annealing in N<sub>2</sub>O has a deleterious effect. The early results were performed on thin oxides on bulk SiC without epi-layers [24]. On the other hand, direct growth of the oxide in N<sub>2</sub>O has proven beneficial as N<sub>2</sub>O breaks down into O<sub>2</sub>, N<sub>2</sub> and NO at the oxidation temperature [25], particularly above 1200 °C. It has been proposed that, in an N<sub>2</sub>O ambient, there exist two competing processes: oxidation via O<sub>2</sub>, producing carbon buildup and nitridation via NO, assisting in carbon removal [23]. The optimum oxidation process appears to occur when the kinetics for carbon removal are just sufficient to keep pace with carbon generation, which is linked to the oxidation rate. The best results on interface quality and oxide reliability to date have been from direct oxide growth in NO, both for 6H-SiC and 4H-SiC [26]-[27]. Due to the very slow growth rate of the oxide in NO (5 hours at 1175 °C to grow 16 nm), there is sufficient time for the nitrogen to remove excess carbon. This slow growth rate and the toxic nature of 100% NO means the process may not be desirable for high volume industrial use.

With the vastly different growth kinetics of thermal oxides on SiC compared to Si, it is important to determine the amount of nitrogen and its distribution relative to the interface. Fig. 1.6 compares the SIMS profile of nitrogen and oxygen through the oxidesemiconductor interface of both Si and SiC samples nitrided in NO. The nitrogen distribution relative to the interface is exactly the same in both cases, but the percentage of N in SiC is greatly reduced [28].

Fig. 1.6. Normalized SIMS profiles of oxygen (top) and nitrogen (bottom) in nitrided oxides on Si (symbols) and SiC (lines). The nitrogen peak shape and position are the same relative to the oxygen profiles [28].

## C) SiC/SiO<sub>2</sub> interface trap spectrum

The enhanced density of electrically active imperfections at the interface between SiC and SiO<sub>2</sub> as compared to Si/SiO<sub>2</sub> is a combined result of the wider semiconductor bandgap and more numerous electrically active states. The key information is provided by the analysis of the energy (*E*) distribution of the SiC/oxide interface traps ( $D_{it}$ ) across the SiC band gap. From the  $D_{it}$  (*E*) distributions of SiC MOS structures obtained by oxidation of Si faces of the three most common SiC polytype crystals (3C-, 4H-, and 6H-, both of n-type and p-type conductivity) in dry O<sub>2</sub> [29], it is seen that for all the polytypes,  $D_{it}$  remains above 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup> over the entire SiC band gap energy range. Moreover one can notice two regions with particularly high  $D_{it}$ :

- in the lower half of the SiC band gap  $D_{ii}$  is in the range of  $10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>;

- in the vicinity of the conduction band edge, particularly in 4H-SiC,  $D_{it}$  approaches  $10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup>.

Interface-trap density depends on the SiC polytypes used in the fabrication of MOS capacitors. It is also sensitive to the crystallographic orientation of the SiC surface. The general trend is the occurrence of a higher density of traps and charges at the C-face of hexagonal SiC (6H-, 4H-polytypes) than at the Si-face [30].  $D_{it}$  also increases with increasing crystal surface misalignment angle from the (0001) plane (Si face), which is explained by a higher defect density at the SiC surfaces with orientations different from (0001) [31]. In an attempt to reduce the interface trap density, numerous annealing studies were performed during the last decade. They can be divided in three groups on the basis of the chemical mechanism behind the particular thermal treatment.

- Conventional Si technology post-oxidation anneal (POA) in non-oxidizing ambient was applied to SiC/SiO<sub>2</sub> samples to reduce the fixed charge density. In n-type 6H-SiC samples the high-temperature POA in Ar is reported to improve the interface quality significantly [32].

- Attempts to passivate defects in 6H- and 4H-SiC/SiO<sub>2</sub> samples by attaching hydrogen to them have shown that only weak improvement can be achieved by POA in H<sub>2</sub> at temperatures typical for Si (350-450 °C). With increasing temperature of the hydrogen anneal up to 1000 °C, a limited D<sub>it</sub> reduction is observed in the n-type 6H- and 4H-SiC/SiO<sub>2</sub>[34], but not in the p-type samples.

- A third group of treatments concerns direct growth or POA nitridation of oxide in nitric gases (NO, N<sub>2</sub>O, NH<sub>3</sub>). In contrast to other POA treatments, nitridation allows re-

duction of  $D_{it}$  both in the upper and lower parts of the 4H-SiC band gap, albeit to a different extent [35].

## v) Conclusions

MOS devices fabricated on alternative substrate materials, namely Ge, III-V, and SiC, have been reported in the literature. Ge and III-V substrates are important for integrated circuits, whereas SiC is interesting for power MOSFETs. This chapter lays the foundation for the research on reliability of Ge and SiC MOS done in this work.

## **CHAPTER II**

# BASICS OF TOTAL DOSE RADIATION AND BIAS TEMPERATURE INSTABILITY

# i) Radiation damage

Various system environments (e.g., space, nuclear reactors, etc.) can lead to radiation-induced degradation of electronic components. Thus it is important to understand the mechanisms responsible for degradation of electronic components. Many times, commercial off-the-shelf (COTS) parts are used in space systems because of economic considerations and ease of availability. It is extremely important to understand the underlying physics of degradation of these commercial devices. Radiation effects on semiconductor devices can be classified into 3 main categories:

- 1) Ionizing damage

- 2) Displacement damage

- 3) Single event effects

Ionizing radiation creates electron/hole pairs in the materials of interest. This radiation may be in the form of photons with energies greater than the band-gap of the material of concern, or in the form of particles such as electrons, protons, or atomic ions. Other forms of radiation damage include displacement damage from particles such as protons, neutrons, or heavy ions. Displacement damage primarily causes a reduction in minority carrier lifetime in the silicon substrate; for example, this can have an adverse effect on the gain of bipolar devices. Single event effects are produced by the interaction of a single energetic particle with a sensitive device region. The following radiation sources are used in this work:

#### 1) X-ray source

In this work, an ARACOR 4100 (Advanced Research and Applications CORporation) irradiation system is used as the source of x-rays to irradiate the devices. It generates 10 keV x-rays produced by a 60 kV, 3 kW x-ray tube. A collimator and shutter system provides a uniform 3-cm-diameter beam. The system has a radiation-tight and interlocked enclosure that provides safety to the operator during the exposure of the samples. A calibrated Si PIN diode is mounted at the sample platform level to measure the dose rate at the front surface. The dose rate can be controlled by changing the voltage and/or current setting in the XRG 3100 x-ray generator from Philips. The voltage can be changed in the range of 20 kV to 45 kV and the current can be changed in the range of 0.5 mA to 40 mA. In normal operation, the x-ray beam passes through 150 µm of Al filtering before exposing the sample to shield the low energy portion of the x-ray spectrum.

### 2) Van de Graaff proton accelerator

Particle accelerators are devices used for increasing the velocity of ions and subatomic particles such as protons, electrons, and positrons. The Van de Graaff accelerator consists of a tall metal cylinder with a hollow metal dome at its top. A silk conveyor belt runs through the middle of the cylinder. At the bottom of the cylinder, the belt collects positive charges from a high-voltage source. The positive charges ride to the top of the cylinder on the belt and are deposited on the outside of the dome at the top of the machine. The longer the belt runs, the more positive charges accumulate on the dome. At some point, the accumulation of charges on the hollow dome becomes so great that a bolt of lightning jumps from the dome to a metal rod near the machine. The bolt of lightning consists of positive charges that accumulate on the dome and are finally repelled from it. The Van de Graaff accelerator can be converted to a particle accelerator simply by attaching some kind of target to the metal rod near the machine. When the bolt of lightning strikes the metal rod, it bombards the target. The atoms of which the target is made will be broken apart by the beam of positively charged electricity.

#### A) Experimental setup for x-ray radiation

The schematic diagram of the experimental setup for x-ray radiation is shown in Fig. 2.1. Devices are placed on the chuck in the ARACOR 4100 x-ray source. The devices can be connected to the Keithley 706 scanner, which in turn is connected to a power supply, parameter analyzer, or LCR meter and GPIB box. Commands may be sent from the GPIB box to switch between different devices.

### **B)** Optimum lab source for radiation testing

Finding an optimum laboratory radiation source for testing of electron devices has been an area of active research [36]-[37]. Both laboratory Co-60 gamma and x-ray sources have been used to evaluate the radiation-hardness of electronic devices for space environments.

X-ray sources can operate at higher dose rates than most Co-60 gamma sources and can be used to irradiate individual die at the wafer level. Because of these properties, xray sources are often used for process development and control [38]. It was shown that xray irradiations more closely match proton radiation-induced degradation than Co-60 gamma irradiations. These results suggest that the best laboratory radiation source for qualification testing is a low-energy x-ray source for simulating proton-rich environments or for environments where the electron flux can be shielded. For environments and system designs where the electron flux dominates, Co-60 gamma radiation sources may still be the optimum source for device qualification [37].

Fig. 2.1. Experimental setup for x-ray radiation using ARACOR and device characterization.

### C) Total dose effects on MOS devices

A MOS device exposed to ionizing radiation typically suffers degradation in one or more of its performance parameters. MOS transistors experience a shift in threshold voltage, a decrease in mobility of charge carriers, and higher junction leakage. The damage responsible for these total dose effects occurs in the insulator layers of the circuit structures. The radiation damage in the oxide layers consists of three components:

- 1) The buildup of trapped charge in the oxide

- 2) An increase in the number of interface traps

- 3) An increase in the number of bulk oxide traps.

The basic radiation problem in a MOS transistor is illustrated in Fig. 2.2, where Fig. 2.2(a) shows the normal operation of a MOSFET. The application of an appropriate gate voltage causes a conducting channel to form between the source and drain so that current flows when the device is turned on. In Fig. 2.2(b), the effect of ionizing radiation is illustrated. Radiation-induced trapped charge has built up in the gate oxide, which causes a shift in the threshold voltage (that is, a change in the voltage which must be applied to turn the device on). If this shift is large enough, the device cannot be turned off, even at zero volts applied, and the device is said to have failed by going depletion mode.

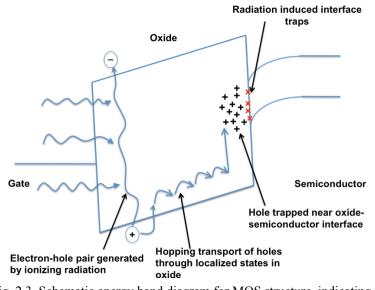

Fig. 2.3 shows a schematic energy band diagram of a MOS structure, where positive bias is applied to the gate, so that electrons flow toward the gate and holes move to the Si substrate [69]. Four major physical processes, which contribute to the radiation response of a MOS device, are also indicated. The most sensitive parts of a MOS system to radiation are the oxide insulators.

When radiation passes through a gate oxide, electron/hole pairs are created by the deposited energy. In  $SiO_2$ , the electrons are much more mobile than the holes, and they are swept out of the oxide, typically in a picosecond or less. However, in that first picosecond, some fraction of the electrons and holes will recombine. That fraction will depend greatly on the energy and type of the incident particle. The holes that escape initial recombination are relatively immobile and remain near their point of generation, where they cause a negative threshold voltage shift in a MOS transistor. These processes, electron/hole pair generation and recombination, together, are the "first process" that is depicted in Fig. 2.3.

Fig. 2.2. Schematic diagrams of n-channel MOSFETs illustrating radiation-induced charging of the gate oxide: a) normal operation and b) post-irradiation operation.

Fig. 2.3. Schematic energy band diagram for MOS structure, indicating major physical processes underlying radiation response [69].

The following types of defects have been recognized in the gate oxide in MOS devices [39]:

- 1) fixed oxide charge

- 2) mobile ionic charge

- 3) interface traps

- 4) oxide-trap charge

- 5) border traps

Oxide traps and fixed oxide charge lie within the oxide, and do not communicate with the Si [39]. Oxide trap charge is net positive charge due to trapped holes. It causes negative threshold-voltage shifts in MOSFETs and can affect the leakage current. These positive charges may be neutralized with time after radiation. Mobile ionic charges are  $Na^+$ and  $K^+$  ions that may be present in gate oxides due to human contamination. They were of significant concern two decades back, but with innovation in extremely clean fabrication facilities, these are not much of concern in state-of-the-art MOSFETs.

Interface traps are present at the oxide-semiconductor interface and can communicate with the semiconductor. They can trap both electrons and holes. Interface traps have been associated with  $P_b$  centers, which are trivalent Si defects at the Si/SiO<sub>2</sub> interface [40]. Interface traps build up slowly following radiation. Also radiation-induced oxide-trapped charge has been associated with E' centers, which are trivalent Si defects in SiO<sub>2</sub> [40]. Border traps are near-interfacial oxide traps that communicate with the Si [41]. Only studies of defect microstructure, e.g., via electron-spin-resonance, allow clear discrimination between interface traps and border traps. It is difficult to draw a clear distinction between oxide traps and border traps, as there is no particular distance where we can say that the oxide trap does not communicate with the semiconductor. MOS capacitors provide a good way to determine the border trap density from hysteresis between forward

and reverse sweep of MOS C-V characteristics [42].

Radiation induced degradation in MOSFET characteristics:

Following are the main effects of total-dose radiation on MOSFET electrical characteristics:

- 1) Threshold shift

- 2) Mobility degradation

- 3) Increase in junction leakage

- 4) Change in sub-threshold slope

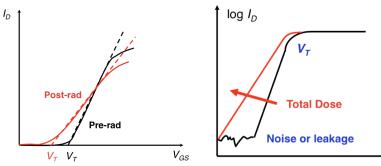

Threshold voltage shifts, changes in sub-threshold slope, and decreases in mobility are evident from the linear  $I_d$ - $V_g$  characteristics in Fig. 2.4a. The threshold voltage shift is mostly negative and is attributed to hole traps in the gate oxide. Decrease in mobility is attributed to buildup of interface traps at the gate oxide-semiconductor interface which results in increased scattering of carriers. Increase in off-state leakage is evident in the sub-threshold  $I_d$ - $V_g$  characteristics in Fig. 2.4b. This increase in off-state current can be caused by field oxides, shallow trench isolation (STI), or buried oxides in silicon-on-insulator (SOI) MOSFETs. A p-n junction leakage current has the following components [43]:

- 1) Diffusion component

- 2) Generation component

- 3) Surface generation component

The diffusion current is caused by generation in the neutral region and diffusion to the depletion region of a *pn* junction. The generation current is caused by generation in the depletion region. The surface generation current is caused by generation in the depletion

region at the Si/SiO<sub>2</sub> interface.

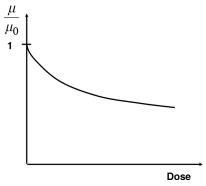

Mobility degradation in a MOSFET with total dose radiation is shown in Fig. 2.5. Degradation in mobility with dose follows the following expression [44].

$$\frac{\mu}{\mu_0} = \frac{1}{1 + \alpha_{ii}\Delta N_{ii} + \alpha_{oi}\Delta N_{oi}}$$

(2)

Here  $\Delta N_{ot}$  and  $\Delta N_{it}$  are changes in oxide-trap charge and interface-trap densities with radiation.

Fig. 2.4. a)  $I_d$ - $V_g$  characteristics showing stretch-out and mobility degradation with radiation. b) Sub-threshold  $I_d$ - $V_g$  characteristics showing increase in leakage current with radiation.

Fig. 2.5. Mobility degradation of a MOSFET as a function of radiation dose.

#### **D)** Total dose radiation in high-κ dielectric MOS devices

To continue improvement in device performance for a technology node, successful efforts have been made to replace the SiO<sub>2</sub> or nitrided SiO<sub>2</sub> as gate dielectrics in MOS-FETs with high- $\kappa$  materials. High- $\kappa$  materials such as HfO<sub>2</sub>, ZrO<sub>2</sub>, TiO<sub>2</sub> etc. can provide a much lower equivalent oxide thickness (EOT) than SiO<sub>2</sub>.

The effects of total dose radiation on silicon-based MOSFETs and MOS capacitors with high- $\kappa$  dielectrics such as Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> and ZrO<sub>2</sub> have been studied before [45]-[50]. The effects of combined x-ray radiation and bias-temperature instability on high- $\kappa$  MOS capacitors have also been studied [48].

### ii) Negative Bias Temperature Instability (NBTI)

Negative bias temperature instability has been known since at least 1966 [51]. It has become an important reliability issue in sub-micron scale silicon integrated circuits. The gate electric fields have increased as a result of scaling, IC operating temperature has increased, and surface p-channel MOSFETs have replaced buried channel devices. Also, nitrogen is routinely added to thermally grown SiO<sub>2</sub>. These factors have resulted in increased degradation of MOS devices and circuits due to bias temperature stress (BTS).

#### A) What is NBTI?

NBTI is an increase in the absolute threshold voltage and a degradation of the mobility, drain current, and transconductance of p-channel MOSFETs. It is attributed to the creation of interface traps and oxide charge by a negative gate bias at elevated temperature. The oxide electric field is usually, but not always, lower than that leading to hot carrier degradation. The oxide electric field and temperature are similar to those typically encountered during burn-in and sometimes encountered during high-performance chip operation. In terms of practical impact on MOSFETs, the greatest impact of NBTI occurs on p-MOSFETs since only those devices experience a uniform negative bias condition during typical CMOS circuit operation.

The mechanism is ascribed to breaking of Si-H bonds at the SiO<sub>2</sub>/Si substrate interface by a combination of electric field, temperature, and interactions with holes or hydrogenous species, resulting in dangling bonds or interface traps at that interface, designated as  $D_{it}$  and  $N_{it}$ , and positive oxide charge,  $N_{ot}$ , that may be due to H<sup>+</sup> or trapped holes. To simulate a NBTI condition, a negative bias is applied on the gate of a p-MOSFET with all other terminals grounded. The wafer is heated to a constant temperature (typically 125 °C). The stress is interrupted at desired intervals for device characterization. A special technique called on-the-fly NBTI characterization allows more accurate simulation of NBTI as the device is stressed at all times (even during characterization) in this technique [52]. Recovery or relaxation of NBTI has also been extensively studied recently. Under AC operating conditions, the recovery phenomenon may result in a less severe shift in device parameters [53].

#### B) NBTI models

Various NBTI models have been proposed, of which the Reaction–Diffusion (R–D) model is the most prevalent [54]-[56]. In this model, interface traps are generated at the  $SiO_2/Si$  interface (reaction) with a linear dependence on stress time. Hydrogen is released during this reaction phase. In the subsequent diffusion phase, the hydrogen diffuses from

the interface into the oxide with the time dependence  $t^n$ , where *n* for neutral hydrogen species is frequently given as 0.25. This hydrogen diffusion results in threshold voltage shifts  $\Delta V_T \sim t^n$ , often attributed entirely to the generation of interface traps. While the diffusion-limited regime has been verified many times, the reaction-limiting regime has not as frequently been observed, because it occurs during a very short time. The oxide/interface trap buildup also follows an exponential dependence on oxide field.

### C) Interface traps and oxide charges

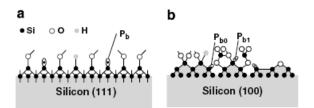

Silicon is tetrahedrally bonded with each Si atom bonded to four Si atoms in the wafer bulk. When the Si is oxidized, the bonding configuration at the surface is as shown in Fig. 2.6(a) for (111) and (b) for (100) orientation, with most Si atoms bonded to oxygen. Some Si atoms bond to hydrogen. A common type of interface trap is an interface trivalent Si atom with an unsaturated (unpaired) valence electron at the SiO<sub>2</sub>/Si interface, denoted by [57]:  $Si_3 \equiv Si$ .

Fig. 2.6 Structural model of the (a): (111)Si surface and (b): (100)Si surface [57].

The " $\equiv$ " represents three complete bonds to other Si atoms (the Si<sub>3</sub>) and the "•" represents the fourth, unpaired electron in a dangling orbital (dangling bond). Interface traps are also known as  $P_b$  centers [58]. Interface traps are described by  $D_{it}$  (cm<sup>-2</sup> eV<sup>-1</sup>),  $Q_{it}$  (C/cm<sup>2</sup>), and  $N_{it}$  (cm<sup>-2</sup>).

On (111)-oriented wafers, the  $P_b$  center is a Si<sub>3</sub> $\equiv$ Si• center, situated at the Si/SiO<sub>2</sub> interface with its unbonded central-atom orbital perpendicular to the interface, as shown in Fig. 2.6(a). On (100)Si, the four tetrahedral Si–Si directions intersect the interface plane at the same angle. Two defects, named  $P_{b1}$  and  $P_{b0}$ , have been detected by electron spin resonance (ESR). The  $P_{b1}$  center was originally thought to be a Si atom backbonded to two substrate Si atoms, with the third saturated bond attached to an oxygen atom, designated as  $Si_2O \equiv Si^{\bullet}$ . This identification was found to be incorrect, as the calculated energy levels for this defect do not agree with experiment [59]. A recent calculation suggests the  $P_{b1}$  center to be an asymmetrically oxidized dimer, with no first neighbor oxygen atoms [60]. By 1999, it was unambiguously established that both  $P_{b0}$  and  $P_{b1}$  are chemically identical to the  $P_b$  center [61]. However, there is a charge state difference between these two centers indicating  $P_{b0}$  is electrically active, while some authors believe the  $P_{b1}$  to be electrically inactive [62]. The two different effects are the result of strain relief in (100) silicon. The defects result from the naturally occurring mismatch-induced stress at the SiO<sub>2</sub>/Si interface during oxide growth. At room temperature and higher these two defects contribute to the electrical activity of total interface traps [63]. Recent ESR measurements show the  $P_{bl}$  center to be electrically active with two distinct, narrow peaks close to midgap in the silicon band gap [64]. However,  $P_{b1}$  centers are typically generated at densities considerably lower than  $P_{b0}$  centers, making them potentially less important.

Interface traps are electrically active defects with an energy distribution throughout the Si band gap. They act as generation/recombination centers and contribute to leakage current, low-frequency noise, and reduced mobility, drain current, and trans-conductance. Since electrons or holes occupy interface traps, they become charged and contribute to threshold voltage shifts. The surface potential dependence of the occupancy of interface traps is illustrated in Fig. 2.7.

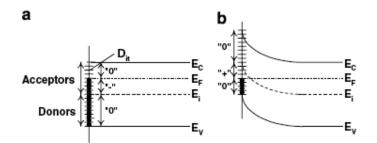

Fig. 2.7. Band diagrams of the Si substrate of a p-channel MOS device showing the occupancy of interface traps and the various charge polarities for (a) negative interface trap charge at flatband and (b) positive interface trap charge at inversion. Each of the small horizontal lines represents an interface trap. It is either occupied by an electron (solid circle) or occupied by a hole (unoccupied by an electron), shown by the lines.

Interface traps at the SiO<sub>2</sub>/Si interface are acceptor-like in the upper half and donorlike in the lower half of the band gap [65]. Hence, as shown in Fig. 2.7(a), at flatband, with electrons occupying states below the Fermi energy, the states in the lower half of the band gap are neutral (occupied donors designated by "0"). Those between midgap and the Fermi energy are negatively charged (occupied acceptors designated by "–"), and those above  $E_F$  are neutral (unoccupied acceptors). For a p-MOSFET in inversion, shown in Fig. 2.7(b), the interface traps between mid gap and the Fermi level are now unoccupied donors, leading to positively charged interface traps (designated by "+"). Hence interface traps in p-channel devices in inversion are positively charged, leading to negative threshold voltage shifts. Negative bias stress generates donor states in the lower half of the band gap [65].

The oxide charge that contributes to NBTI is not well understood. Oxide charge can consist of various entities, including mobile charge (e.g., Na, K, and Li ions), oxide

trapped charge (e.g., electrons and/or holes), and fixed charge. We exclude mobile charge, because NBTI is observed when there is no mobile charge. Oxide charge is located within the oxide and may communicate with the Si conduction and valence bands and it is positive. Some believe the trapped charge is  $H^+$  trapped in the oxide near the SiO<sub>2</sub>/Si interface. However, it is generally believed that hole trapping is the dominant mechanism and that the hole traps or their precursors may exist in the insulator prior to the stress.

The traps are positively charged when occupied by holes and neutral when unoccupied. It is possible that such positively charged traps can be neutralized by electrons when the n-substrate is at flatband and in accumulation. Similar traps have been proposed to be responsible for low frequency (1/*f*) noise where electrons or holes tunnel into traps [67]. The trap distance from the SiO<sub>2</sub>/Si interface determines the tunneling time and hence the 1/*f* noise frequency response. Typical trap distances are 1–2 nm. The range 0.9–1.75 nm covers the frequency range  $1-10^4$  Hz where 10 Hz corresponds to 2 nm distance. If carriers can tunnel over this frequency range, this would correspond to tunnel times of  $10^{-4}$ –1 s, which suggests that the positive charge can be discharged in very short times, consistent with NBTI experiments. Oxide charge located closer to the oxide/substrate interface leads to higher threshold voltage shifts than charge near the gate/oxide interface. It is rarely pointed out that charge build-up in the oxide also alters the oxide electric field. Depending on the charges and their location, the oxide electric field may increase or decrease locally, e.g., near the SiO<sub>2</sub>/substrate interface.

The NBTI threshold voltage change does not depend on the hole density, determined by changing the channel hole density and measuring the threshold voltage change. The hole density can be changed by changing  $V_T$  through fabrication or substrate bias. When this was done, there was very little change in interface trap generation, indicating that hole density is a secondary effect [68]. However, it appears that holes are required for NBTI degradation.

The p-MOSFET threshold voltage is:

$$V_{T} = \phi_{MS} - \frac{Q_{ot}}{C_{ox}} - \frac{Q_{it}(2\phi_{F})}{C_{ox}} - 2\phi_{F} - \frac{Q_{S}}{C_{ox}}$$

(3)

where  $\phi_{MS}$  is the work function difference between the gate and substrate,  $\phi_F$  the Fermi potential,  $Q_{ot}$  the positive oxide charge density (projected to the oxide-semiconductor interface),  $Q_S$  the semiconductor charge density, and  $C_{ox}$  the oxide capacitance/unit area.  $Q_{it}$  is given by

$$Q_{it} = q D_{it} \Delta E = q N_{it} \tag{4}$$

where  $\Delta E$  is the energy range over which interface traps are active.  $Q_{it}$  may be positive or negative (Fig. 7). Since neither gate nor substrate doping density nor oxide thickness change during stress, the threshold voltage change is due to changes in  $Q_{ox}$  and  $Q_{it}$  as

$$\Delta V_T = -\frac{\Delta Q_{ox} + \Delta Q_{it}}{C_{ox}} = -\frac{q(\Delta N_{ox} + \Delta N_{it})}{C_{ox}}$$

(5)

where q is the electron charge,  $C_{ox}$  is the oxide capacitance,  $N_{it}$  is the density of charged interface traps,  $N_{ox}$  is the density if oxide traps.

In today's ICs,  $N_{ox}$  and  $N_{it}$  are approximately  $10^{10}$  cm<sup>-2</sup> or slightly less before stress. Typical  $\Delta V_T$  is on the order of -10 mV, leading to  $\Delta N_{ox} + \Delta N_{it} \approx 10^{11}$  cm<sup>-2</sup> for  $t_{ox} = 2$  nm, showing the NBTI-generated charges/states are typically higher than the starting values. How many SiH bonds are there to be dissociated? After Si oxidation,  $N_{it} = 10^{12} - 10^{13}$  cm<sup>-2</sup> which is reduced to approximately  $10^{10}$  cm<sup>-2</sup> after low-temperature forming gas annealing. This suggests that  $\Delta V_T$  may approach -100 mV or higher after prolonged stress before the  $10^{12}$ – $10^{13}$  cm<sup>-2</sup> Si-H bonds are broken.

## **CHAPTER III**

# **RADIATION EFFECTS ON GERMANIUM P-MOSFETS-PART I: BASIC MECHANISMS**

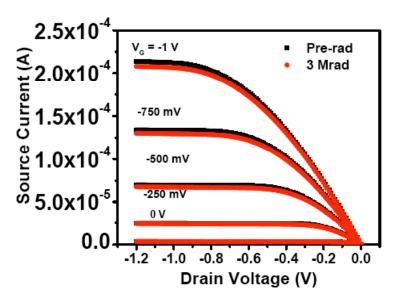

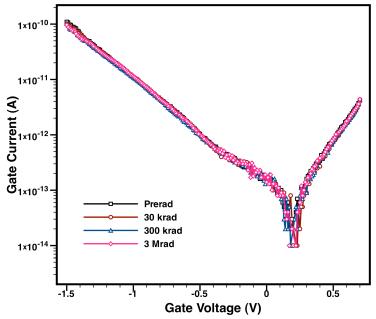

In this chapter we describe the 10 keV-x-ray radiation response of Ge p-MOSFETs with a standard process. We consider long channel length (W/L= 9.8µm/10µm) devices. The results of total ionizing dose irradiation on p-channel depletion mode MOSFETs fabricated on Ge-on-Si substrates with a TiN/TaN/HfO<sub>2</sub> gate stack are reported. There is no significant change observed in gate leakage current, threshold voltage, or transconductance at the maximum total dose of 3 Mrad(SiO<sub>2</sub>), but there is a reduction in the on/off current ratio of the devices as the total dose increases. This reduction is due to an increase in drain-substrate junction leakage current, which is dominated by an increase in surface generation current.

Total ionizing dose (TID) effects on Ge MOSFETs have not been extensively studied, in contrast to the numerous studies of radiation effects on SiO<sub>2</sub>-based Si MOSFETs that have been reported [69]-[70]. A few reports on TID-induced parametric degradation in ultra thin HfO<sub>2</sub>-based Si MOSFETs are available and radiation-induced shifts in the threshold voltage have been reported [71]. When TID effects on HfO<sub>2</sub>/Dy<sub>2</sub>O<sub>3</sub> gate stacks on Ge substrates were examined [72], very little degradation was reported.

This work investigates the radiation response of p-channel MOSFETs fabricated on Ge-on-Si substrates with a TiN/TaN/HfO<sub>2</sub> gate stack. The effects of ionizing radiation on gate leakage currents, transconductance, on/off current ratio, and threshold voltage shift are reported. Reduction in the on/off current ratio is identified as the most serious radia-

tion-effects challenge for application of these devices in ionizing radiation environments. This reduction of on/off current ratio is primarily due to an increase in drain-substrate junction leakage current.

## *i) Experimental Details*

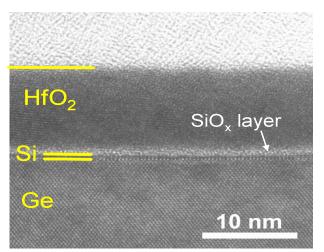

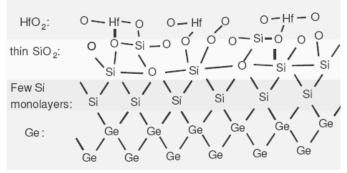

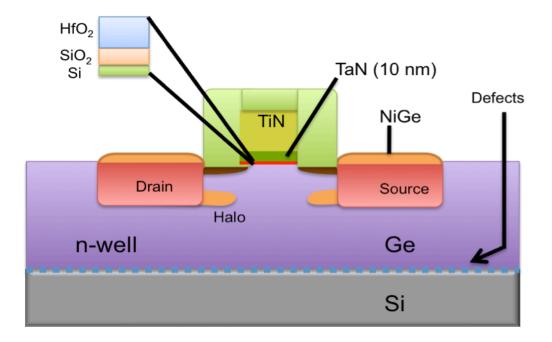

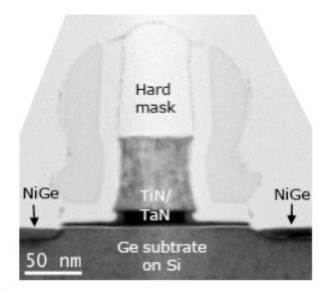

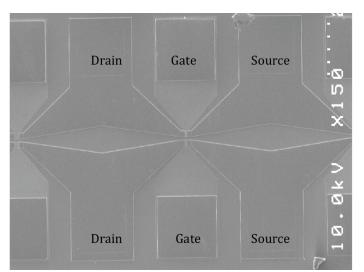

The devices studied are Ge-on-Si substrate pMOS transistors with HfO2 gate dielectrics. The substrates have been prepared by growing 2-µm epitaxial Ge films on Si substrates by reduced pressure chemical vapor deposition (RP-CVD). The threading dislocation density of the relaxed Ge epi layer is in the range of  $10^8$  cm<sup>-2</sup>. Active areas have been defined in a SiO<sub>2</sub> layer deposited on the Ge-on-Si substrates. The gate deposition sequence starts with the Ge surface passivation using a thin (4-8 monolayers) epitaxial Si layer that is partially oxidized. This passivation layer is immediately capped by 4 nm of atomic layer deposited (ALD) HfO<sub>2</sub>, followed by 10 nm of TaN and 80 nm of TiN, deposited by physical vapor deposition (PVD). A TEM picture of the gate dielectric is given in Fig. 3.1. The bonding arrangement at the oxide-semiconductor interface is shown in Fig. 3.2. After the dry etch of the gate stack, a halo P implantation of 60 keV 4  $\times 10^{13}$  cm<sup>-2</sup> was performed. The p<sup>+</sup> regions received an extension implant of 11 keV BF<sub>2</sub> at  $8 \times 10^{14}$  cm<sup>-2</sup> and a highly doped drain (HDD) implant of 7.5 keV B to a dose of 4  $\times 10^{15}$  cm<sup>-2</sup>, which was preceded by a Ge<sup>+</sup> preamorphization implantation. This places the junction at a depth of  $\sim 80$  nm below the surface. Doping activation was conducted at 500 °C for 5 min in a nitrogen ambient environment. Self-aligned nickel germanide (NiGe) was used for contacting the source, drain and gate. The EOT value of the gate dielectric is 1.2 nm. The W/L ratio of the devices studied is 9.8µm /10µm. The schematic diagram of the device cross-section is shown in Fig. 3.3. The TEM cross-section of a 65-nm gate length Ge p-MOSFET is shown in Fig. 3.4. The devices were exposed to 10 keV x-rays in an ARACOR irradiator with the gate biased at 1.3 V (positive gate bias is anticipated to be the worst bias case condition) and the other terminals grounded. The bias voltage was applied by an HP 4156A semiconductor parameter analyzer, which also was used for electrical characterization. The samples were irradiated to a cumulative dose of 3 Mrad(SiO<sub>2</sub>) at a dose rate of 31.5 krad(SiO<sub>2</sub>)/min. The arrangement of the MOSFETs on the die is shown in the SEM image in Fig. 3.5.

Fig. 3.1. TEM cross-section of the Ge p-MOSFET gate oxide-semiconductor interface.

Fig. 3.2 shows the representation of the germanium –gate oxide interface.

Fig. 3.3 Schematic cross-section of the Ge p-MOSFET.

Fig. 3.4 TEM cross-section of a 65 nm Ge p-MOSFET [13].

Fig. 3.5. SEM top view of the contact pads of a MOSFET.